# CHAPTER ONE

# **Circuit and System Fundamentals**

## Dr. John Choma

Professor & Chair Department of Electrical Engineering-Electrophysics

University of Southern California University Park: Mail Code: 0271 Los Angeles, California 90089-0271

> 213–740–4692 [USC Office] 213–740–8677 [USC Fax] johnc@almaak.usc.edu

# Dr. Wai-Kai Chen

International Technological University

### **1.1.0. INTRODUCTION**

The formulation of meaningful analytical procedures and design strategies for even the most advanced of electronic feedback circuits and systems relies on a thorough grasp of basic circuit and system concepts. Aside from abilities to apply and interpret the Kirchhoff voltage and current laws (KVL and KCL) in both the time and frequency domains, at least three issues underpin the mission of acquiring design-oriented analytical proficiency in the electronic circuits arena. The first of these is the theorems attributed to Thévenin and Norton. An ability to apply these theorems to the problems of exploring and understanding the electrical dynamics of electronic networks that couple specified signal sources to an arbitrary linear or nonlinear load is a virtual cornerstone of the electronic networks discipline. For example, Thévenin's and Norton's theorems might be gainfully applied to deduce the desired input/output (I/O) electrical characteristics of a preamplifier designed for insertion between the output terminals of a compact disc player and the input terminals of the power amplifier used to drive the audio speakers of a stereo system.

A second issue embraces transfer functions of linear networks. The capability of deducing the transfer characteristic and casting it into appropriate mathematical form serve a multitude of purposes. Included among these purposes are a delineation of the input to output gain of the network undergoing investigation, the determination of the network input and output impedances, an assessment of the relative stability of the system, and the determination of the time domain response of the subject circuit to specified transient and steady state input excitations. Phasor analyses in the sinusoidal steady state, which is fundamental to a stipulation of the manner in which the system gain and pertinent impedance levels depend on the frequency of the applied input signal, are intimately linked to network transfer functions. Phasors comprise the basis for deducing such electronic circuits and systems performance metrics as bandwidth, impedances, frequency response, and phase response. The bandwidth defines the frequency interval over which the I/O gain is maintained nominally constant. The impedance levels at the input and output terminals of an active network are instrumental in determining whether an amplifier is more suitable for voltage than for current amplification. The frequency response is essentially a mathematical snapshot of the manner in which the network under consideration performs over specified intervals of signal frequency. Finally, the phase response establishes the network delay, which defines the average time required by a system to process and ultimately deliver the desired steady state output response to a specified input signal.

The third issue is the intelligent use of the four types of dependent generators; namely, the voltage controlled current source (VCCS), the voltage controlled voltage source (VCVS), the current controlled current source (CCCS), and the current controlled voltage source (CCVS). Understanding the volt-ampere properties of these mathematical circuit branch elements is a pre-requisite to formulating reasonably accurate, design-oriented, linearized circuit models for active devices, such as the metal-oxide-semiconductor field-effect transistor (MOSFET), the bipolar junction transistor (BJT), and the PN junction diode. Moreover, the facility to exploit these properties prudently and creatively is fundamental to the intelligent application of Thévenin's and Norton's theorems and to the efficient deduction of the transfer characteristics of electronic systems.

In an attempt to vector the interested reader on a path toward ultimate electronic circuit design proficiency, the foregoing and a few related other concepts indigenous to basic circuit theory are reviewed and exemplified in this chapter. These reviews and illustrations serve to

introduce the reader to an interesting and even perplexing paradox that underpins the genuinely difficult task (some might even argue art) of creative and innovative electronic circuit and system design. In particular, the fundamental purpose of circuit analysis is not the precise disclosure of either a circuit response or a specific circuit performance metric. Instead, analyses are conducted to gain an insightful understanding of the limitations and attributes of the time and frequency domain electrical dynamics pervasive of a circuit architecture deemed plausible for the design mission. As such, these design-oriented analyses respond to the time-honored adage that nothing should ever be built until that which is to be built is thoroughly understood.

Design-oriented engineering analysis is not a trivial undertaking because design itself is neither trivial nor straightforward. Design is a challenging undertaking because it is not the problem of finding the N solutions to a system of N equations in N unknowns. The most typical design problem is one in which there are more specifications that must be satisfied or more variables that need to be determined than there are independent equations that can be written. Basic algebra teaches that a problem for which the number of unknowns does not match the number of available independent equations has no unique solution. Since poorly structured mathematical problems are implicit to virtually all design environments, unique design solutions rarely prevail. Nevertheless, viable and even creative solutions can be determined. The best of these solutions, in the sense of yielding reliable, manufacturable, and cost effective electronic networks that meet operating specifications, are rarely forged by trial and error strategies. Instead, optimal solutions derive from fundamental phenomenological understanding. The task necessarily preceding such understanding is the conduct of thorough mathematical and computer-based analyses that insightfully highlight both the attributes and the limitations of the circuit and system architectures under consideration. The satisfying understanding that supports the completion of a design project ensues when analytical disclosures can be creatively interpreted and lucidly explained in terms of fundamental physical laws, basic circuit and system theories, and simple mathematical models.

## **1.2.0. THÉVENIN'S AND NORTON'S THEOREMS**

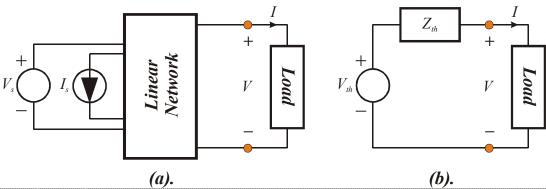

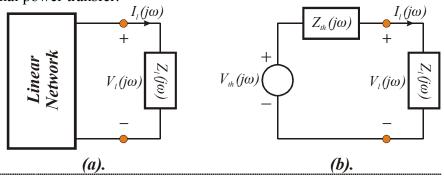

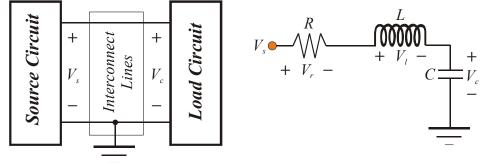

Consider the system in Figure (1.1a), which abstracts two terminals of a generalized linear network coupled to a load branch. Since the subject network is stipulated as a linear entity, its intrinsic branch elements are exclusively linear resistors, linear capacitors, linear inductors, and linear controlled voltage and current sources. Although no sources of energy are presumed embedded in the structure, any number of independent energy sources can be applied. To this end and without loss of generality, two independent inputs -a voltage source,  $V_s$ , and a current source,  $I_s$ , – are depicted. It should be understood that the presumption of no intrinsic energy sources implies at least one of three possible operational circumstances. In particular, the internal capacitors and inductors may have zero initial voltages and currents, respectively, at the time at which the indicated input sources,  $V_s$ , and  $I_s$ , are applied. Alternatively, it may be that analytical interest focuses on only the steady state performance of the system. Accordingly, the effects of initial capacitive and inductive energies have dissipated and no longer possess engineering significance. A third possibility is that initial capacitor voltages and inductor currents are treated as additional independently applied input excitations, similar to the signal sources,  $V_s$ , and  $I_s$ . In the present circumstance, it is tacitly assumed that analytical attention focuses exclusively on steady state electrical characteristics.

Thévenin's theorem states that the electrical characteristics at any port (or terminal pair) of a linear electrical network can be modeled by a voltage source in series with an impedance, as suggested by Figure (1.1b). The indicated voltage source,  $V_{th}$ , is termed the **Thévenin** voltage of the port undergoing scrutiny, while the subject series impedance,  $Z_{th}$ , is known as the **Thévenin impedance** of said port. If the port at which Thévenin's theorem is applied happens to be the output port of the network where signal responses to applied input excitations are to be delivered, the Thévenin impedance is also known as the network output impedance. When  $V_{th}$  and  $Z_{th}$  are correctly measured or calculated, the Thévenin equivalent circuit, or Thévenin model, "seen" by the load establishes a load voltage, V, and a load current, I, that are respectively identical to the load voltage and current supported by the original system in Figure (1.1a). It is important to underscore the fact that the foregoing assertions are independent of the nature of the load connected to the network port undergoing a Thévenin investigation. This is to say that the load at hand can be a passive, an active, a linear, or even a nonlinear electrical branch.

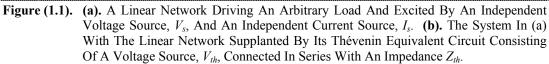

An alternative to Thévenin's theorem is Norton's theorem, which stipulates that any port of a linear electrical network can be represented as a current source in shunt with an impedance, as suggested by Figure (1.2). The current source,  $I_n$ , is termed the *Norton current* of the port undergoing scrutiny. The associated shunt impedance, which can be termed the *Norton impedance*, is, at risk of deflating Norton's ego, identical to the Thévenin impedance introduced in Figure (1.1b).

**Figure (1.2).** The Norton Equivalent Circuit For The System Given In Figure (1.1a). As In The Case Of The Thévenin Model In Figure (1.1b), The Norton Circuit Delivers A Load Voltage, *V*, And A Load Current, *I*, That Are Respectively Identical To the Load Voltage And Load Current Observed In The Original System.

The topological simplicity of both the Thévenin and Norton models obscures their actual significance and engineering utility. An initial appreciation of these models can be garnered from the realization that the linear networks they represent can be large, intricate circuits comprised of hundreds thousands of interconnected electrical branch elements. But architectural complexity notwithstanding, only two elements -voltage source and impedance in the case of Thévenin and current source and impedance in the case of Norton- are required for the unique determination of the voltage and corresponding current associated with an appended load. In short, it is likely easier to analyze the model in either Figure (1.1b) or in Figure (1.2) than it is to analyze the entire electrical system abstracted in Figure (1.1a). The downside to this Thévenin or Norton analytical tack is that the replacement of the original system by either of the models shown in Figures (1.1b) or (1.2) leads to an irretrievable loss of branch voltage, branch current, and branch power information within the linear network. In most electronic circuit and system applications, this loss of information is an acceptable consequence of the expediency with which the load voltage, current, and power can be determined in terms of Thévenin or Norton parameters. In a few cases, such loss of information may prove unacceptable. For example, in some design environments, it may be essential to understand how nonzero network element tolerances or other manufacturing uncertainties deleteriously affect the ability of a linear network to establish and sustain required load voltage and current characteristics.

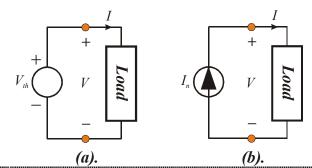

The Thévenin and Norton equivalent circuits are two distinctly different circuit topologies that serve to model any considered linear electrical system. Questions therefore naturally arise as to why two modeling approaches need be advanced when one model appears to suffice. To be sure, either a Thévenin or a Norton representation can be used to model a port of any linear network. Given the widespread analytical comfort levels associated with voltage sources, it is hardly surprising that the Thévenin equivalent circuit enjoys wider popularity than does its Norton counterpart. But in fact, some network ports are more amenable to Thévenin modeling, while others are more appropriate to Norton modeling. In idealized operating circumstances, it is even possible to encounter a network port for which Thévenin parameters can be calculated or measured, but Norton parameters are not deterministic, and vice versa. For example, and as is demonstrated in the following subsection of material, the Norton current is indeterminate for a network port whose Thévenin impedance is zero. In this case, only a Thévenin equivalent circuit can be meaningfully contrived and, as Figure (1.3a) illustrates, the subject network port emulates the volt-ampere characteristics of an ideal voltage source. On the other hand, the Thévenin voltage of a network port having infinitely large Thévenin impedance cannot be determined, which accordingly forces a Norton representation of said port. In this case, the network port at hand behaves as the ideal current source depicted in Figure (1.3b). A general extrapolation of the foregoing two statements is that a network port characterized by a small Thévenin impedance behaves as an approximate ideal voltage source and is therefore prudently modeled by a Thévenin equivalent circuit. On the other hand, a linear network port that emulates idealized current source characteristics by virtue of its large Thévenin impedance is best represented by a Norton equivalent circuit.

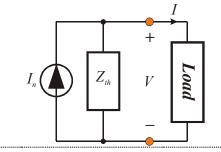

Figure (1.3). (a). The Thévenin Equivalent Circuit Of A Loaded Linear Network Port Whose Thévenin Port Impedance Is Zero. The Port In Question Behaves As An Ideal Voltage Source. (b). The Norton Equivalent Circuit Of A Loaded Linear Network Port Whose Thévenin Port Impedance Is Infinitely Large. The Port In Question Behaves As An Ideal Current Source.

#### **1.2.1. THÉVENIN AND NORTON PARAMETERS**

The experimental determination or analytical evaluation of the Thévenin parameters commences by noting in Figure (1.1b) that the load voltage, V, is

$$V = V_{th} - Z_{th}I, \qquad (1-1)$$

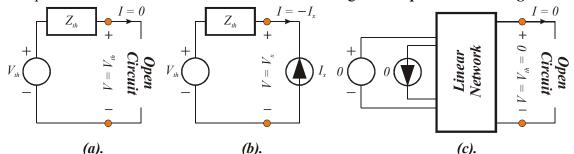

where *I* is obviously the current supplied by the network and conducted by the load connecting to, or terminating, the network port undergoing scrutiny. The fact that the Thévenin equivalent circuit is independent of the nature of the load encourages the exploitation of specific loads that facilitate the direct determination of the Thévenin voltage,  $V_{th}$ . To this end, if the actual load were to be supplanted by an open circuit, as shown in Figure (1.4a), current *I* is necessarily reduced to zero, which renders  $V \equiv V_{th}$  in (1-1). In other words, the Thévenin voltage of a linear network port is the voltage established at that port when said port is open circuited. This observation explains the common reference to a Thévenin voltage as an *open circuit voltage*.

Consider now the case in which the original load is replaced by an ideal current source of value  $I_x$ , as is depicted in Figure (1.4b). The resultant network current is  $I = -I_x$ , and if  $V_x$  denotes the value of port voltage V corresponding to the applied current load, (1-1) delivers

$$\frac{V_x}{I_x} = Z_{th} + \frac{V_{th}}{I_x}, \qquad (1-2)$$

where it is important to note that voltage  $V_x$  is in disassociated polarity reference to current  $I_x$ . It would be delightful if  $V_{th}$  could be constrained to zero under the stipulated load current source constraint. In this event, the ratio of the current source voltage,  $V_x$ , -to- the current source current,  $I_x$ , is the Thévenin impedance,  $Z_{th}$ , in need of evaluation. The strategy for effecting null  $V_{th}$ in a physically sound sense derives from classic **superposition theory**, which applies to all linear networks. In particular, recall from Figure (1.1a) that the network undergoing study is excited by two sources of independent energy; namely, voltage  $V_s$  and current  $I_s$ . Superposition theory states that any branch voltage or any branch current of any linear electrical system, which certainly embraces a linear network under the condition of a linear load termination that happens to be a constant current source, is the algebraic superposition of the effects of all applied independent sources of voltage and current. It follows that

$$V_{th} = A_{st}V_s + Z_{st}I_s , \qquad (1-3)$$

where  $A_{st}$  and  $Z_{st}$  are understood to be constants (perhaps frequency dependent constants), independent of  $V_s$  and  $I_s$ . Obviously,  $V_{th}$  is zero if the applied signal energies are nulled, as is highlighted in the abstraction of Figure (1.4c). Thus, the Thévenin impedance at a network port can be determined as the ratio of a voltage,  $V_x$ , established in response to an applied load current,  $I_x$ , - to- $I_x$ , under the special circumstance of all independently applied signal sources set to zero.

The procedure advanced for Thévenin impedance calculation effectively mirrors the operation of an ohmmeter used to measure the resistance between two electrical terminals. It might therefore be termed the **ohmmeter method** of impedance computation. At risk of inadvertently depressing the reader, there is no such beast as an ohmmeter. The ohmmeters commonly found in the laboratory are actually electronic systems that perform two functions when its leads are connected to a terminal pair of interest. The first function is the injection of a current  $(I_x)$  that is sufficiently small to preclude any significant electrical perturbation of the network undergoing characterization. In strictly linear networks, such as those considered in this discussion, superposition renders the actual value of  $I_x$  immaterial. In nonlinear structures, such as transistors or batteries, the value of  $I_x$  is so crucial as to render a conventional ohmmeter ineffective for resistance evaluation. The second function performed by the ohmmeter is the monitoring of the resultant voltage  $(V_x)$  established at the port to which the current is applied. The reading observed on the ohmmeter is actually this voltage scaled to the applied current  $(V_x/I_x)$  and hence, it is the resistance evidenced at the port in question.

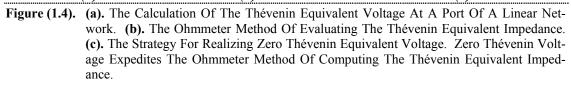

The determination of the Norton current,  $I_n$ , like the evaluation of the Thévenin voltage, relies on the fundamental fact that the parameters of the Norton equivalent circuit are independent of the load termination. If, therefore, the load appearing in Figure (1.2) is replaced by an electrical short circuit, as indicated in Figure (1.5), it is clear the that resultant current, I, flowing through the short circuited load is identical to  $I_n$ . It follows that in general, the Norton current of linear network port is the current supplied by that port to a short-circuited termination. Not surprisingly, the Norton current is often referred to as a *short circuit current*. And like  $V_{th}$ ,  $I_n$  is the superposition of the effects of the applied input signal energies. With reference to Figure (1.1a),

$$I_n = Y_{sn}V_s + A_{sn}I_s , \qquad (1-4)$$

where  $Y_{sn}$  and  $A_{sn}$  are constants that are independent of applied signal voltage,  $V_s$ , and applied signal current,  $I_s$ .

#### **1.2.2. ENGINEERING OBSERVATIONS**

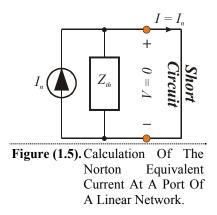

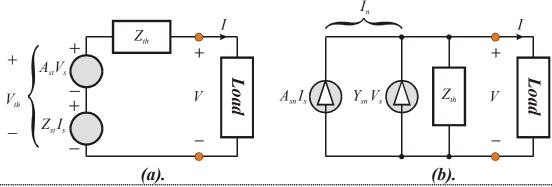

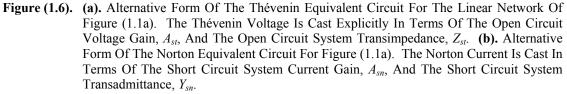

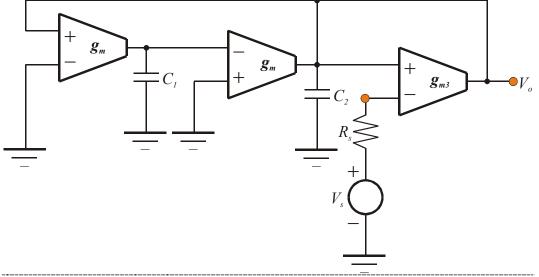

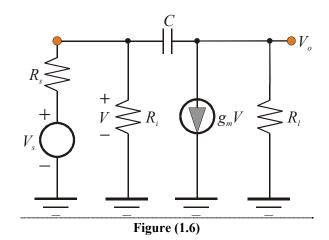

Three useful and interesting sidebars ensue from the foregoing considerations. The first and most obvious of these is that the Thévenin equivalent circuit of the system in Figure (1.1a) can, by virtue of Figure (1.1b) and (1-3), be drawn in the topological format of Figure (1.6a). In this diagram, parameter  $A_{st}$  is a dimensionless parameter that represents the voltage transfer function, or voltage gain, from the port at which  $V_s$  is incident -to- the port that is terminated in the considered load. As such, Ast might logically be termed the system Thévenin voltage gain or equivalently, the system *open circuit voltage gain*. On the other hand, parameter  $Z_{st}$  has units of ohms and is the *Thévenin transimpedance*, or *open circuit transimpedance*, evidenced between the port at which signal current  $I_s$  is applied and the load port. In other words, the transimpedance, like any impedance function, is a voltage -to- current ratio; it is literally the transfer impedance measured from the port of source current application -to- the load voltage response. A second, related observation is that because of (1-4), the Norton equivalent circuit in Figure (1.2) can be delineated as the structure offered in Figure (1.6b). In this case, parameter  $A_{sn}$  is dimensionless and symbolizes the Norton current gain, or short circuit current gain, between the applied signal source current,  $I_s$ , and the load port at which voltage V is established. On the other hand, Y<sub>sn</sub>, which has units of mhos, is the Norton transadmittance, or short circuit trans*fer admittance*, from the port at which signal voltage  $V_s$  is applied and the load port that conducts current I. Collectively, both of the models in Figure (1.6) underscore the fact that the Thévenin voltage and Norton current at a network port are respectively the superimposed effects of the energy sources applied to the network undergoing examination. They also highlight the various transfer relationships that link the Thévenin load voltage and the Norton load current to input signal energies.

The third observation derives from the explicit requirement that the Thévenin and Norton equivalent circuits applied to a given network port must each produce identical load voltage and current results under actual load termination conditions. In other words, one engineer using the Thévenin model and another using the Norton equivalent circuit must each compute the same load voltage and current responses. This necessity means that the Thévenin voltage,  $V_{th}$ , and the Norton current,  $I_n$ , are not independent variables. In order to arrive at the relationship between  $V_{th}$  and  $I_n$ , consider the model in Figure (1.1b) under the special circumstance of a short-circuited load, as depicted in Figure (1.7a). By definition, the resultant load current, I, is the short circuit, or Norton load current,  $I_n$ , which is

**Figure (1.7).** (a). The Thévenin Equivalent Circuit Of A Linear Network Port Terminated In A Short Circuited Load. (b). The Norton Equivalent Circuit Of A Linear Network Port That Is Open Circuited.

$$I \equiv I_n = \frac{V_{th}}{Z_{th}}.$$

(1-5)

This elegantly simple result shows that the Norton current at a port of a linear electrical network is nothing more than the ratio of the Thévenin voltage -to- the Thévenin impedance at said port. The application of the Norton model in Figure (1.2) to the special case of an open circuited load shown in Figure (1.7b) delivers a consistent result. Specifically, the open circuit load voltage V, which is now identical to the Thévenin voltage,  $V_{th}$ , "seen" by the load, is

$$V_{th} = Z_{th}I_n , \qquad (1-6)$$

for which an understanding with respect to (1-5) assuredly instills pride in your high school algebra teachers.

#### **EXAMPLE #1.1:**

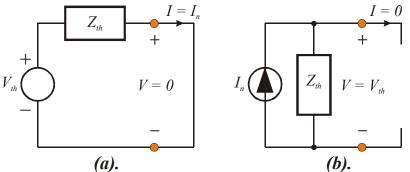

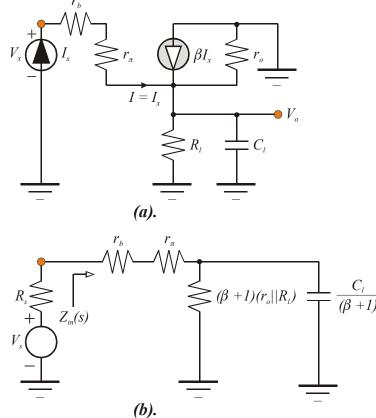

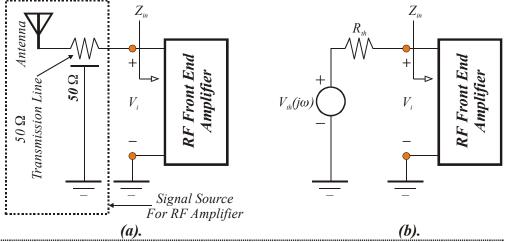

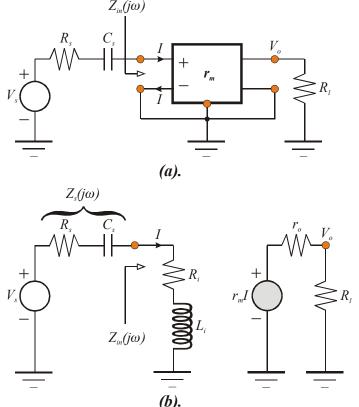

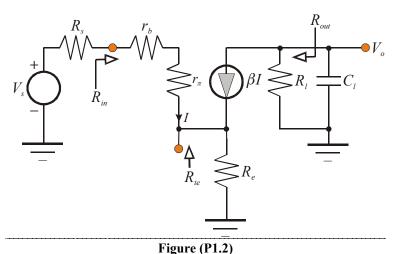

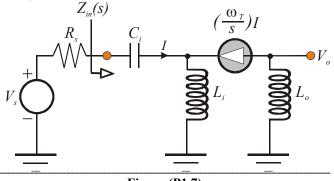

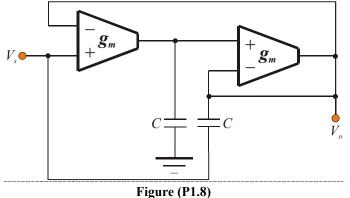

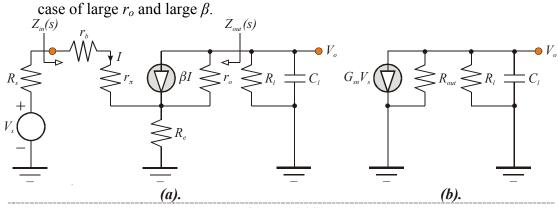

The circuit appearing in Figure (1.8) is the linearized model of a bipolar junction transistor (BJT) voltage buffer, which is otherwise known as an emitter follower. The applied signal source is represented as a Thévenin equivalent circuit consisting of the series interconnection of a signal voltage,  $V_s$ , and a signal source

resistance,  $R_s$ . The output signal voltage is  $V_o$ , which is taken as the voltage developed across a load capacitance of value  $C_l$ . Determine expressions for the Thévenin voltage,  $V_{th}$ , seen by the capacitive load, the Thévenin resistance,  $R_{th}$ , facing this load, and the transfer function,  $A_v(s) = V_o(s)/V_s(s)$ . As a demonstration of the utility of the Thévenin analytical approach to evaluating the performance of an electronic network, examine the voltage transfer function from the perspective of determining the 3-dB bandwidth,  $\omega_b$ , and plotting the frequency response of the amplifier. Numerically evaluate the Thévenin voltage gain,  $A_{st}$ , the Thévenin resistance, and the 3-dB bandwidth for transistor parameters of  $r_b = 200 \ \Omega$ ,  $r_{\pi} = 2 \ K\Omega$ ,  $r_o = 50 \ K\Omega$ , and  $\beta = 120 \ amps/amp$ . Additionally, take  $R_s = 300 \ \Omega$ ,  $R_l = 3 \ K\Omega$ , and  $C_l = 10 \ pF$ .

Figure (1.8). Linearized Model Of A Bipolar Junction Transistor Emitter Follower.

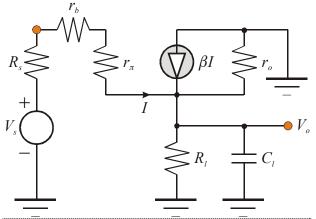

Figure (1.9). (a). Equivalent Circuit Used To Evaluate The Thévenin Voltage Seen By The Capacitance, C<sub>l</sub>, In Figure (1.8). (b). Equivalent Circuit Used To Evaluate The Thévenin Resistance Seen By The Capacitance, C<sub>l</sub>, In Figure (1.8). (c). Thévenin Equivalent Circuit Pertinent To The Output Port Of The Amplifier In Figure (1.8).

#### SOLUTION #1.1:

(1). Figure (1.9a) is the circuit diagram appropriate to the computation of the Thévenin voltage,  $V_{th}$ , established at the capacitive load port. Note in this diagram that the capacitive load branch has been removed; that is, the load has been open circuited. The resultant branch currents have been identified in this circuit diagram to appease Kirchhoff. Observe that the current, I, which controls the dependent current source,  $\beta I$ , is expressible as

$$I = \frac{V_s - V_{th}}{R_s + r_b + r_{\pi}}.$$

(E1-1)

A conventional nodal analysis then yields

$$\frac{V_{th}}{R_l} + \frac{V_{th}}{r_o} - (\beta + I)I = \frac{V_{th}}{R_l} + \frac{V_{th}}{r_o} - \frac{(\beta + I)(V_s - V_{th})}{R_s + r_b + r_\pi} = 0,$$

(E1-2)

from which the Thévenin voltage computes to be

$$V_{th} = \left[\frac{(\beta + l)(r_o ||R_l)}{R_s + r_b + r_\pi + (\beta + l)(r_o ||R_l)}\right] V_s .$$

(E1-3)

As a check on the propriety of (E1-3), note that  $\beta = 0$  in Figure (1.9a) eliminates the current controlled current source,  $\beta I$ . Since resistance  $r_o$  is clearly in parallel with resistance  $R_l$ , it is hardly surprising that (E1-3) reduces to the simple voltage divider expression,

$$V_{th} = \left[\frac{\left(r_{o} \|R_{l}\right)}{R_{s} + r_{b} + r_{\pi} + \left(r_{o} \|R_{l}\right)}\right] V_{s} .$$

(E1-4)

(2). The circuit diagram used to determine the Thévenin resistance,  $R_{th}$ , seen by the load capacitance,  $C_l$ , in Figure (1.8) is provided in Figure (1.9b), where the independent signal voltage,  $V_s$ , applied to the original circuit has been nulled. It is evident that the "ohmmeter" current,  $I_x$ , relates to the "ohmmeter voltage,"  $V_x$ , in accordance with

$$I_x = \frac{V_x}{R_l} + I_{xx} = \frac{V_x}{R_l} + \frac{V_x}{r_o} - (\beta + l)I, \qquad (E1-5)$$

where current *I* is now

$$I = -\frac{V_x}{R_s + r_b + r_{\pi}}.$$

(E1-6)

Upon combining these two relationships, the pertinent Thévenin resistance is found to be

$$R_{th} = \frac{V_x}{I_x} = \left(R_l \|r_o\right) \left\| \left(\frac{r_{\pi} + r_b + R_s}{\beta + l}\right)\right\|.$$

(E1-7)

For  $\beta = 0$ , this solution collapses to the expected result of a parallel combination of three effective circuit resistances; namely, the load resistance,  $R_l$ , the transistor model resistance,  $r_o$ , and the net resistance comprised of the series interconnection of resistances  $r_{\pi}$ ,  $r_b$ , and  $R_s$ .

(3). From the solution for the Thévenin voltage in Step (1) above, the Thévenin voltage gain,  $A_{st}$ , is

$$A_{st} = \frac{V_{th}}{V_s} = \frac{(\beta + I)(r_o ||R_l)}{R_s + r_b + r_\pi + (\beta + I)(r_o ||R_l)}.$$

(E1-8)

The resultant model for the evaluation of the overall voltage gain of the emitter follower is shown in Figure (1.9c). This simple model readily produces an overall gain expression of \_\_\_\_\_\_

$$A_{v}(s) = \frac{V_{o}(s)}{V_{s}(s)} = \frac{A_{st}(l/sC_{l})}{R_{th} + l/sC_{l}} = \frac{A_{st}}{l + sR_{th}C_{l}}.$$

(E1-9)

It is appropriate to interject that the product,  $R_{th}C_l$ , is the *time constant* attributed to the capacitance,  $C_l$ . In general, it can be stated that the time constant associated with a capacitor in a linear network is the product of said capacitance and the Thévenin resistance faced by the subject capacitor.

(4). In the laboratory, the amplifier at hand might very well be characterized under steady state sinusoidal operating conditions. With sinusoidal excitation, the steady state response derives from replacing the Laplace operator, s, in the preceding result by the imaginary frequency variable,  $j\omega$ . Thus,

$$A_{\nu}(j\omega) = \frac{V_o(j\omega)}{V_s(j\omega)} = \frac{A_{st}(l/j\omega C_l)}{R_{th} + l/j\omega C_l} = \frac{A_{st}}{l+j\omega R_{th}C_l},$$

(E1-10)

for which the magnitude of gain is

$$\left|A_{v}(j\omega)\right| = \left|\frac{V_{o}(j\omega)}{V_{s}(j\omega)}\right| = \left|\frac{A_{st}}{1+j\omega R_{th}C_{l}}\right| = \frac{\left|A_{st}\right|}{\sqrt{1+\left(\omega R_{th}C_{l}\right)^{2}}}.$$

(E1-11)

Note that for very small radial signal frequencies,  $\omega$ , the voltage transfer function is approximately constant, independent of frequency. On the other hand, large  $\omega$  incurs a reduced magnitude of transfer function and thus, a degraded gain. Indeed, infinitely large  $\omega$  results in zero gain magnitude. Such a transfer function characteristic is indicative of a *lowpass network*; that is, a network capable of passing with minimal gain reduction, or with minimal attenuation, low signal frequencies from its input -toits output port, but incapable of processing very large frequencies without substantial attenuation. Of course, the reason for this lowpass characteristic is rendered transparent by the original circuit in Figure (1.8). In particular, there is only one energy storage element –capacitor  $C_{l}$  in the subject network. At very low signal frequencies, this capacitor emulates an open circuited branch, thereby collapsing the network at hand to a purely resistive, so called *memoryless*, circuit. In a memoryless configuration, no branch element has an impedance that varies with signal frequency and accordingly, the gain of such a circuit is a constant, independent of signal frequency. At higher frequencies, the impedance of capacitor  $C_l$  decreases and in the limit of infinitely large frequency, the impedance of  $C_l$  approaches zero ohms. Since  $C_l$  is incident with the output port of the circuit, the magnitude of the output voltage,  $V_o(j\omega)$ , and thus the gain,  $V_o(j\omega)/V_s(j\omega)$ , decreases progressively toward zero for large signal frequencies.

(5). The gain expression deduced in the preceding computational step indicates that the zero frequency gain, say  $A_v(0)$ , is actually the Thévenin voltage gain,  $A_{st}$ . In the most general of circuit analyses,  $A_{st}$  is not identically equal to the zero frequency gain. It happens here that  $A_{st} \equiv A_v(0)$  only because the load, which is removed from the otherwise memoryless network in the course of delineating the Thévenin gain, happens to be a capacitor. Thus, removal of the load in this example is tantamount to a consideration of zero signal frequency effects since a capacitive impedance at zero frequency is infinitely large.

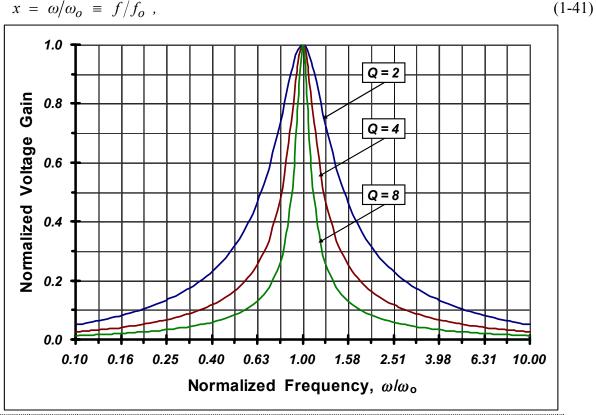

In a lowpass circuit, the 3-dB frequency,  $\omega_b$ , is the frequency at which the gain magnitude is a factor of the square root of two smaller than the magnitude of the zero frequency gain; that is,

$$|A_{\nu}(j\omega_{b})| \triangleq \frac{|A_{\nu}(0)|}{\sqrt{2}} = \frac{|A_{\nu}(0)|}{|l+j\omega_{b}R_{th}C_{l}|}.$$

(E1-12)

Evidently,

$$\omega_b = \frac{l}{R_{th}C_l} , \qquad (E1-13)$$

which is little more than the inverse time constant associated with the lone capacitive element,  $C_l$ , in the original network.

A factor of *root two* gain degradation is equivalent to a gain magnitude deterioration of *three decibels* because of the definition of a decibel. In particular, the decibel value of any positive or a negative number, X, is  $20log_{10}|X|$ . If X is root two, its decibel (or dB) value is very close to 3. It follows that

$$\begin{aligned} A_{v}(j\omega_{b}) & in \ db \ = \ 20 \log_{10} |A_{v}(j\omega_{b})| \ = \ 20 \log_{10} |A_{v}(0)| \ - \ 20 \log_{10} \sqrt{2} \\ &\approx \ 20 \log_{10} |A_{v}(0)| \ - \ 3 \ dB \ ; \end{aligned}$$

that is, the decibel value of gain is reduced from its decibel value of zero frequency gain by an amount equal to  $3 \, dB$ . Hence, the signal frequency effecting a root two gain magnitude reduction is termed the 3-dB frequency.

(6). The gain relationships in Step (4) can now be written in the forms

$$A_{v}(j\omega) = \frac{V_{o}(j\omega)}{V_{s}(j\omega)} = \frac{A_{st}}{1 + j\omega/\omega_{b}},$$

(E1-14)

and

$$\left|A_{\nu}(j\omega)\right| = \left|\frac{V_{o}(j\omega)}{V_{s}(j\omega)}\right| = \frac{\left|A_{st}\right|}{\sqrt{1 + \left(\omega/\omega_{b}\right)^{2}}}.$$

(E1-15)

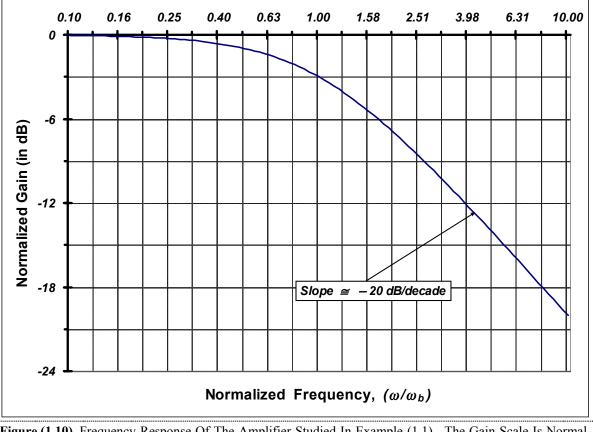

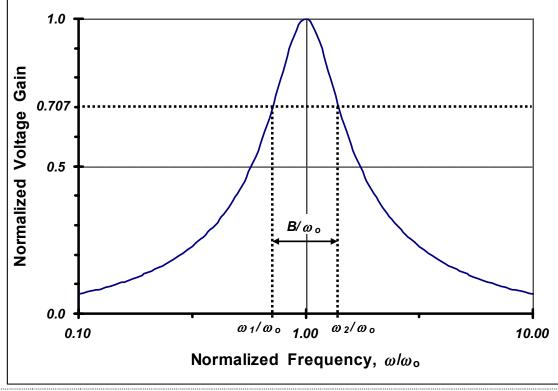

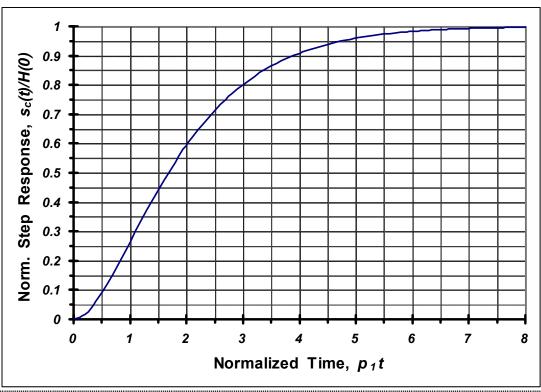

The frequency response of an amplifier is simply the plot of its gain magnitude as a function of signal frequency. For the amplifier undergoing consideration herewith, this plot appears in Figure (1.10), where the gain scale is in units of decibels and is normalized to the zero frequency gain,  $A_{st}$ . The frequency scale is normalized to the *3-dB* bandwidth,  $\omega_b$ .

The frequency response effectively pictures the ability of an amplifier to process applied input signals of varying frequencies. For example, the lowpass amplifier at hand is capable of providing an essentially constant I/O transmission over relatively low frequencies, but it is incapable of sustaining this transmission at high frequencies. To this end, the 3-dB frequency is a measure of amplifier effectiveness over frequency. To the extent that "essentially constant gain" can be viewed as a gain magnitude that is within *three decibels* of its maximum (in this case, the low frequency) gain, the 3-dB bandwidth,  $\omega_b$ , can be interpreted as the maximum frequency over which relatively constant gain is sustained. In this example, the maximum gain is actually less than one, which logically brings into question the utility of the considered amplifier. Despite this less than unity maximum gain, the buffer enjoys widespread popularity in electronic circuits and systems. More information about buffering applications is provided subsequently.

(7). For the stipulated numerical values of all device and circuit parameters, the Thévenin gain, the Thévenin voltage gain, Thévenin resistance, and *3-dB* bandwidth are

**Figure (1.10).** Frequency Response Of The Amplifier Studied In Example (1.1). The Gain Scale Is Normalized To The Zero Frequency Value, *A<sub>st</sub>*, Of Amplifier Gain.

$A_{st} = 0.993 = -0.063 \ dB$   $R_{th} = 20.51 \ \Omega$  $\omega_b = 2\pi (775.9 \ MHz) .$

In short, the buffer considered herewith establishes, within 3-dB error, almost unity voltage gain  $(0 \ dB)$  over a frequency passband extending from  $0 \ Hz$  -to- slightly under 776 *MHz*, while providing a Thévenin resistance at its output port of slightly more than 20  $\Omega$ . Because the Thévenin resistance is indeed computed at the output port of the amplifier, this resistance metric is referred to as simply the amplifier **output resistance**.

**<u>COMMENTS:</u>** The commentaries accompanying the preceding computational steps can be supplemented by the overarching observation of the profound simplicity of the Thévenin equivalent circuit. In particular, the original circuit in Figure (1.8) contains eight (8) branch elements, while its Thévenin model in Figure (1.9c) contains only three (3) elements. This simplicity fosters design-oriented insights that are not rendered immediately transparent by the original configuration. For example, to the extent that the design objective is the realization of a buffer characterized by near unity low frequency gain and very low output resistance, the results highlighted by the Thévenin model suggest that large transistor  $\beta$  is essential. Note that the output resistance clearly satisfies

$$R_{th} < \frac{r_{\pi}+r_b+R_s}{\beta+l},$$

which further dramatizes the importance of large  $\beta$ . Even the ability to achieve large *3-dB* bandwidth is seen to be strongly dependent on transistor  $\beta$ , since

$$\omega_b = \frac{l}{R_{th}C_l} \approx \frac{\beta + l}{\left(R_s + r_b + r_\pi\right)C_l}$$

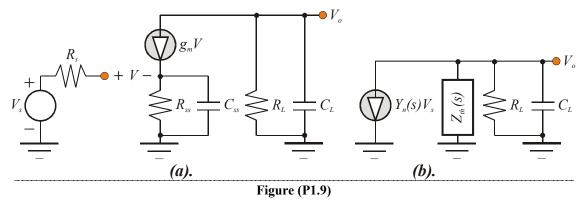

#### **EXAMPLE #1.2:**

Reconsider the circuit in Figure (1.8) from the perspective of evaluating the Thévenin equivalent circuit presented to the signal source by the input port of the amplifier. Using the parameter values provided in the preceding example, evaluate the Thévenin input impedance at zero frequency, infinitely large signal frequency, and the previously computed 3-dB frequency of the amplifier.

#### SOLUTION #1.2:

(1). Because the circuit capacitor in Figure (1.8) is presumed to have zero initial charge and because no other energy sources appear within the network to the right of the signal source, the Thévenin equivalent circuit at the amplifier input port is comprised exclusively of an impedance, say  $Z_{in}(s)$ . The pertinent model for computing this impedance appears in Figure (1.11a) and reflects the fact that the "ohmmeter" current,  $I_x$ , is identical to the current, I, that controls the dependent current source,  $\beta I$ .

Figure (1.11). (a). Circuit Model Used To Compute The Thévenin Impedance Presented To The Signal Source By The Input Port Of The Amplifier. (b). Topological Depiction Of The Thévenin Input Impedance Determined For The Equivalent Circuit In (a).

(2). Since the branch elements,  $R_b$ ,  $r_o$ , and  $C_l$  are connected in parallel with one another and since the net current flowing through this shunt interconnection is  $(\beta + 1)I = (\beta + 1)I$  $I)I_x$

$$V_{x} = (r_{b} + r_{\pi}) I_{x} + \frac{(\beta + I)(r_{o} ||R_{l}) I_{x}}{I + s(r_{o} ||R_{l}) C_{l}},$$

(E2-1)

whence

$$Z_{in}(s) = \frac{V_x}{I_x} = r_b + r_\pi + \frac{(\beta + I)(r_o ||R_l)}{I + s(r_o ||R_l)C_l}.$$

(E2-2)

This result can be rewritten in the form

$$Z_{in}(s) = r_b + r_{\pi} + \frac{(\beta + l)(r_o ||R_l)}{1 + s[(\beta + l)(r_o ||R_l)][\frac{C_l}{(\beta + l)}]},$$

(E2-3)

which suggests representing the input amplifier port by the model offered in Figure (1.11b).

Because the Thévenin impedance found above pertains to the input port of the considered amplifier, it is often referred to as the *Thévenin input impedance* or, in abridged fashion, the *input impedance* of the amplifier. Note that this input impedance is computed with the capacitive load in tack; that is, the capacitive load is not removed from the circuit, as it is in the Thévenin voltage determination. In the jargon of circuit theory, the resultant input impedance, with the actual load connected, is sometimes called the *driving point input impedance*, as opposed to the open circuit input impedance, which would be  $Z_{in}(s)$  under the condition of load removal.

(3). At zero signal frequency, the load capacitance behaves as an open circuit. More correctly, the admittance,  $sC_l$ , of the load capacitance at zero frequency is zero. From either the foregoing analytical disclosures or the representation in Figure (1.11b),

$$Z_{in}(0) = r_b + r_{\pi} + (\beta + I)(r_o ||R_l) = 344.7 \ K\Omega.$$

At infinitely large signal frequency, the load capacitance behaves as an short circuit. (4). In particular, the impedance,  $l/sC_l$ , of the load capacitance is zero at infinitely large signal frequency. From either the foregoing analytical disclosures or the representation in Figure (1.11b),

$$Z_{in}(\infty) = r_b + r_\pi = 2.20 \ K\Omega \,.$$

(5). At the 3-dB bandwidth,  $\omega_b$ , of the buffer, the driving point input impedance is

$$Z_{in}(j\omega_b) = r_b + r_\pi + \frac{(\beta + I)(r_o ||R_l)}{I + j\omega_b(r_o ||R_l)C_l}.$$

(E2-4)

From the preceding example,  $\omega_l = 2\pi(775.9 \text{ MHz})$  and accordingly.

From the preceding example,  $\omega_b = 2\pi (775.9 \text{ MHz})$  and accordingly,

$$Z_{in}(j\omega_b) = 2,200 + \frac{342.5(10^3)}{1+j138.0} \approx (2,200 - j2,482) \Omega.$$

Since the imaginary part of this impedance function is negative, the input impedance at the 3-dB bandwidth of the amplifier is noted to be capacitive.

**<u>COMMENTS:</u>** The use of Thévenin's theorem has served to highlight several important properties of a voltage buffer. The first of these properties, which derives from Example (1.1), is that the low frequency voltage transmission factor, or gain, is less than unity, but indeed, close to one. A second property is a low frequency input impedance that is significantly larger than the low frequency Thévenin output impedance. In particular, the I/O impedance transformation ratio is, from the present and preceding example,  $344.7 K\Omega/20.51 \Omega = 16.8(10^3)$ . As is illustrated shortly, this dramatic ratio boasts utility in practical electronic systems. Third, the capacitive nature of the input impedance renders a significant reduction of this impedance over signal frequency. In this example, the difference between the low frequency and very high frequency input impedances is  $344.7 K\Omega/2.20 K\Omega$ , which is better than 156.

### **1.3.0. DEPENDENT SOURCES AND AMPLIFIER CONCEPTS**

The Thévenin and Norton theorems and concepts addressed in the preceding section of material lay a foundation on which to build a fundamental understanding of general amplifiers and their respective properties. This understanding sets the stage for both open loop and closed loop electronic system design strategies by transforming the abstractness of dependent energy sources into topological tools that support design objectives. To this end, it is both instructive and interesting to be aware of the fact that there exist only four fundamental types of linear amplifiers and that these four amplifier configurations respectively emulate the four controlled sources that are an implicit part of basic circuit theory literature.

The most popular amplifying unit is the *voltage amplifier*, whose practical implementation delivers volt-ampere characteristics that emulate those of an ideal voltage controlled voltage source. The ubiquitous operational amplifier is an excellent example of a voltage amplifier. The second most common amplifier is the *transadmittance amplifier*, which is often referred to in the literature as simply a *transconductor*. The transconductor, which emulates the electrical characteristics of a voltage controlled current source, delivers an output port current that is directly proportional to applied input port voltage. It is the foundation of many broadband lowpass and tuned radio frequency (RF) amplifiers. It also enjoys utility as the gain cell implicit to wideband and ultra linear active resistance-capacitance (RC) filters. The transimpedance ampli*fier*, or *transresistor*, is the dual of the transconductor. It converts an applied input current to an output voltage response and as such, its electrical dynamics approximate the ideal current controlled voltage source. Like the transconductor, the transresistor is often the core active element of broadband networks. It is often synthesized by appending appropriate feedback to a basic voltage amplifier. An operational amplifier operated with resistive feedback between its input and phase-inverted output ports is among the most common of transresistors. Finally, the voltampere characteristics of a *current amplifier* emulate the electrical properties of an ideal current controlled current source. The current amplifier is rarely used as stand-alone circuit architecture. Instead, its impedance transformation attributes encourage its utilization in conjunction with transconductors to arrive at compensated circuits whose bandwidths are, under certain conditions, substantively larger than the bandwidth capabilities of transconductors operated without current amplifier compensation.

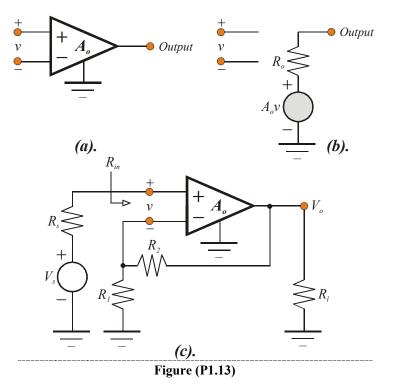

### **1.3.1. VOLTAGE AMPLIFIER**

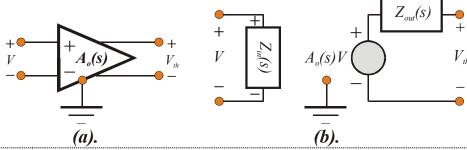

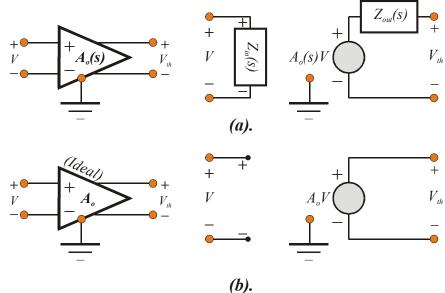

The circuit schematic symbol of a voltage amplifier is diagrammed in Figure (1.12a). Like all simple linear amplifiers, it is a *two port* structure. Its input port, to which signal is applied to establish the differential input port voltage, V, which is ultimately amplified, is comprised of the two terminals labeled "+" and "-." The "+" terminal is called the *non-inverting input terminal*, while the "-" terminal is termed the *inverting node*. The output port on the right of the circuit schematic symbol supports the Thévenin, or open circuit, voltage response,  $V_{th}$ , to applied input excitation. In the most general case, the open circuit, or Thévenin, response,  $V_{th}$ , is extracted differentially between the two terminals that comprise the amplifier output port. If one of the two output port terminals is incident with the amplifier ground terminal,  $V_{th}$  is referred to as a *single ended output voltage*. If, as is diagrammed in the subject figure, neither of the two output port terminals is grounded,  $V_{th}$  is called a *differential output voltage*. Similarly, note that voltage V might be termed a *differential input voltage* because neither of the two input port terminals is established is indicated as common to the amplifier ground.

**Figure (1.12). (a).** Circuit Schematic Symbol Of A Voltage Amplifier. The Amplifier Is Depicted In Its Non-Inverting Mode, Since The Controlling Input Voltage, V, Is Applied Differentially From The Non-Inverting Input Terminal -To-The Inverting Input Terminal. **(b).** Circuit Model Of The Amplifier In (a). Parameter  $Z_{in}(s)$  Is The Driving Point Input Impedance. To First Order, This Impedance Is Independent Of The Load Termination. Parameter  $Z_{out}(s)$  Is The Driving Point Output Impedance Of The Amplifier. The Parameter,  $A_o(s)$ , Is The Thévenin Voltage Gain Of The Amplifier And Is Measured As The Ratio Of The Differential Open Circuit Output Voltage,  $V_{th}$ , -To- The Differential Input Port Voltage, V.

The indicated gain,  $A_o(s)$ , is a frequency dependent transfer function. For V > 0, which indicates that the non-inverting input terminal lies at a signal potential that is larger than the potential established at its inverting counterpart, the Thévenin output voltage is  $A_o(s)V$ , thereby implying no phase inversion between the input and output ports. In other words, if V rises with time, the Thévenin output voltage is an amplified version of voltage V that likewise increases with time. On the other hand, for V < 0, which suggests that V is applied from the "–" input terminal -to- the "+" input terminal, as opposed to the polarity indicated in Figure (1.12a), the open circuit output voltage is  $-A_o(s)V$ , and 180 degree I/O phase inversion is evident.

From Thévenin's theorem, a viable equivalent circuit for the voltage amplifier abstracted in Figure (1.12a) is the model offered in Figure (1.12b). The input port model, which consists of a simple input impedance branch,  $Z_{in}(s)$ , reflects the presumption that no energy sources appear either within the active amplifier block or at the output port of the amplifier. Strictly speaking,  $Z_{in}(s)$  is a driving point input impedance; that is, it is an impedance that is dependent on the load that terminates the amplifier output port. However, in this initial foray

into the world of linear amplifiers,  $Z_{in}(s)$  is presumed independent of the output port load. This presumption means that  $Z_{in}(s)$  is unchanged whether the output port is terminated in a specific load or open circuited, as it is during the process of computing the Thévenin output port voltage. As the student will ultimately learn, this independence of the Thévenin input impedance on load termination is closely approximated if there is insignificant internal feedback implicit to the active amplifier cell. In turn, negligible internal feedback is generally a reasonable presumption at all but very high signal frequencies.

In the output port representation,  $Z_{out}(s)$  is the usual Thévenin equivalent impedance seen looking into the output terminal. This impedance is, in fact, the driving point output impedance in that it is determined under the condition of the input port terminated in the internal impedance of the applied signal source. Like the nominal independence of  $Z_{in}(s)$  on load termination,  $Z_{out}(s)$  is also nominally independent of source impedance if negligible internal feedback prevails within the amplifier itself. The dependent voltage,  $A_o(s)V$ , is the Thévenin voltage established at the output port, while  $A_o(s)$  is the Thévenin voltage gain measured from the differential amplifier input port, where voltage V prevails, -to- the open circuited differential output port where the Thévenin voltage,  $V_{th}$ , is established.

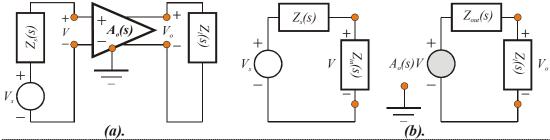

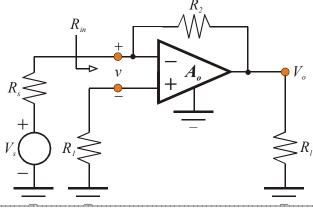

In an actual linear application of the voltage amplifier, a signal voltage source having a Thévenin internal impedance of  $Z_s(s)$  activates the input port, while a load impedance,  $Z_l(s)$ , terminates the output port, as is depicted in Figure (1.13a). Recalling the amplifier model hypothesized in Figure (1.12b), the system model pertinent to Figure (1.13a) is the topology appearing in Figure (1.13b). By inspection, the overall system voltage gain, say  $A_v(s)$ , is

**Figure (1.13). (a).** System Schematic Depiction Of A Voltage Amplifier Terminated In A Load Impedance And Driven At Its Input Port By A Voltage Source. **(b).** Equivalent Circuit Of The System In (a). The Input Voltage, V, And The Output Response,  $V_o$ , Are Taken Herewith As Differential Circuit Branch Voltages. However, And Depending On The Actual System Architecture, Either V Or  $V_o$ , Or Both, Can Be Single Ended Variables. If Both V And  $V_o$  Are Extracted As Single Ended Node Voltages, The System In (a) Is Said To Maintain A Common Ground Between Its Input And Output Ports.

$$A_{v}(s) = \frac{V_{o}}{V_{s}} = \frac{V_{o}}{V} \times \frac{V}{V_{s}} = A_{o}(s) \left[ \frac{Z_{l}(s)}{Z_{l}(s) + Z_{out}(s)} \right] \left[ \frac{Z_{in}(s)}{Z_{in}(s) + Z_{s}(s)} \right],$$

(1-7)

which shows that the overall voltage gain, compared to the Thévenin voltage gain,  $A_o(s)$ , is degraded by a factor equal to the product of input port and output port voltage dividers. The gain,  $A_o(s)$ , is the gain afforded by the amplifying device and is therefore the maximum possible gain achievable in a linear system in which this device is embedded. Accordingly, (1-7) underscores the fact that a linear system degrades the available device gain by the combined effects of nonzero amplifier driving point output impedance and finite amplifier driving point input imped-

ance. This observation begets a stipulation of the electrical characteristics indigenous to an *ideal voltage amplifier*.

- (1). The driving point input impedance,  $Z_{in}(s)$ , is infinitely large for all signal frequencies and for all load terminations. Note that the infinitely large input impedance property implies that zero current is drawn from the signal source by the amplifier input port. As a result, no voltage drop appears across the internal signal source impedance, thereby maximizing the transfer of applied Thévenin source voltage to the amplifier input port.

- (2). The driving point output impedance,  $Z_{out}(s)$ , is zero for all signal frequencies and for all signal source impedances. This characteristic allows an output port voltage to be developed across any load impedance, inclusive (in principle only) of even a short-circuited load. More importantly, the voltage developed across the load termination is the Thévenin output port voltage, which is the maximum possible voltage that can be generated across the terminating load impedance.

- (3). In an ideal voltage amplifier,  $A_o(s)$  is a constant,  $A_o$ , independent of signal frequency. Properties #1 and #2 allow for a system gain that is identically equal to the voltage gain afforded by the amplifying device. Pragmatically, this gain,  $A_o(s)$ , is generally a suitably large, constant, real number, say  $A_o$ , at low frequencies. At high frequencies in the steady state, it attenuates at a minimum rate of 20 *dB/decade* because of unavoidable intrinsic energy storage parasitics. Observe that the idealized constant gain stipulation implies the unrealistic device capability of amplifying signals whose frequencies embody a range extending from "DC" -to- daylight.

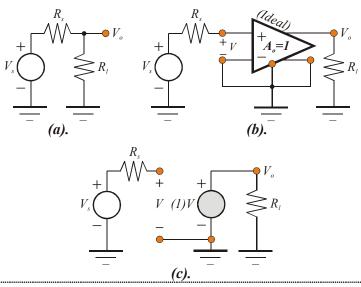

Figure (1.14) summarizes the electrical properties of an ideal voltage amplifier.

Figure (1.14). (a). System Schematic Diagram And Circuit Level Model Of A Voltage Amplifier. (b). System Schematic Diagram And Circuit Level Model Of An Ideal Voltage Amplifier. The Gain Parameter, A<sub>o</sub>, Is A Constant, Independent Of The Frequencies Of Applied Input Signals.

Voltage amplifiers are often operated with differential input and single ended output ports. With reference to Figure (1.12a), the pertinent circuit schematic symbol is the structure shown in Figure (1.15a), and the applicable equivalent circuit appears in Figure (1.15b). In the interest of schematic simplicity, the diagram in Figure (1.15a) is generally cast in the form of Figure (1.15c), where it is understood that the output port voltage,  $V_{th}$ , is now referred to system

ground. The diagrams in Figures (1.13) and (1.14) remain applicable for single ended outputs, with the proviso that the system ground is now incident with the negative terminal of the output voltage response,  $V_o$ .

Figure (1.15). (a). Schematic Portrayal Of A Voltage Amplifier With Single Ended Output. (b). Equivalent Circuit Of The Single Ended Configuration Abstracted In (a). (c). Simplified Schematic Symbol Of A Voltage Amplifier With Single Ended Output. In This Depiction, The Open Circuit Output Voltage,  $V_{th}$ , Is Presumed Measured With Respect To The System Ground.

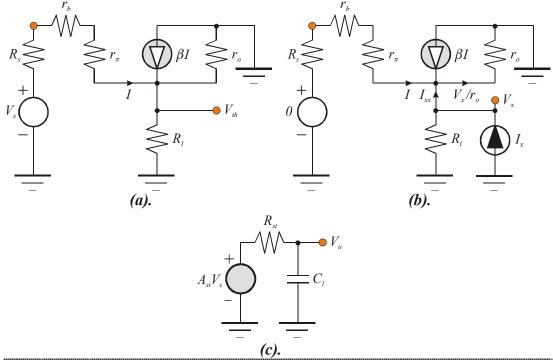

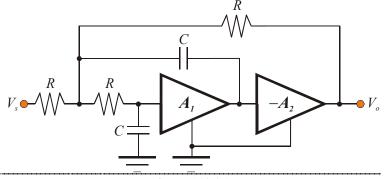

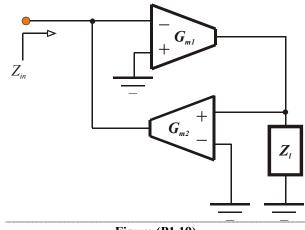

#### **1.3.2. TRANSCONDUCTOR**

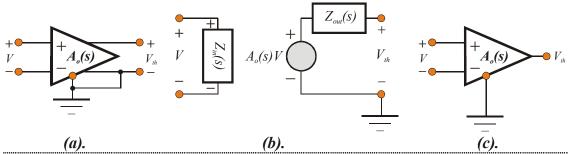

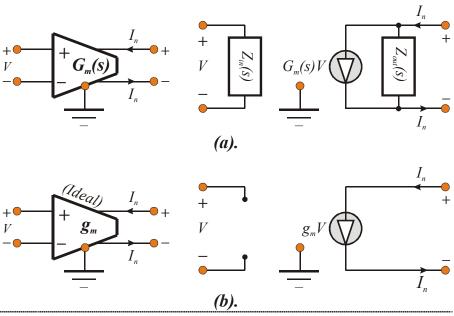

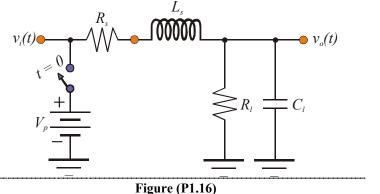

The circuit schematic symbol of a transadmittance amplifier, or transconductor, appears in Figure (1.16a). Yet another name for this amplifier is *operational transconductor amplifier*, which is commonly abbreviated as "*OTA*." The differential input port voltage, V, which is established as a result of applied input signal, is a positive number when it is measured from the non-inverting input terminal (+) -to- the inverting terminal (-). This input port voltage is converted by the transconductor into a short circuit, or Norton, output current,  $I_n$ . The subject Norton current is proportional to V with a proportionality constant,  $G_m(s)$ , whose dimension is mhos; that is,  $I_n = G_m(s)V$ . Note that the positive algebraic sense of  $I_n$  is a current flowing into the positive output terminal and flowing out of the negative output terminal of the transconductor when V > 0. The Thévenin and Norton concepts introduced earlier render the architecture of Figure (1.16b) a plausible two port model of the linear transconductor.

**Figure (1.16). (a).** Circuit Schematic Symbol Of A Transconductance Amplifier. **(b).** Circuit Model Of The Amplifier In (a). Parameter  $Z_{in}(s)$  Is The Driving Point Input Impedance, While  $Z_{out}(s)$  Is The Driving Point Output Impedance Of The Amplifier. The Parameter,  $G_m(s)$ , Is The Norton Transadmittance Of The Transconductor.

Figure (1.17a) offers a linear system application of the transconductor introduced in Figure (1.16), while Figure (1.17b) depicts its corresponding circuit model. As usual,  $Z_s(s)$  represents the source impedance of the applied voltage signal, and  $Z_l(s)$  is the load impedance incident with the transconductor output port. By inspection, the I/O transadmittance, say  $Y_f(s)$ , is

Figure (1.17). (a). System Schematic Diagram Of A Transadmittance Amplifier Terminated In A Load Impedance And Driven At Its Input Port By A Voltage Source. (b). Equivalent Circuit Of The System In (a).

$$Y_{f}(s) = \frac{I_{o}}{V_{s}} = \frac{I_{o}}{V} \times \frac{V}{V_{s}} = G_{m}(s) \left[ \frac{Z_{out}(s)}{Z_{out}(s) + Z_{l}(s)} \right] \left[ \frac{Z_{in}(s)}{Z_{in}(s) + Z_{s}(s)} \right].$$

(1-8)

Analogous to the voltage gain expression in (1-7), this transadmittance function is the product of a maximum transfer function (in this case, a transadmittance function) and two dividers. The first of the two dividers on the right hand side of this relationship, which is a current divider for the system output port in Figure (1.17b), approaches unity as the output impedance,  $Z_{out}(s)$ , tends toward an open circuit. The second divider is an input port voltage divider, which approaches unity as the driving point input impedance,  $Z_{in}(s)$ , emulates the impedance of an open circuit. These observations lead forthwith to the electrical definitions implicit to an *ideal transadmit*-tance amplifier.

- (1). The driving point input impedance,  $Z_{in}(s)$ , is infinitely large for all signal frequencies and for all load terminations. Infinitely large input impedance implies that zero current is drawn from the signal source by the amplifier input port. As a result, no voltage drop appears across the internal signal source impedance, thereby maximizing the transfer of applied Thévenin signal voltage to the amplifier input port.

- (2). The driving point output impedance,  $Z_{out}(s)$ , is infinitely large for all signal frequencies and for all signal source impedances. This characteristic allows for an output current that is identical to the Norton output current and is therefore independent of load impedance.

- (3). In an ideal transconductor or transadmittance amplifier,  $G_m(s)$  is a constant, independent of signal frequency. Properties #1 and #2 allow for a system transadmittance that is identically equal to the transadmittance afforded by the amplifying device. Pragmatically, this forward transfer relationship is generally a suitably large, constant, real number, say  $g_m$ , at low frequencies. At high frequencies in the steady state, the effective forward transconductance attenuates owing to the unavoidable presence of internal energy storage parasitics.

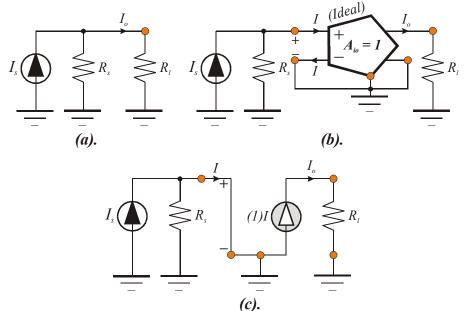

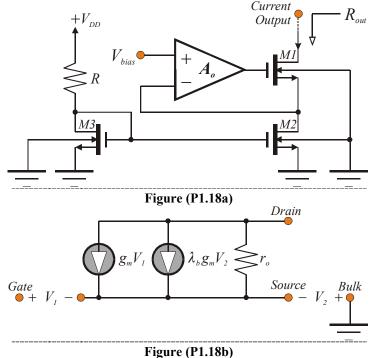

Figure (1.18) reviews the foregoing electrical properties. Observe that the circuit model of an ideal transadmittance amplifier is identical to the schematic abstraction of a voltage controlled current source.

### **1.3.3. TRANSRESISTOR**

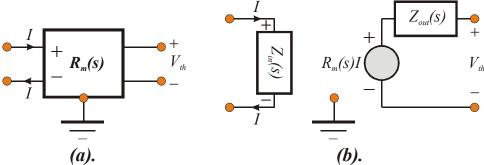

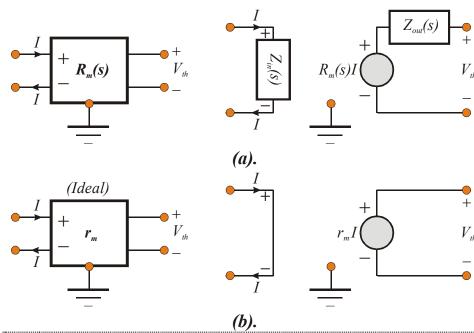

Figure (1.19a) shows the circuit schematic symbol of a transimpedance amplifier, or more simply, a transresistor. This type of amplifier operates on applied input current, I, to generate an output port Thévenin voltage,  $R_m(s)I$ , that is proportional to current I. For a driving point input impedance of  $Z_{in}(s)$  and a driving point output impedance of  $Z_{out}(s)$ , the electrical model is the topology offered in Figure (1.19b).

**Figure (1.18). (a).** System Schematic Diagram And Circuit Level Model Of A Transadmittance Amplifier, Or Transconductor. **(b).** System Schematic Diagram And Circuit Level Model Of An Ideal Transconductor. The Transconductance Parameter,  $g_m$ , Is A Constant, Independent Of Frequency.

**Figure (1.19). (a).** Circuit Schematic Symbol Of A Transresistor. **(b).** Circuit Model Of The Amplifier In (a). Parameter  $Z_{in}(s)$  Is The Driving Point Input Impedance,  $Z_{out}(s)$  Is The Driving Point Output Impedance, and  $R_m(s)$ , Is The Thévenin Transimpedance Of The Device.

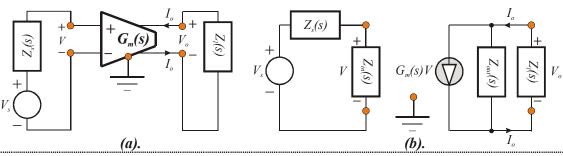

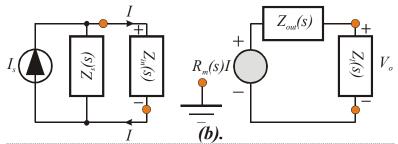

In system level applications of the transresistor, the input signal energy derives from a current source,  $I_s$ , whose presumably large Thévenin impedance is  $Z_s(s)$ , as depicted in Figure (1.20a). Also shown in this schematic diagram is a load impedance,  $Z_l(s)$ , that is incident with the transresistor output port and supports the resultant differential voltage response,  $V_o$ , to the input signal current source. The corresponding equivalent circuit in Figure (1.20b) delivers an I/O transimpedance,  $Z_l(s)$ , given by

$$Z_{f}(s) = \frac{V_{o}}{I_{s}} = \frac{V_{o}}{I} \times \frac{I}{I_{s}} = R_{m}(s) \left[ \frac{Z_{l}(s)}{Z_{l}(s) + Z_{out}(s)} \right] \left[ \frac{Z_{s}(s)}{Z_{s}(s) + Z_{in}(s)} \right].$$

(1-9)

An inspection of this relationship underscores the obvious fact that in the steady state, the magnitude,  $|Z_f(j\omega)|$ , of the overall transimpedance is less than the magnitude,  $|R_m(j\omega)|$ , of the Thévenin output port voltage -to- input port transimpedance. Accordingly, maximal forward transimpedance is afforded when both  $Z_{in}(s)$  and  $Z_{out}(s)$  approach the impedance of a short circuit. This observation readily leads to the definition of an *ideal transimpedance amplifier*.

Figure (1.20). (a). System Schematic Diagram Of A Transimpedance Amplifier Terminated In A Load Impedance And Driven At Its Input Port By A Current Source. (b). Equivalent Circuit Of The System In (a).

- (1). The driving point input impedance,  $Z_{in}(s)$ , is zero for all signal frequencies and for all load terminations. Zero input impedance means that no signal voltage can be sustained across the input port of a transresistor, which in turn suggests the impropriety of driving the input port of a transresistor with a voltage source.

- (2). The driving point output impedance,  $Z_{out}(s)$ , is zero for all signal frequencies and for all signal source impedances. This characteristic implies that the output voltage developed in response to applied input current is theoretically independent of all load terminations.

- (3). In an ideal transresistor or transimpedance amplifier,  $R_m(s)$  is a constant, independent of signal frequency. Properties #1 and #2 allow for a system transimpedance that is identical to the transimpedance of the amplifying device. Pragmatically, this forward transfer relationship is generally a large, constant, real number, say  $r_m$ , at low frequencies. At high frequencies in the steady state, the low frequency value of this transimpedance attenuates because of unavoidable intrinsic energy storage parasitics.

In Figure (1.21), the foregoing electrical properties are reviewed and the electrical model of an ideal transimpedance amplifier is cast as a voltage controlled current source.

Figure (1.21). (a). System Schematic Diagram And Circuit Level Model Of A Transimpedance Amplifier, Or Transresistor. (b). System Schematic Diagram And Circuit Level Model Of An Ideal Transresistor. The Transresistance Parameter, r<sub>m</sub>, Is A Constant, Independent Of Frequency.

#### **1.3.4. CURRENT AMPLIFIER**

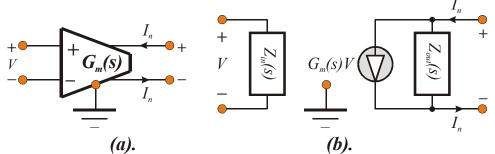

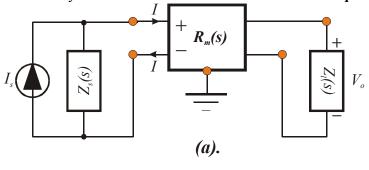

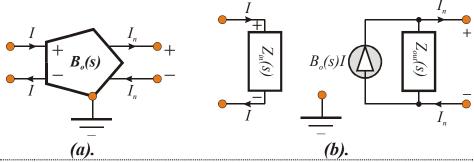

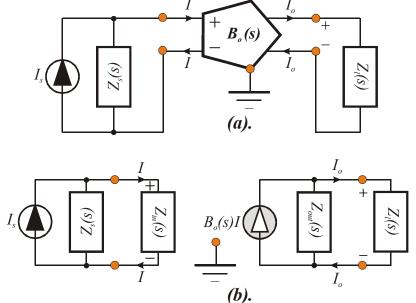

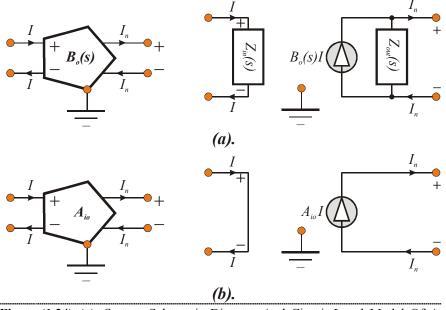

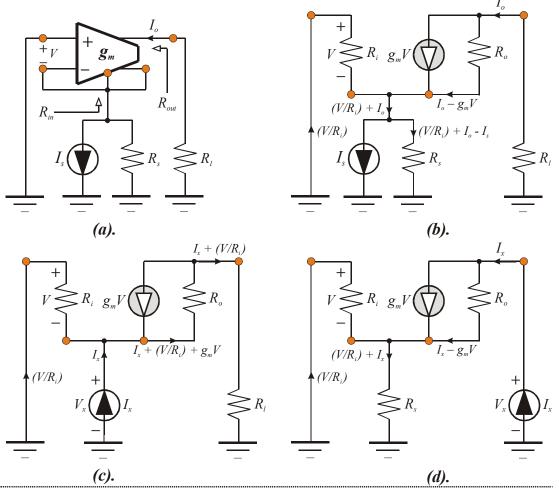

The circuit schematic symbol of a current amplifier appears in Figure (1.22a). This amplifier responds to applied input current, I, to establish a Norton output current,  $I_n = B_o(s)I$ . With a driving point input impedance of  $Z_{in}(s)$  and a driving point output impedance of  $Z_{out}(s)$ , the electrical model of a current amplifier is the network in Figure (1.22b).

**Figure (1.22). (a).** Schematic Symbol Of A Current Amplifier. **(b).** Two Port Model Of The Current Amplifier In (a). Parameters  $Z_{in}(s)$  and  $Z_{out}(s)$  Respectively Denote The Driving Point Input And Output Impedances, While  $B_o(s)$  Is The Norton Current Gain Of The Amplifier.

As in transresistor applications, the signal source applied to the input port of a current amplifier is a current source,  $I_s$ , having a relatively large source impedance,  $Z_s(s)$ . The resultant output response to this applied current is itself a current,  $I_o$ , conducted by load impedance  $Z_l(s)$ , which is connected across the amplifier output port. The system application at hand is abstracted in Figure (1.23a), for which the pertinent electrical model is the circuit diagram shown in Figure (1.23b). This model generates a system current gain expression whose algebraic form is similar to that of the transfer relationships derived for the three previously studied amplification systems; namely,

$$A_{i}(s) = \frac{I_{o}}{I_{s}} = \frac{I_{o}}{I} \times \frac{I}{I_{s}} = B_{o}(s) \left[ \frac{Z_{out}(s)}{Z_{out}(s) + Z_{l}(s)} \right] \left[ \frac{Z_{s}(s)}{Z_{s}(s) + Z_{in}(s)} \right].$$

(1-10)

Clearly,  $A_i(s)$  approximates  $B_o(s)$ , which is the maximum system current gain afforded by the utilized current amplification device, when  $Z_{in}(s)$  is a very small impedance and  $Z_{out}(s)$  is very large. It follows that an *ideal current amplifier* satisfies the requirements itemized herewith.

Figure (1.23). (a). System Level Application Of A Linear Current Amplifier. (b). Equivalent Circuit Of The Current Amplification System In (a).

- (1). The driving point input impedance,  $Z_{in}(s)$ , is zero for all signal frequencies and for all load terminations.

- (2). The driving point output impedance,  $Z_{out}(s)$ , is infinitely large for all signal frequencies and for all signal source impedances. This characteristic implies that the output current developed in response to applied input current is theoretically independent of all load terminations.

- (3). In an ideal current amplifier,  $B_o(s)$  is a constant, independent of signal frequency. Properties #1 and #2 allow for a system current gain that is identical to the maximum current gain allowed by the amplifying device. This current gain is generally a large, constant, real number, say  $A_{io}$ , at low frequencies. At high frequencies in the steady state, the low frequency value of the current gain attenuates at a minimum rate of 20 *dB/decade* because of unavoidable intrinsic energy storage parasitics.

Figure (1.24) overviews the foregoing electrical properties and in the process, it depicts the electrical model of an ideal current amplifier as a current controlled current source.

### **1.3.5. BUFFERS**

As might be suspected, the four types of amplifiers discussed in the preceding subsections of material are most commonly used to boost relatively anemic voltage or current signal amplitudes into more robust voltages and currents that can deliver required amounts of energy to specified loads. For example, consider the futility of connecting an audio speaker directly to the output terminals of a compact disc (CD) player. Typical audio speakers have nominal input impedances in the range of eight -to- sixteen ohms and may require as many as tens of volts of excitation for proper performance and acceptable fidelity. In contrast, the Thévenin output impedance of representative CD units is 500 ohms or larger. Moreover, CD players rarely deliver open circuit output voltages larger than a few tens of millivolts. Since a 16  $\Omega$  speaker connected across a voltage source whose internal resistance is 500  $\Omega$  comprises a voltage divider of roughly 1/32, a CD unit having a 20 mV open circuit output voltage capability delivers only about 620 microvolts to the speaker terminals. This miniscule voltage is hardly sufficient to enjoy the Rolling Stones and thus, an appropriate amplifier (most likely a cascade of several amplifiers intertwined with requisite filters and signal processing subsystems) must be inserted between the CD player and the speaker.

Figure (1.24). (a). System Schematic Diagram And Circuit Level Model Of A Current Amplifier. (b). System Schematic Diagram And Circuit Level Model Of An Ideal Current Amplifier. The Current Gain, A<sub>io</sub>, Is A Constant, Independent Of Frequency.

If signal amplitude amplification is the dominant function of amplifiers, impedance buffering is the second most important application of amplifying networks. Buffers, which are ubiquitous in both analog and digital circuit technologies, perform impedance transformation between input and output ports so that the output voltage -to- signal source voltage transfer function or the output current -to- signal source current gain is maintained very close to unity for wide ranges of signal source and load impedances. Two types of buffers –the *voltage buffer* and the *current buffer*– are commonly found in electronic systems.

### 1.3.5.1. Voltage Buffer

With reference to the generalized ideal voltage amplifier diagrammed symbolically in Figure (1.14b), an *ideal voltage buffer* has a frequency invariant Thévenin voltage gain of unity  $(A_o = I)$  in addition to infinitely large input impedance and zero output impedance for all load and source terminations, respectively. Since the Thévenin voltage gain is the largest possible voltage gain achievable in a system into which a voltage amplifier is embedded within the I/O signal path, it is only natural to question the pragmatism of an active device capable of only unity voltage gain.

**Figure (1.25). (a).** A Voltage Divider For Which The Signal Voltage Of A Source Whose Thévenin Resistance Is  $R_s$  Is To Be Delivered To Load Resistance  $R_l$ . **(b).** Ideal, Buffer Inserted In I/O Signal Flow Path. **(c).** Model Of The Buffered System In (b).

A response to the foregoing inquiry begins by considering the simple voltage divider in Figure (1.25a). In this divider, the output voltage,  $V_o$ , is an attenuated version of the Thévenin signal source voltage,  $V_s$ , since

$$\frac{V_o}{V_s} = \frac{R_l}{R_l + R_s} \,. \tag{1-11}$$

If the hypothetical CD example considered in the preceding subsection is revisited herewith, the divider in question is 16/(16+500) = 1/32.25, which suggests that only 3.1% of the Thévenin signal voltage is actually delivered to the load resistance,  $R_l$ . In other words, 96.9% of this signal voltage is "lost" in the internal resistance,  $R_s$ , of the signal source. In an attempt to mitigate this signal loss, an ideal buffer is inserted between the source and the load, as suggested in Figure (1.25b). Since the subject buffer has infinitely large input impedance, no current is drawn from the signal source and as a result, no voltage is "lost" in the Thévenin resistance of the source. Moreover, the zero output resistance of the buffer allows an output voltage response to be established across a load resistance of any value. The propriety of these assertions is confirmed by the model in Figure (1.25c), which produces

$$\frac{V_o}{V_s} = \frac{V_o}{V} \times \frac{V}{V_s} = (1)(1) = 1.$$

(1-12)

Thus, 100% of the Thévenin signal source voltage appears across the network output port as voltage  $V_o$ , independent of either load termination or source resistance.

Of course, no physically realizable voltage buffer is ideal. The practical buffer addressed in Examples (1.1) and (1.2), delivers a large, but nonetheless finite, input resistance of 344.7 K $\Omega$ , a small, but nonzero, output resistance of 20.51  $\Omega$ , and a nearly unity gain of 0.993. If this buffer supplants its idealized counterpart in Figure (1.25),  $R_s = 500 \Omega$ ,  $R_l = 16 \Omega$ , and (1-7)

lead to a voltage transfer function of  $V_o/V_s = 1/2.3$ . This result is hardly the desired ideal unity value, but it is *14-times* better than the non-buffered value of 1/32.25.

#### **EXAMPLE #1.3:**

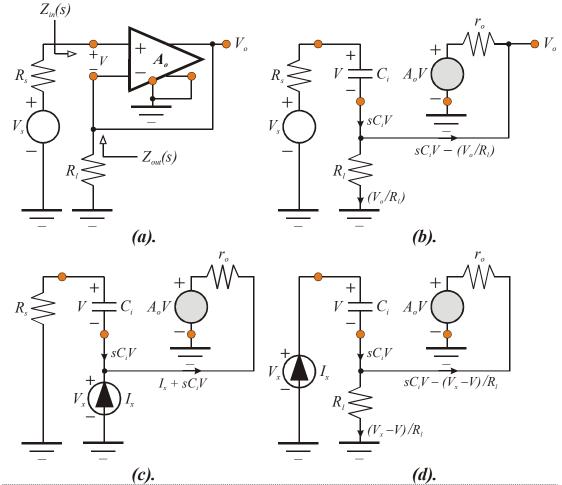

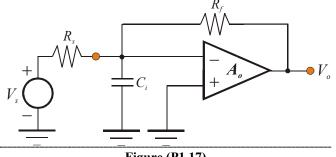

Operational amplifiers (op-amps) of reasonable quality can be gainfully exploited as voltage buffers in broadband electronic system applications. To this end, Figure (1.26a) depicts a voltage buffer realized with an op-amp having a single ended output port. For the purpose of this problem, assume that the op-amp has a Thévenin voltage gain (often referred to in the literature as the *open loop gain*) of  $A_o = 80 \ dB$ , an output resistance,  $r_o$ , of 35  $\Omega$ , and an input impedance that is purely capacitive. The net value of the input capacitance, which is plausibly attributed to the combined effects of the op-amp, incorporated compensation, and circuit parasitics, is  $C_i = 300 \ pF$ . The Thévenin resistance,  $R_s$ , of the signal source is  $500 \ \Omega$ , while the load resistance,  $R_l$ , driven by the buffer is  $16 \ \Omega$ . Derive general expressions for, and discuss the engineering significance of, the system voltage gain,  $A_v(s) = V_o/V_s$ , the output impedance,  $Z_{out}(s)$ , seen by the load resistance,  $R_l$ , and the input impedance,  $Z_{in}(s)$ , seen by the signal source.

#### SOLUTION #1.3:

(1). Recalling Figure (1.14b) and using the information provided in this problem, Figure (1.26b) is the equivalent circuit of the buffer in Figure (1.26a). In terms of the branch currents delineated in this diagram, KVL gives

$$A_o V = -r_o \left( sC_i V - \frac{V_o}{R} \right) + V_o$$

$$V_s = R_s \left( sC_i V \right) + V + V_o$$

Subsequent to elimination of variable V from these equilibrium relationships, a bit of algebra confirms an I/O voltage transfer function of the form,

$$A_{v}(s) = \frac{V_{o}}{V_{s}} = \left(\frac{kA_{o}}{l+kA_{o}}\right) \left(\frac{l+\frac{s}{z}}{l+\frac{s}{p}}\right),$$

(E3-1)

where

$$k = \frac{R_l}{R_l + r_o} \tag{E3-2}$$

is a voltage divider between the resistances,  $r_o$  and  $R_l$ . Moreover, the input port capacitance appears to generate a left half plane pole at frequency p, as well as a left half plane zero at frequency z. These critical frequencies are given by

$$p = \frac{l + kA_o}{\left(R_s + kr_o\right)C_i}$$

(E3-3)

and

$$z = \frac{A_o}{r_o C_i}.$$

(E3-4)

(2). Several features of the voltage transfer function in (E3-1) warrant highlighting. First, observe that the system gain at zero frequency is

$$A_{\nu}(0) = \frac{kA_o}{l+kA_o}, \qquad (E3-5)$$

which is almost one by virtue of very large  $A_o$ . In the present case,  $A_o = 80 \ dB = 10,000$  and k = 0.3137, whence  $A_v(0) = 0.9997$ . It therefore appears that at least at low signal frequencies, the circuit in Figure (1.26a) very nearly satisfies the unity voltage gain objective of an ideal voltage buffer.

**Figure (1.26). (a).** Operational Amplifier With Single Ended Output Configured As A Voltage Buffer. The Signal Source Is Represented As The Series Interconnection Of Voltage  $V_s$  And Resistance  $R_s$ , While The Load Driven By The Buffer Is Taken To Be The Resistance,  $R_l$ . **(b).** Equivalent Circuit Of The System In (a). The Indicated Branch Currents Are Appropriate To A Determination Of The System Voltage Gain,  $A_v(s) = V_o/V_s$ . **(c).** Equivalent Circuit For The Determination Of The Driving Point Output Impedance,  $Z_{out}(s)$ . **(d).** Equivalent Circuit For Evaluating The Driving Point Input Impedance,  $Z_{in}(s)$ .

The locations of the pole and zero of the voltage transfer function define the frequency response of the buffer at hand. In the present case,  $p = 2\pi(3.26 \text{ GHz})$ , and  $z = 2\pi(151.6 \text{ GHz})$ . The frequency of the zero is better than 46-times larger than the frequency of the pole and is, in fact, so large as to render dubious its validity in light of the frequency response limitations implicit to the utilized simple model. Numerical validity notwithstanding, the frequency of the zero is so much larger than that of the pole as to warrant its tacit neglect over a frequency passband extending from zero through, and somewhat beyond, the pole frequency. Accordingly,

#### Choma & Chen

$$A_{\nu}(s) = \frac{V_o}{V_s} \approx \frac{kA_o/(1+kA_o)}{1+\frac{s}{p}},$$

(E3-6)

from which it is apparent that the *3-dB* bandwidth, say  $\omega_b$ , is

$$\omega_b \approx p = \frac{l + kA_o}{\left(R_s + kr_o\right)C_i} \approx \frac{kA_o}{\left(R_s + R_l \|r_o\right)C_i} = 2\pi(3.26 \text{ GHz}). \quad (E3-7)$$

Thus, the buffer undergoing examination delivers very nearly unity gain from zero signal frequency to almost 3.3 GHz.

(3). The "ohmmeter" model pertinent to computing the driving point output impedance,  $Z_{out}(s)$ , seen by the load resistance,  $R_l$ , is depicted in Figure (1.26c). For the branch currents indicated in this diagram, KVL produces

$$0 = R_{s} (sC_{i}V) + V + V_{x}$$

$$V_{x} = r_{o} (I_{x} + sC_{i}V) + A_{o}V.$$

(E3-8)

Upon elimination of the voltage variable, V, in these two relationships, it is easily demonstrated that the output impedance, expressed in terms of steady state frequency variables, is

$$Z_{out}(j\omega) = \frac{V_x}{I_x} = \left(\frac{r_o}{l+A_o}\right) \left(\frac{l+j\omega\tau_z}{l+j\omega\tau_p}\right),$$

(E3-9)

where the time constant,  $\tau_z$ , associated with the zero of the impedance function and the time constant,  $\tau_p$ , attributed to the impedance function pole are respectively given by  $\tau_z = R_s C_i$  (E3-10)

and

$$\tau_p = \frac{\left(R_s + r_o\right)C_i}{l + A_o}.$$

(E3-11)

(4). From (E3-9), the low frequency output impedance is

$$Z_{out}(0) = \frac{r_o}{l+A_o},$$

(E3-12)

which is virtually zero because of the very large amplifier gain,  $A_o$ . Indeed,  $Z_{out}(0)$  computes herewith to 0.0035  $\Omega$ , which assuredly emulates the zero output impedance indigenous to an ideal voltage buffer.

The time constant associated with the impedance zero is  $\tau_z = 150 \text{ nSEC}$ , which corresponds to a frequency of  $1/\tau_z = 2\pi(1.07 \text{ MHz})$ . On the other hand,  $\tau_p = 16.05 \text{ pSEC}$ , corresponding to a frequency,  $1/\tau_p = 2\pi(9.92 \text{ GHz})$ . Clearly, the pole frequency is significantly larger (over 9,000-times larger) than the zero frequency. It follows that for frequencies as large as an octave or two below the pole frequency,

$$Z_{out}(j\omega) \approx \left(\frac{r_o}{l+A_o}\right) (l+j\omega\tau_z),$$

(E3-13)

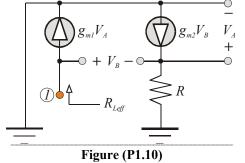

which suggests that the driving point output impedance is inductive. Specifically, this impedance reflects a resistance, say  $R_{eff}$ , connected in series with an inductance, say  $L_{eff}$ , such that

$$R_{eff} = \frac{r_o}{l+A_o}, \qquad (E3-14)$$

and

$$L_{eff} = \left(\frac{r_o}{l+A_o}\right)\tau_z = \frac{r_o R_s C_i}{l+A_o}.$$

(E3-15)

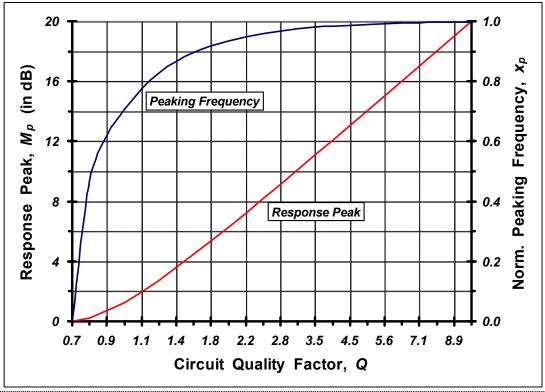

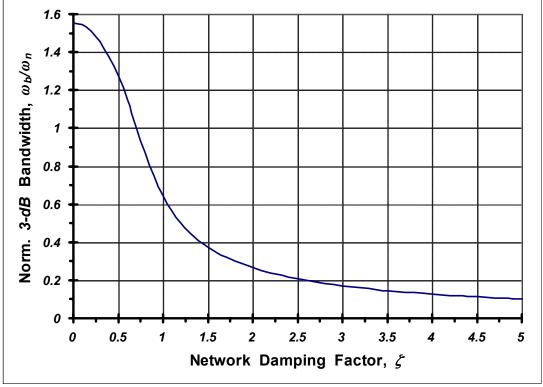

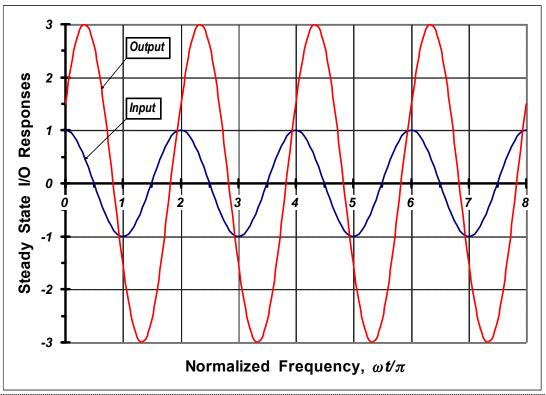

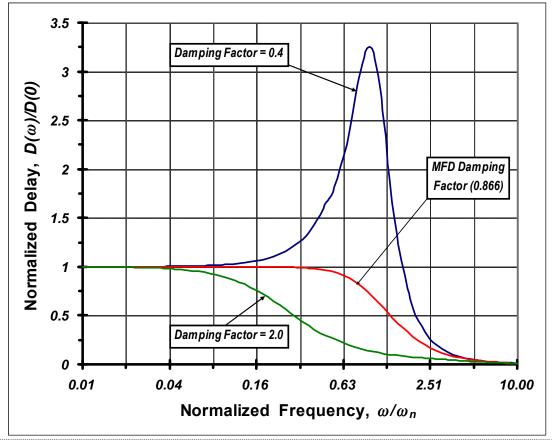

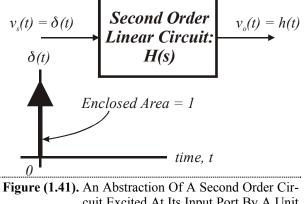

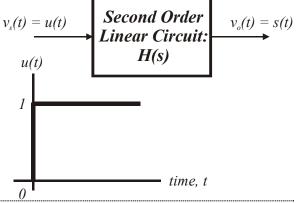

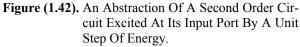

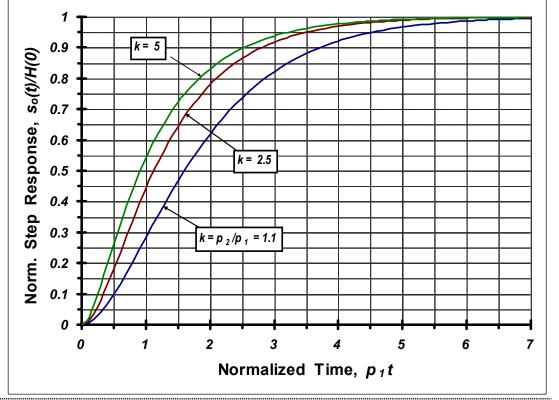

The indicated effective resistance is, as anticipated, the previously determined zero frequency value of the output impedance. Although the effective series inductance is small, it can cause poor transient circuit responses and/or even resonant frequency responses when, as is commonly encountered, the buffer drives a strongly capacitive load.