EECS 143 Microfabrication Technology

# Lab Report 1

## **Table of Contents**

- 1. Profiles & Layout (14 Points)

- 2. Process Procedures (20 points)

- 3. Calculations (36 Points)

- 4. Questions (30 Points)

- 5. Bonus Questions (10 Points)

Total Points = 110 possible (graded out of 100)

Please be sure to include the requirement signature regarding academic honesty. All lab group members should print out this page, sign on the attached form, and include it with your Lab Report. Thank you!

**REPORTS MUST BE WORD PROCESSED (EXCEPT FOR SKETCHES AND HAND WRITTEN CALCULATIONS)**

Each group of students will submit one joint report. There will be a 20 PAGE max limit on the report. Profiles & Layout and Calculations do not count towards this page limit. <u>FOLLOW THE ATTACHED TEMPLATE FORMAT</u> <u>FOR THE REPORT. STUDENTS NOT FOLLOWING THIS FORMAT WILL BE</u> <u>DEDUCTED 10% PER SECTION DEVIATING FROM TEMPLATE.</u> When possible, be concise and use structured bullet points!

Due Date: Tuesday, April 22<sup>nd</sup> 2007, 3:45pm in class. Please also submit an electronic copy to your TA by the same deadline.

There is a 10pt Deduction for Late Reports Per day.

#### I. Profiles & Layout (14 Points)

Draw cross-sectional profiles of a *MOSFET* (test structure 8) after each of the steps:

W1: Staring Wafer

W2: Field Oxidation

W3: ACTV Photolithography and Etch

W4: Gate Oxidation

W5: Polysilicon CVD

W6: POLY Lithography and Etch, Source/Drain Clear

W7a: Spin-on Glass + Source/Drain Pre-diffusion

W7b: Source/Drain Drive-in + Intermediate Oxidation

W8: CONT Photolithography and Etch

W9: Aluminum Evaporation

W10: METL Photolithography + Etch

Indicate all layers. Label each feature and indicate thicknesses (make roughly proportional sketches). Illustrate and describe important details:

- non-planar interfaces from thermal oxidation

- isotropic etch profiles

- point-source Al evaporation

- thermal oxidation growth

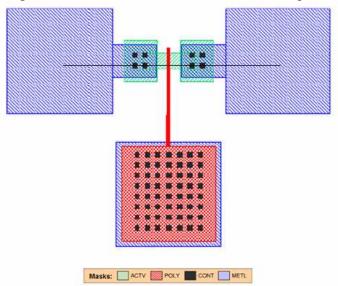

These drawings should have significantly more detail than those on the lab manual website. See the diagram below for the exact cross-sections in question. (5 Points)

B. Draw top views of the same thin-oxide *MOSFET* (test structure 8) after each of the four photolithography steps. [ACTV, POLY, CONT, METL] (4 Points)

#### II. Process Procedures (20 Points) [Refer to Template at the back of the Report]

A. Describe monitoring measurements that were done during processing:

Film color Line Width Thickness Resistivity Vernier

Determine whether each layer was overetched or underetched? Did you purposely over/underetch? Why?

Include a table of your misalignments for each layer.

Describe how the verniers are used to measure misalignment. Using diagrams may help. Were any layers misaligned intentionally? For each pair of verniers (ACTV-POLY, ACTV-CONT, POLY-CONT, CONT-METL), describe how far the marks may be misaligned in terms of device function. (6 Points)

B. List and concisely describe the possible problems that could have occurred during the batch fabrication steps:

W2: Field Oxidation

W4: Gate Oxidation

W5: Poly Deposition

W7a: Source-Drain Prediffusion

W7b: Drive-In & Intermediate Oxidation

W9: Aluminum Evaporation

W10: Sintering

What were the sources of the problems, and how could you avoid them? How do you expect these deviations to affect the performance/function and cross-section of the device? List the types of monitoring measurements from Part A taken during each step (7 Points)

C. Other than the problems that occurred during the batch sessions, what were the particular problems (or deviations from other groups) that could occur in YOUR wafer? Specifically these are the steps where all wafers were run in individually.

W3: ACTV PhotolithographyW6: POLY PhotolithographyW7: SOG Deposition & SOG StripW8: CONT PhotolithographyW10: METL Photolithography

What were the causes and how were the problems overcome? How would these affect device performance? Include any illustrations that would be helpful. List the types of measurements from Part A taken during each step (7 Points)

### **III.**Calculations (36 Points) [Refer to Report Template at Back of Report]

Fill the template table with the following parameters from your own wafer: (3 points)

- a) Film thickness (each layer)

- b) Sheet Resistance (after ion implantation and S&D formation)

- c) % over/underetch measured photoresist from theoretical (each layer)

Calculate the parameters asked for in the following questions—list both the theoretical values and the empirical values, when applicable. We would like to see that you understand what processing abnormalities may have led to a discrepancy between the two. Neatly write up and annotate all calculations and attach in appendix. (Points will be deducted if we can not understand what you wrote).

- 1. Theoretical and experimental thicknesses of field oxide, gate and intermediate oxides (Include orientation dependence of oxidation rate but not impurity dependence) (10 points)

- 2. Junction depths after pre-diffusion and drive-in (theoretical, assume only phosphorous doping with surface concentration limited by solid solubility). You must consider the effect of the initial ion implantation. For pre-deposition you may use the box approximation, but for drive-in you must use the half-gaussian calculation. Why is this? (10 points)

- 3. Final surface concentrations of dopants, as determined from Irvin's curves using sheet resistance measurements made in lab. (2 points)

- 4. Plot or sketch the change of dopant profile from the silicon surface through the source-drain after each thermal step.

- Field Oxidation

- Gate Oxidation

- Poly-Deposition

- Pre-Deposition

- Drive-In & Intermediate Oxidation.

- Sintering

Quantitatively label significant points such as Peak concentration, Peak Width, Junction Depth. Show movement of the Silicon-Silicon Dioxide interface and qualitatively show non-ideal effects such as dopant redistribution during oxidation. (12 points)

5. Lateral diffusion under the MOSFET gates. You may estimate. Justify estimation. (Theoretical). (2 points)

#### IV. Questions (30 Points – 2.5 points each) (3 Page Limit)

Answer these questions in the most concise manner possible. A few lines should suffice for each.

- 1. What type of photoresist (positive or negative? I-line or G-line?) do we use in the lab? What do I-line and G-line refer to? Briefly describe how the resist responds to the process steps like spinning, UV light exposure and development.

- 2. What is the purpose of baking the wafers at 120 °C before depositing HMDS? What is the purpose of the 90 °C bake after spinning on photoresist? What happens if the soft bake is too hot and too long (say 120 °C, 5 minutes)?

- 3. What is the purpose of hard bake? What happens if we skip this step? What may happen if the bake is done at a temperature above 120 °C (say 200 °C)?

- 4. We do lithography steps under yellow light only. What is the consequence if we expose the wafers to fluorescent light before development? What if we expose them to fluorescent light after development? Would red light damage your process?

- 5. What are the differences between wet and dry oxidation that lead us to use one for the gate oxide and one for the field/intermediate oxide? What is the purpose of annealing in nitrogen after oxidation?

- 6. How do you determine etching time using theoretical etch rate in literature? List two ways to determine etch time empirically from lab measurements, when you etch the layers. (Hint: these methods include visual cues.). How close are the experimental and the theoretically calculated values?

- 7. Before n+ deposition (prior to SOG spinning), we clean in Piranha but not in HF. Before gate oxidation, we clean in both. Why the difference?

- 8. Why is 5:1 BHF (5:1 NH<sub>4</sub>F:HF) used for etching features in the oxide while 10:1 BHF is used for cleaning and spin-on-glass stripping? Why buffered HF?

- 9. What would happen if we skipped the HF dip before metallization?

- 10. What is etch selectivity?

- 11. Why do we first use the roughing pump and then the diffusion pump when pumping down the aluminum deposition system? Why must the foreline pressure be kept below 100 mTorr?

- 12. What is the Al etchant composed of? What happens if you use it at room temperature? What is the purpose of sintering? What will result if sintering step is skipped? What happens if sintering temperature is too hot or too low?

#### V. Bonus Questions (up to 10 Points)

- 1. Describe an alternate method for doing two of the process steps (i.e. LOCOS instead of Field Oxide and Sputtering instead of Evaporation, or ion implantation instead of SOG, etc.) and the tradeoffs. [5 points]

- 2. Simulate the 143 process flow in Tsuprem4. A simplified model is written and provided for you on the website. Modify the provided Tsuprem4 code to match the parameters of one of your MOSFETs, and print off your code and a cross section diagram of the final MOSFET side-profile for your report. [5 points]

*Note:* These questions are \*bonus\*, so please do not ask your lab GSI for help with them!

### Lab Report Template:

I. Profiles & Layout:

A. Thin oxide MOSFET Cross Section

B. Top Views

#### II. Process Procedures:

- A. Process Monitoring Measurements

- Measurement Type and Description

- Over-Etch/Under-Etch

- Misalignment Tolerance

### B& C. Batch and Individual Processing Steps:

Week 2: Field Oxidation:

- Batch Processing Problems

- Measurements Taken

#### Week 3: Field Oxide Cut

- Individual Processing Problems

- Measurements Taken

Week 4: Gate Oxidation

- Batch Processing Problems

- Measurements

Week 5: Poly Deposition

- Batch Processing Problems

- Measurements

Week 6: Gate Definition

- Individual Processing Problems

- Measurements

#### Week 7: S/D Diffusion and Intermediate Oxidation

- Batch Processing Problems

- Individual Processing Problems

- Measurements

#### Week 8: Contact Hole Cut

- Individual Processing Problems

- Measurements

Week 9: Metallization

- Batch Processing Problems

- Measurements

Week 10: Metal Definition

- Batch Processing Problems

- Individual Processing Problems

- Measurements

- III. Calculations:

- IV. Questions:

- V. Bonus:

- VI. Appendix:

Calculations Results Template: Film Thicknesses: (\*\*note: Not all lab sections took Linewidths after PR strip, those may skip that column\*\*)

| Layer          | Theoretical | Experimental | % Error |

|----------------|-------------|--------------|---------|

|                | Calculation |              |         |

| Field Oxide    |             |              |         |

| Polysilicon    |             |              |         |

| Gate Oxide     |             |              |         |

| Intermed Oxide |             |              |         |

| Aluminum       |             |              |         |

#### Overetch:

| Layer          | Measured Linewidth | % Overetch | Theoretical Etch Time | Actual Etch Time | % Overetch |

|----------------|--------------------|------------|-----------------------|------------------|------------|

| Field Oxide    |                    |            |                       |                  |            |

| Polysilicon    |                    |            |                       |                  |            |

| Gate Oxide     |                    |            |                       |                  |            |

| Intermed Oxide |                    |            |                       |                  |            |

| Aluminum       |                    |            |                       |                  |            |

Sheet Resistance:

| Layer                      | Sheet Resistance | Surface Concentration (Calculated) |

|----------------------------|------------------|------------------------------------|

| ACTV After Field Oxidation |                  |                                    |

| ACTV After Pre-Dep         |                  |                                    |

| ACTV After Drive-in        |                  |                                    |

Theoretical Junction Depth

| Layer               | Vertical Junction Depth | Lateral Junction Depth |

|---------------------|-------------------------|------------------------|

| ACTV After Pre-Dep  |                         |                        |

| ACTV After Drive-in |                         |                        |

## EECS 143 Lab Report 1

Spring 2008

In signing below, I attest to the fact that I have read and have adhered to the policies and guidelines discussed in the EECS Departmental Policy on Academic Dishonesty, as found at: <u>http://www-inst.eecs.berkeley.edu/~ee143/fa05/policy.html</u>

| Name:      |

|------------|

| Signature: |

| Date:      |

| Name:      |

| Signature: |

| Date:      |

| Name:      |

| Signature: |

| Date:      |