US 20040069124A1

## (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2004/0069124 A1 Murakai et al.

Apr. 15, 2004 (43) Pub. Date:

(54) MUSICAL SOUND GENERATOR, PORTABLE TERMINAL, MUSICAL SOUND GENERATING METHOD, AND STORAGE **MEDIUM**

Inventors: Yasuvuki Murakai, Hamamatsu-shi (JP); Ichiro Futohashi, Hamakita-shi

Correspondence Address: Pillsbury Winthrop **Intellectual Property Group Suite 2800** 725 South Figueroa Street Los Angeles, CA 90017-5406 (US)

Appl. No.: 10/344,806

PCT Filed: Aug. 17, 2001

PCT No.: PCT/JP01/07092 (86)

(30)Foreign Application Priority Data

(JP) ...... 2000-248469 Aug. 18, 2000 May 28, 2001 (JP) ...... 2001-158994

### **Publication Classification**

(51) **Int. Cl.**<sup>7</sup> ...... **G10H** 1/06; G10H 7/00

#### (57)ABSTRACT

There are provided a musical tone-generating apparatus which neither requires hardware having an increased circuit size nor imposes a heavy burden on a CPU thereof, and a mobile terminal apparatus including the musical tone-generating apparatus, as well as a musical tone-generating method, and a storage medium storing a program for executing the method. A CPU converts music contents data stored in a RAM to hardware tone generator control data, stores the resulting data into the RAM. In reproduction, the CPU reads out and sends the hardware tone generator control data to a hardware tone generator. A data decoder circuit of the hardware tone generator sequentially reads out the hardware tone generator control data from a FIFO and separates the read data into time management information and data of a parameter for generation of a musical tone, and sets the time management information to a counter. Under the control of the counter performing the time management, a register write controller writes data of the parameter into a tone generator control register at timing indicated by the time management information. A tone generator section produces the musical tone based on the data stored in the tone generator control register.

FIG. 3A

FIG. 3B

FIG. 4

**FIG.** 5

|     |                      | CONTR                                          | GENERATOR<br>OL REGISTER<br>DAPTED DATA |

|-----|----------------------|------------------------------------------------|-----------------------------------------|

| • S | SMAF                 | TONE<br>GENERATO<br>CONTRO<br>REGISTE<br>INDEX | L CONTROL                               |

|     |                      | (PROGRAM CHANGE) → INDEX : 1                   | 8h DATA : 10h                           |

| 00  | 00 30 47<br>00 37 7F | (CHANNEL VOLUME) → INDEX : E                   |                                         |

| 00  | 2C 50                | (NOTE MESSAGE) → INDEX : B                     |                                         |

| 00  | 20 30                | INDEX : C                                      | 0h DATA: 32h                            |

| 5C  | 2B 20                | (NOTE MESSAGE) → INDEX : B                     | 00h DATA : 8Bh                          |

| 50  | 20 20                | INDEX : C                                      | Oh DATA: 32h                            |

| 2D  | D5 07                | (NOTE MESSAGE) → INDEX : E                     | 33h DATA : CCh                          |

| 20  | <b>D</b> 3 07        | INDEX : C                                      | C3h DATA: 2Dh                           |

| 00  | 29 50                | (NOTE MESSAGE) → INDEX : E                     | 30h DATA : 44h                          |

|     | :                    | INDEX : C                                      | Oh DATA: 32h                            |

|     | •                    |                                                |                                         |

| INDEX      | D7              | D6      | D5      | D4                  | D3     | D2   | D1_                                           | D0      |

|------------|-----------------|---------|---------|---------------------|--------|------|-----------------------------------------------|---------|

| 01h        |                 | <u></u> |         |                     |        |      |                                               | START   |

| 0111       | <del></del>     |         |         |                     |        |      |                                               | 2110    |

| 18~1Fh     | CH n-           | +1 TON  | E COLOF | R NO.               | CH     | TONE | COLO                                          | R NO.   |

| F-Num[7:0] |                 |         |         |                     |        |      |                                               |         |

| B0∼BFh     | BFh F-Null[7.0] |         |         |                     |        |      |                                               |         |

| C0~CFh     | RESE            | RVED    | KEY ON  | 00                  | TAVE[2 | :0]  | F-Nu                                          | ım[9:8] |

|            |                 |         |         |                     |        |      |                                               |         |

| E0~EFh     | RESERVED        |         |         | CHANNEL VOLUME[4:0] |        |      | <u>0]                                    </u> |         |

|            |                 |         |         |                     |        |      |                                               |         |

|                                                     | DATA                                                |

|-----------------------------------------------------|-----------------------------------------------------|

|                                                     | INDEX                                               |

| •<br>•<br>•                                         | :                                                   |

| DATA                                                | DATA                                                |

| INDEX                                               | INDEX                                               |

| TIME<br>AANAGEMENT INI<br>NFORMATION                | TIME<br>MANAGEMENT<br>INFORMATION                   |

| TIME MANAGEMENT INFORMATION- DISCRIMINATING ADDRESS | TIME MANAGEMENT INFORMATION- DISCRIMINATING ADDRESS |

FIG. 9

| ADDRESS<br>/INDEX | DATA |              |                                                                     |

|-------------------|------|--------------|---------------------------------------------------------------------|

| FFh               | 00h  |              |                                                                     |

| 18h               | 10h  | •            |                                                                     |

| E0h               | 1Fh  | (KEY ON)     | TONE GENERATOR CONTROL                                              |

| B0h               | B2h  |              | REGISTER WRITE DATA A                                               |

| C0h               | 32h  |              | J .                                                                 |

| FFh               | 50h  | _            | TONE GENERATOR CONTROL                                              |

| B0h               | B2h  | (KEY OFF)    | BEGISTER WRITE DATA B                                               |

| C0h               | .12h |              | DUE TO GATE TIME = 50, WITH LAPSE OF REFERENCE TIME PERIOD 50 AFTER |

| FFh               | 0Ch  |              | KEY-ON OF A, KEY-OFF EFFECTED                                       |

| B0h               | 8Bh  | (KEY ON)     | TONE GENERATOR CONTROL                                              |

| C0h               | 32h  |              | REGISTER WRITE DATA C                                               |

| FFh               | 20h  |              | TONE GENERATOR CONTROL                                              |

| B0h               | 8Bh  | (KEY OFF)    | BEGISTER WRITE DATA D                                               |

| C0h               | 12h  |              | DUE TO GATE TIME = 20, WITH LAPSE OF REFERENCE TIME PERIOD 20 AFTER |

| FFh               | 0Dh  |              | KEY-ON OF C, KEY-OFF EFFECTED                                       |

| B3h               | CCh  | (KEY ON)     | 4                                                                   |

| C3h               | 2Dh  | ((T) ( O) () | TONE GENERATOR CONTROL                                              |

| B0h               | 44h  | (KEY ON)     | REGISTER WRITE DATA E                                               |

| C0h               | 32h  |              | J                                                                   |

| •                 | :    |              |                                                                     |

| FFh               | 01h  |              |                                                                     |

| 01h               | 00h  |              | SEQUENCER TERMINATED                                                |

FIG. 11

|                                   | DATA                              |

|-----------------------------------|-----------------------------------|

| <u>.</u>                          | SEQUENCER<br>TERMINATING<br>INDEX |

| DATA                              | SE                                |

| INDEX                             | :                                 |

|                                   | DATA                              |

| TIME DATA MANAGEMENT INFORMATION  | INDEX                             |

| DATA                              | TIME<br>MANAGEMENT<br>INFORMATION |

| INDEX                             | MANAG                             |

| TIME<br>MANAGEMENT<br>INFORMATION |                                   |

FIG. 13

| TIME                   | TONE GENERATOR<br>CONTROL REGISTER<br>WRITE DATA |      |                       |

|------------------------|--------------------------------------------------|------|-----------------------|

| MANAGEMENT INFORMATION | INDEX                                            | DATA |                       |

| 00h                    | 18h                                              | 10h  |                       |

| 00h                    | E0h                                              | 1Fh  |                       |

| 00h                    | B0h                                              | B2h  | (KEY ON)              |

| 00h                    | C0h                                              | 32h  |                       |

| 50h                    | B0h                                              | B2h  | (KEY OFF)             |

| 00h                    | C0h                                              | 12h  |                       |

| 0Ch                    | B0h                                              | 8Bh  | (KEY ON)              |

| 00h                    | C0h                                              | 32h  |                       |

| 20h                    | B0h                                              | 8Bh  | (KEY OFF)             |

| 00h                    | C0h                                              | 12h  |                       |

| 0Dh                    | B3h                                              | CCh  | (KEY ON)              |

| 00h                    | C3h                                              | 2Dh  |                       |

| •                      | •                                                |      |                       |

| :                      | :<br><b>C</b> 0h                                 | 32h  |                       |

| 80h 32                 | :                                                | :    |                       |

| •                      | :                                                | :    |                       |

| 01h                    | 01h                                              | 00h  | SEQUENCER TERMINATION |

FIG. 16

# TONE GENERATOR CONTROL REGISTER

| TIME                      | WRITE DATA |             |  |  |  |

|---------------------------|------------|-------------|--|--|--|

| MANAGEMENT ON INFORMATION | INDEX      | DATA        |  |  |  |

| 80h                       | 98h        | 80h         |  |  |  |

| 80h                       | 33h 81h    | 1Dh 3Eh 9Fh |  |  |  |

| 01h 80h                   | B0h        | B2h         |  |  |  |

| 80h                       | C0h        | B2h         |  |  |  |

| D0h                       | B0h        | B2h         |  |  |  |

| 80h                       | C0h        | 92h         |  |  |  |

| 12h 8Ch                   | B0h        | 8Bh         |  |  |  |

| 80h                       | 38h 81h    | 32h         |  |  |  |

| A0h                       | 68h 81h    | 10h 11h 92h |  |  |  |

| 80h                       | C0h        | 92h         |  |  |  |

| 8Dh                       | B3h        | CCh         |  |  |  |

| 80h                       | C3h        | 2Dh 80h     |  |  |  |

| :                         | •          | :           |  |  |  |

| •                         | •          |             |  |  |  |

| 80h 32                    | C0h        | 32h         |  |  |  |

| <b>:</b>                  | •          | •           |  |  |  |

| :                         | 01b        | 00h         |  |  |  |

| 01h                       | 01h        | 0011        |  |  |  |

FIG. 21

FIG. 24

## MUSICAL SOUND GENERATOR, PORTABLE TERMINAL, MUSICAL SOUND GENERATING METHOD, AND STORAGE MEDIUM

### TECHNICAL FIELD

[0001] This invention relates to a musical tone-generating apparatus which has a simple construction and is capable of generating melodies, a mobile terminal apparatus, a musical tone-generating method, and a storage medium storing a program for executing the method.

### **BACKGROUND ART**

[0002] Conventional musical tone-generating apparatuses include a hardware musical tone-generating apparatus which uses hardware to generate musical tones, and a software musical tone-generating apparatus which causes a computer to execute a musical tone-generating program to generate musical tones.

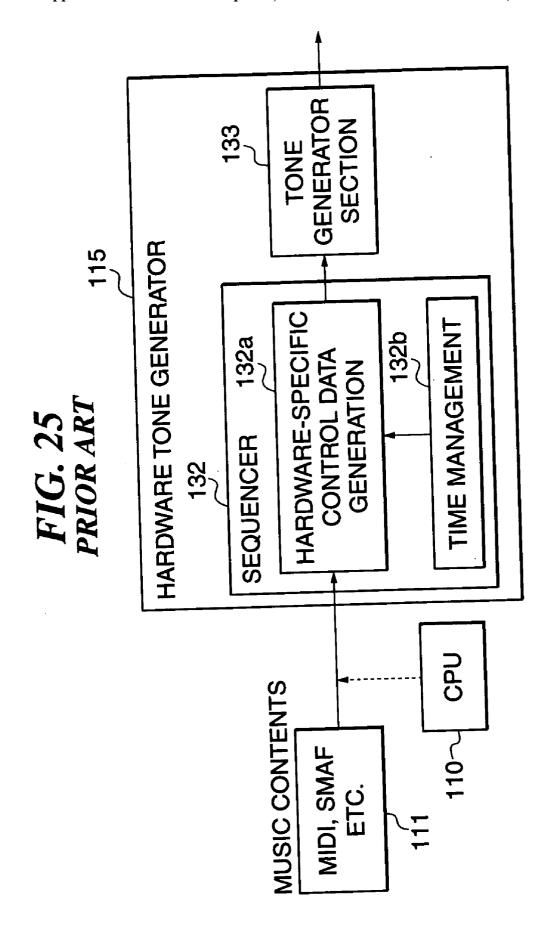

[0003] FIG. 25 shows an example of the arrangement of the conventional hardware musical tone-generating apparatus. In FIG. 25, a CPU (Central Processing Unit) 110 supplies music contents data 111, such as MIDI (Musical Instrument Digital Interface) data and SMAF (Synthetic Music Mobile Application Format) data, referred to hereinafter, to a hardware tone generator 115. In this case, the MIDI data and SMAF data may be transferred from the outside of the apparatus, or read from a storage means of the apparatus. The hardware tone generator 115 includes a sequencer 132, and a tone generator section implemented by hardware. The sequencer 132 has hardware-specific control data-generating section 132a which converts the MIDI data and the SMAF data to control data specific to the hardware tone generator 115, and a time management section 132b which manages the timing of sounding musical tones based on time management information contained in the data.

[0004] In the hardware musical tone-generating apparatus constructed as above, the time management section 132b instructs the hardware-specific control data-generating section 132a to output data in timing based on interval data indicative of time intervals between events contained in the control data and gate time data indicative of a sounding time period. Responsive to the instruction, the hardware-specific control data-generating section 132a delivers the hardware-specific control data generated thereby to the tone generator section 133. The tone generator section 133 generates musical tones based on the supplied hardware-specific control data. Thus, the musical tones are reproduced.

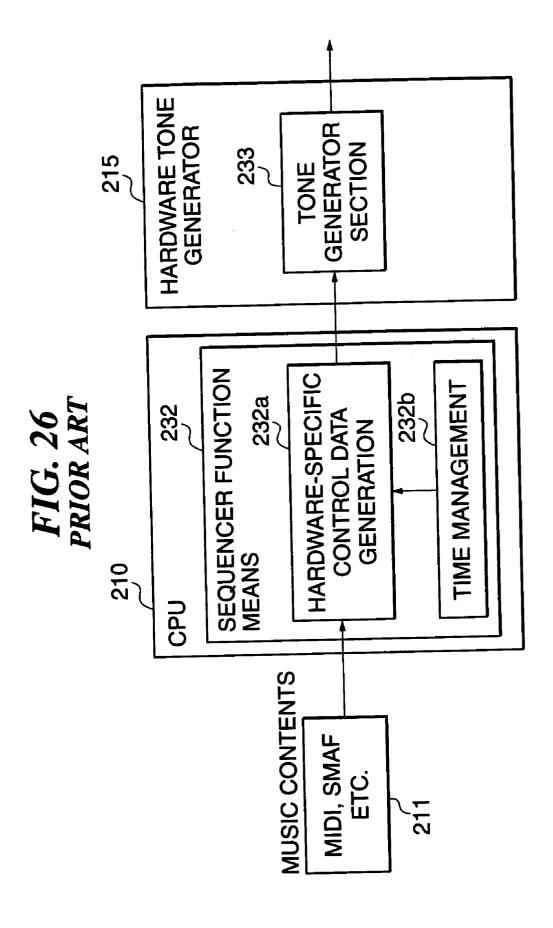

[0005] FIG. 26 shows an example of the arrangement of the conventional software musical tone-generating apparatus. In FIG. 26, a CPU 210 includes a sequencer function means 232 which is realized by a sequencer program executed by the CPU 210. The sequencer means 232 is comprised of a hardware-specific control data-generating means 210a, and a time management means 210b. The hardware-specific control data-generating means 210a which converts MIDI data and SMAF data 211 to control data specific to a hardware tone generator 215, while the time management means 210b controls the timing of sounding musical tones. It should be noted that the MIDI data and the SMAF data converted by the hardware-specific control data-generating means 210a may be transferred from the outside of the apparatus or read from a storage means of the

apparatus. Further, the hardware tone generator 215 which generates musical tones from the hardware-specific control data includes a tone generator section 233 implemented by hardware.

[0006] In the software musical tone-generating apparatus thus constructed, to reproduce musical tones, the time management means 210b of the CPU 210 instructs the hardware-specific control data-generating means 210a to output data in timing based on duration data indicative of time intervals between events, and gate time data indicative of a sounding time period, both of which data are contained in the converted hardware-specific control data. Responsive to the instruction, the hardware-specific control data-generating means 210a delivers the hardware-specific control data generated thereby to the hardware tone generator 215. In the hardware tone generator 215, the tone generator section 233 generates and outputs musical tones based on the hardware-specific control data supplied. The musical tones are thus reproduced by the software musical tone-generating apparatus.

[0007] However, in the hardware musical tone-generating apparatus which is a musical tone-generating apparatus implemented by hardware, the sequencer 132 executes the conversion of the musical contents data and time management, which complicates the construction of the sequencer 132, resulting in an increased circuit size of the sequencer, and hence increased manufacturing costs.

[0008] Further, in the software musical tone-generating apparatus which is a musical tone-generating apparatus implemented by software, the CPU 210 carries out the conversion of musical contents data and time management, which imposes a large burden on the CPU 210, and hence a high-speed CPU is required. Particularly, when the CPU executes other processing with higher importance, such as communication control, as its main function, an expensive high-speed CPU is required to carry out the processing of the sequencer.

[0009] Further, the conventional hardware tone-generating apparatus and the conventional software tone-generating apparatus starts reproduction of a musical piece from the head thereof. This cause the inconvenience that when the musical piece is reproduced as an incoming call music for a cellular phone or the like, only the leading portion of the musical piece can be heard.

## DISCLOSURE OF INVENTION

[0010] It is a first object of the invention to provide a musical tone-generating apparatus which neither requires hardware having an increased circuit size nor imposes a heavy burden on a CPU thereof, and a mobile terminal apparatus including the musical tone-generating apparatus, as well as a musical tone-generating method, and a storage medium storing a program for executing the method.

[0011] It is a second object of the invention to enable such a musical tone-generating apparatus and a cellular phone to reproduce the musical piece starting with a desired point thereof.

[0012] To attain the first object, according to a first aspect of the invention, there is provided a musical tone-generating apparatus comprising software process means for converting music contents data to hardware tone generator control data

which can be reproduced and hardware tone generator means for generating a musical tone based on a parameter for generation of the musical tone which is contained in the hardware tone generator control data, whenever timing based on time management information contained in the hardware tone generator control data is reached.

[0013] According to this musical tone-generating apparatus, software process means converts music contents data to hardware tone generator control data, and time management is executed by hardware tone generator means. Therefore, the size of a circuit of a sequence provided in the hardware tone generator means can be reduced. In this case, the time management can be carried out by a simplified construction using counter means. Further, since the software process means is not required to carry out processing for the time management, a burden on the software process means can be reduced, thereby dispensing with the use of a high-speed CPU.

[0014] Preferably, the musical tone-generating apparatus includes storage means for storing the music contents data, and the software process means converts the music contents data stored in the storage means to the hardware tone generator control data by making use of time during which the software process means has extra processing capability, and stores the converted hardware tone generator control data in the storage means.

[0015] According to this preferred embodiment, the software process means converts the music contents data stored in the storage means to the hardware tone generator control data by making use of time during which the software process means has extra processing capability. Therefore, it is possible to prevent a load from being concentrated on the software process means, whereby it is possible to further reduce the needs of a high-speed CPU.

[0016] Preferably, the hardware tone generator means includes buffer memory means that can store a predetermined amount of the hardware tone generator control data, and the software process means converts the music contents data in such an amount that the resulting hardware tone generator control data can be stored in the buffer memory means, and transfers the resulting hardware tone generator control data to the buffer memory means.

[0017] Preferably, the hardware tone generator means includes counter means for starting counting of clocks of a clock signal generated whenever a unit of reference time elapses, a tone generator control register that controls generation of the musical tone based on the parameter for generation of the musical tone, and write means for writing the parameter following the time management information into the tone generator control register when a count of the counter means becomes equal to or larger than a value indicated by the time management information.

[0018] To particularly attain the second object, the musical tone-generating apparatus includes point register means for storing data of an arbitrary performance start point, and the hardware tone generator means generates musical tones based on hardware tone generator control data starting with a point corresponding to the data of the performance start point stored in the point register means.

[0019] According to this preferred embodiment, the musical tone-generating apparatus includes point register means

for storing data of an arbitrary performance start point, and musical tones are reproduced based on hardware tone generator control data starting with a point corresponding to the data of the performance start point stored in the point register means. Therefore, it is possible to reproduce a musical piece as contents data starting with a desired point thereof. This makes it possible to listen to the musical piece reproduced as an incoming call music, starting with a desired point of the musical piece.

[0020] Preferably, when the software process means converts the music contents data to the hardware tone generator control data, if time management information items have an identical value, and index information items indicative of addresses into which a parameter for generation of a musical tone is to be written are successive to each other, an immediately following one of the index information items which immediately follows the time management information items is set to a leading index information item, and the parameter for generation of a musical tone which follows the immediately following index information item is formed by a plurality of parameters corresponding to the index information items successive to each other.

[0021] According to this preferred embodiment, if time management information items have an identical value, and index information items indicative of addresses into which a parameter for generation of a musical tone is to be written are successive to each other, an immediately following one of the index information items which immediately follows the time management information items is set to a leading index information item, and the parameter for generation of a musical tone which follows the immediately following index information item is formed by a plurality of parameters corresponding to the index information items successive to each other, whereby the amount of hardware-based tone generator control data cab be reduced, thereby reducing the burden on the software processing means and hardware-based tone generator means.

[0022] More preferably, the hardware tone generator means includes counter means for starting counting of clocks of a clock signal generated whenever a unit of reference time elapses, a tone generator control register that controls generation of the musical tone based on the parameter for generation of the musical tone, and write means for writing the parameter following the time management information into the tone generator control register when a count of the counter means becomes equal to or larger than a value indicated by the time management information, and if the parameter is formed by data of the plurality of parameters, writes each parameter data into the tone generator control register while incrementing the address indicated by the index information one by one.

[0023] More preferably, the software process means includes separator means for separating the hardware tone generator control data into the parameter for generating the musical tone and the time management information.

[0024] Further preferably, the hardware tone generator control data is composed of units each comprising a set of the time management information, and at least one pair of an index designating an address of the tone generator control register and data of the parameter to be written into the address.

[0025] Even more preferably, each of the units of the tone generator hardware control data is formed by the time management information, the index, and the data of the parameter.

[0026] Even more preferably, the time management information includes a time management information-discriminating address which indicates whether or not data immediately following the time management information-discriminating address is data of the value indicated by the time management information.

[0027] To attain the first object, according to a second aspect of the invention, there is provided a mobile terminal apparatus comprising a musical tone-generating apparatus including software process means for converting music contents data to hardware tone generator control data which can be reproduced, the conversion processing device being realized by software, and hardware tone generator means for generating a musical tone based on a parameter for generation of the musical tone which is contained in the hardware tone generator control data, whenever timing based on time management information contained in the hardware tone generator control data is reached, and a processing device that performs processing of mobile terminal functions, wherein the software process means is realized by part of functions of the processing device.

[0028] According to this mobile terminal apparatus, the same advantageous effects as describe above can be obtained.

[0029] To particularly attain the second object, it is preferred that the musical tone-generating apparatus point register means for storing data of an arbitrary performance start point, and wherein the hardware tone generator means generates musical tones based on hardware tone generator control data starting with a point corresponding to the data of the performance start point stored in the point register means.

[0030] According to this preferred embodiment, the same advantageous effects as describe above can be obtained.

[0031] To attain the first object, according to a third aspect of the invention, there is provided a musical tone-generating method comprising the steps of converting music contents data to hardware tone generator control data which can be reproduced, by software, and generating a musical tone based on a parameter for generation of the musical tone which is contained in the hardware tone generator control data, whenever timing based on time management information contained in the hardware tone generator control data is reached.

[0032] According to this musical tone-generating method, the same advantageous effects as described above can be obtained.

[0033] To attain the first object, according to a fourth aspect of the invention, there is provided a storage medium storing a program for causing a computer to execute a musical tone-generating method, the program comprising a conversion process module that converts music contents data to hardware tone generator control data which can be reproduced, and a hardware tone generator module that generates a musical tone based on a parameter for generation of the musical tone which is contained in the hardware tone

generator control data, whenever timing based on time management information contained in the hardware tone generator control data is reached.

[0034] According to this storage medium, the same advantageous effects as described above can be obtained.

### BRIEF DESCRIPTION OF DRAWINGS

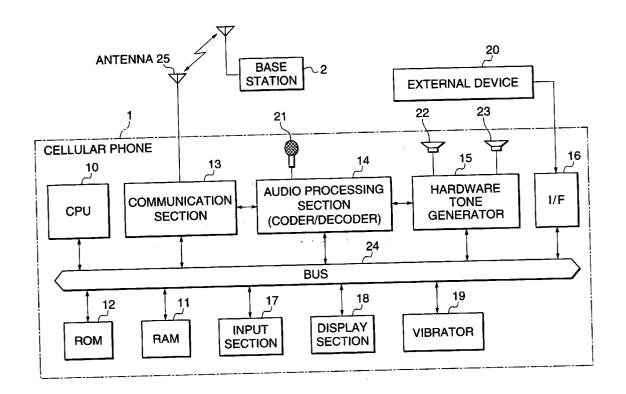

[0035] FIG. 1 is a diagram showing an example of the configuration of a cellular phone to which is applied a mobile terminal apparatus provided with a musical tone-generating apparatus according to a first embodiment of the present invention;

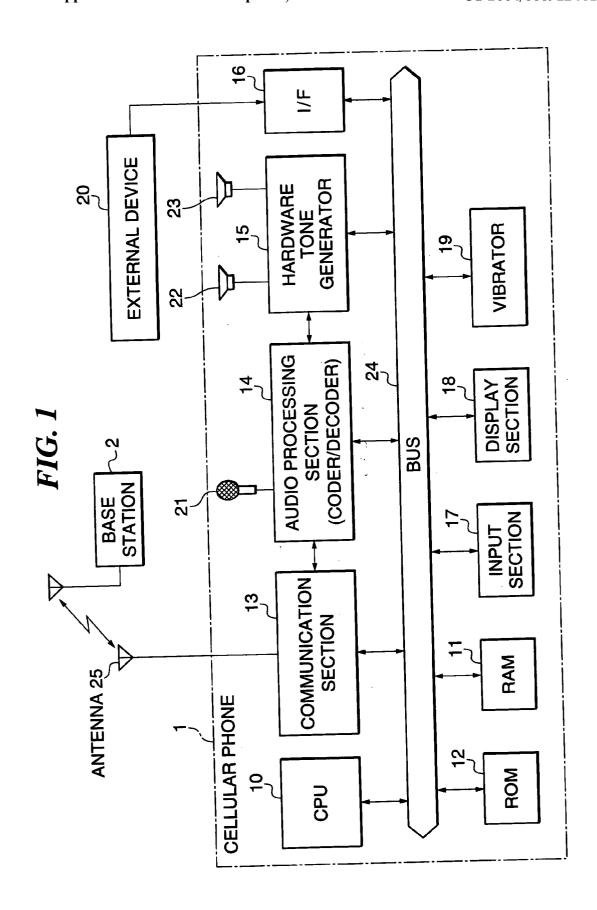

[0036] FIG. 2 is a diagram showing an example of the construction of the musical tone-generating apparatus according to the first embodiment;

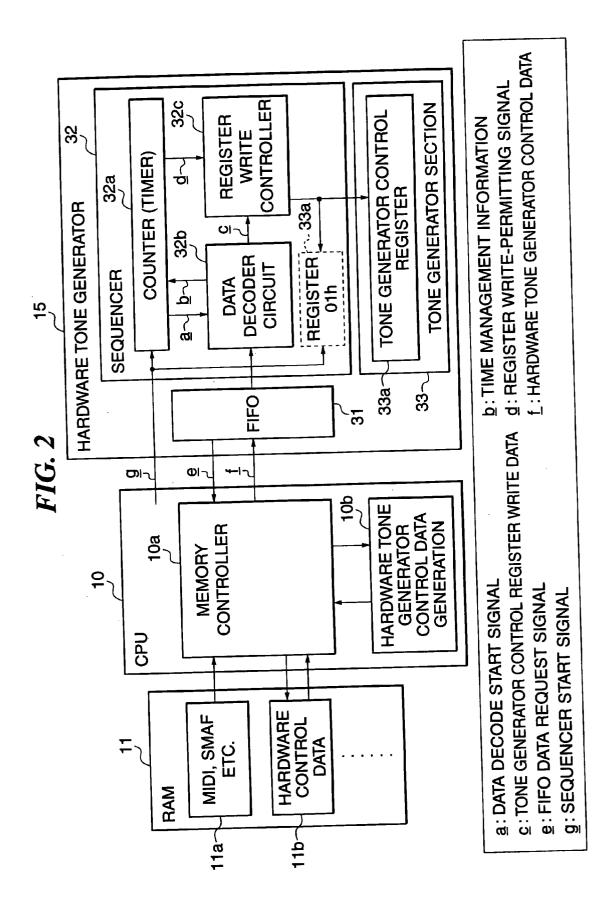

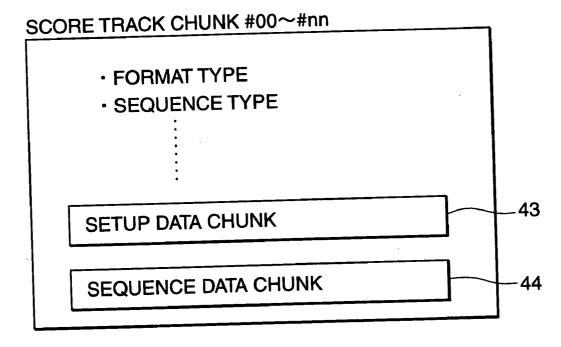

[0037] FIG. 3A is a diagram showing a data structure of SMAF data format.

[0038] FIG. 3B is a diagram showing a data structure of a score track chunk in the data structure of the SMAF data format;

[0039] FIG. 4 is a diagram showing a data structure of a sequence data chunk in the score track chunk of the SMAF data format:

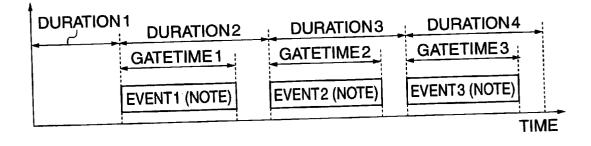

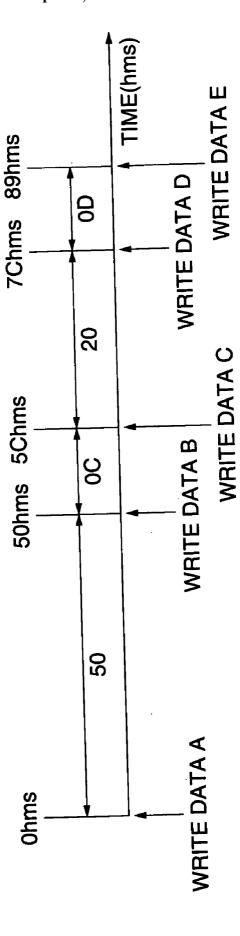

[0040] FIG. 5 is a diagram showing sequence data as an example of the SMAF data plotted along time axis;

[0041] FIG. 6 is a diagram showing a format of data adapted to a tone generator control map with time management information of hardware tone generator control data omitted, used in the musical tone-generating apparatus according to the first embodiment, in a manner associated with SMAF data before conversion;

[0042] FIG. 7 is a diagram showing the tone generator control register map used in the musical tone-generating apparatus according to the first embodiment;

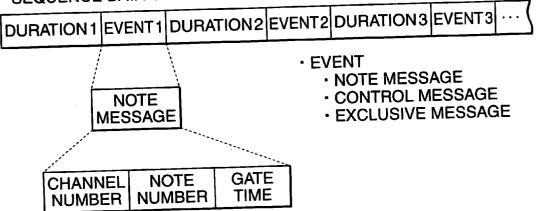

[0043] FIG. 8 is a diagram showing a first data structure of the hardware tone generator control data including the time management information, used in the musical tonegenerating apparatus according to the first embodiment;

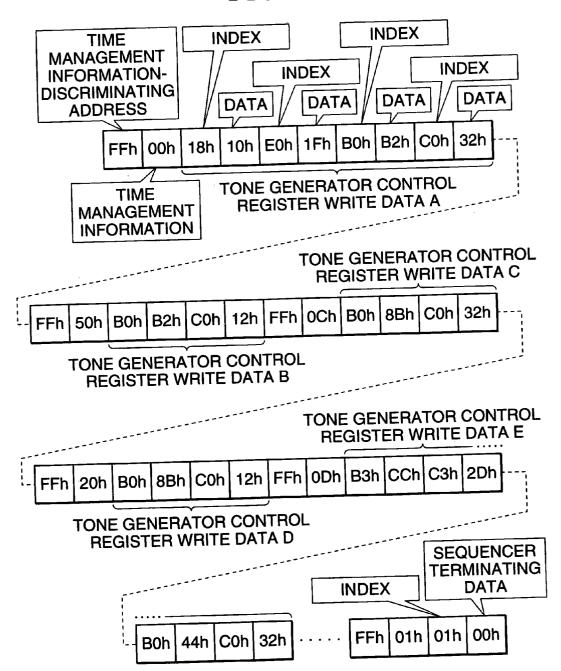

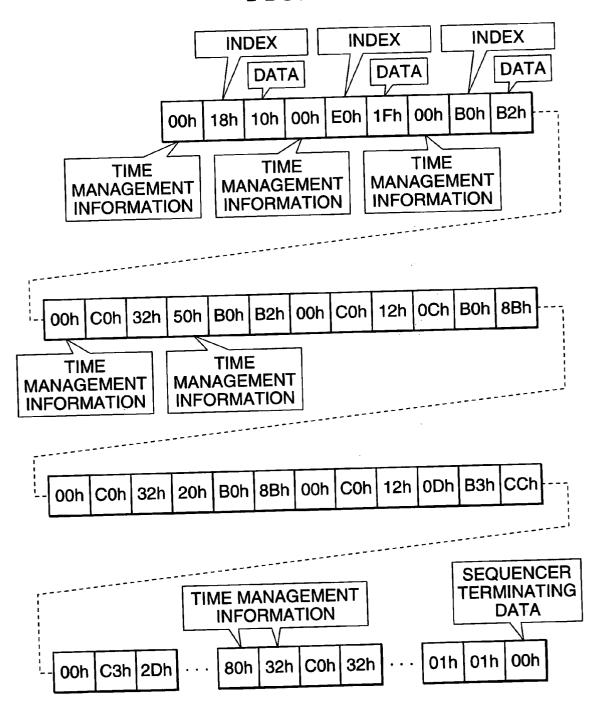

[0044] FIG. 9 is a diagram showing an example of the hardware tone generator control data having the first data structure used in the musical tone-generating apparatus according to the first embodiment;

[0045] FIG. 10 is a diagram showing the hardware tone generator control data having the first data structure, which are rearranged in sets of data;

[0046] FIG. 11 is a timing chart showing timing in which the hardware tone generator control data having the first data structure are written by the musical tone-generating apparatus according to the first embodiment;

[0047] FIG. 12 is a diagram showing a second data structure of the hardware tone generator control data, used in the musical tone-generating apparatus according to the first embodiment;

[0048] FIG. 13 is a diagram showing an example of the hardware tone generator control data having the second data structure used in the musical tone-generating apparatus according to the first embodiment;

[0049] FIG. 14 is a diagram showing the hardware tone generator control data having the second data structure, which are rearranged in sets of data;

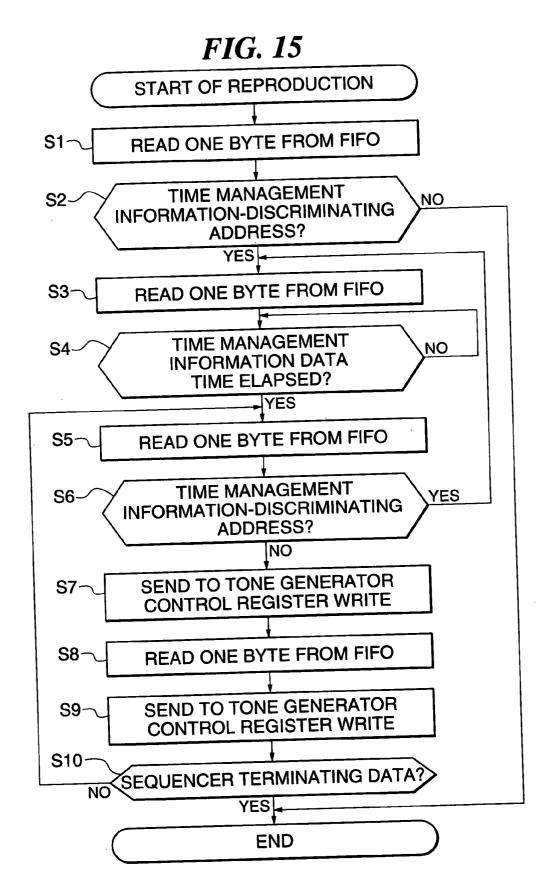

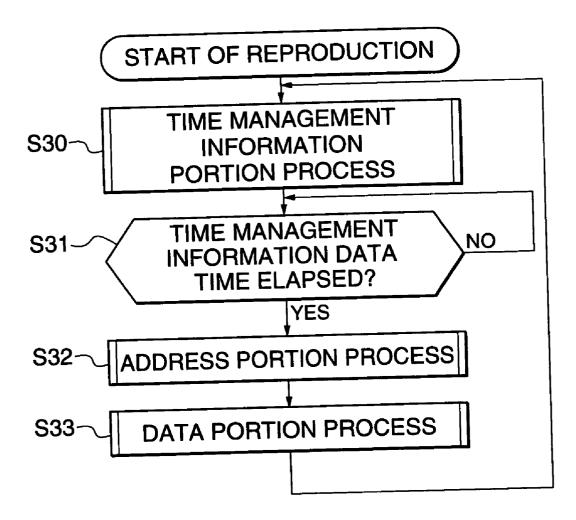

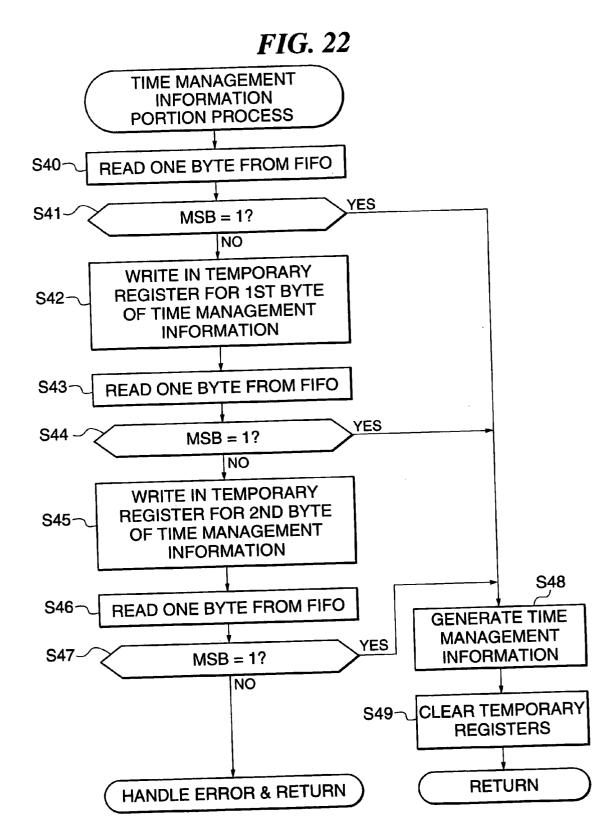

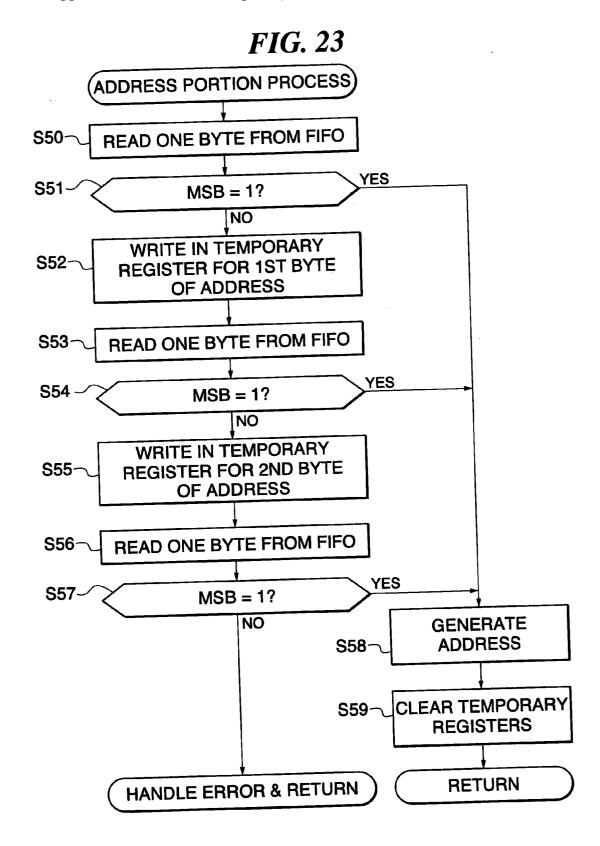

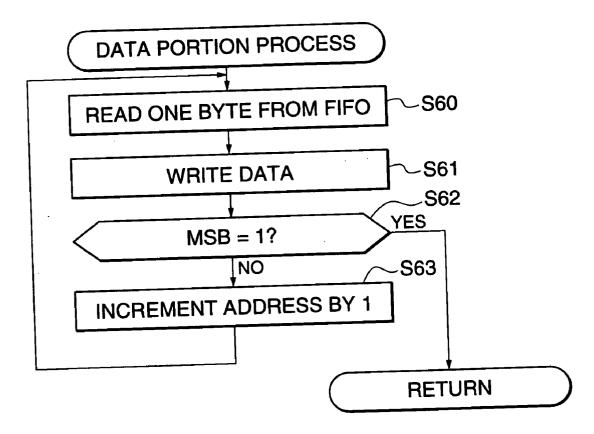

[0050] FIG. 15 is a flowchart showing a reproduction process executed by a sequencer of a hardware tone generator of the musical tone-generating apparatus according to the first embodiment, for reproducing the tone generator control register data having the first data structure;

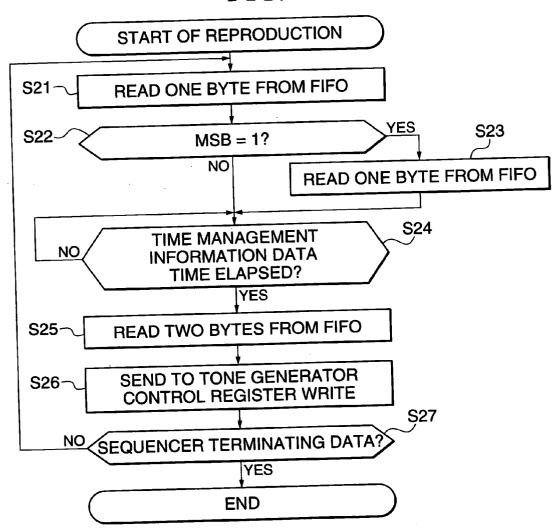

[0051] FIG. 16 is a flowchart showing a reproduction process executed by the sequencer of the hardware tone generator of the musical tone-generating apparatus according to the first embodiment, for reproducing the tone generator control register data having the second data structure;

[0052] FIG. 25 is a diagram showing a conventional musical tone-generating apparatus implemented by hardware; and

[0053] FIG. 26 is a diagram showing a conventional musical tone-generating apparatus implemented by software

# BEST MODE OF CARRYING OUT THE INVENTION

[0054] Now, the present invention will be described in detail with reference to the drawings showing embodiments thereof.

[0055] FIG. 1 shows an example of the configuration of a cellular phone to which is applied a mobile terminal apparatus provided with a musical tone-generating apparatus according to a first embodiment of the present invention, together with a base station.

[0056] The cellular phone 1 is provided with an antenna 25, which is generally a retractable type and can be connected to the base station 2 by radio. The antenna 25 is connected to a communication section 13 having a modulating/demodulating function. A CPU (Central Processing Unit) 10 serves as a system controller that controls components of the cellular phone 1 by executing a telephone function program, and includes a timer that indicates elapsed time during operation and generates a timer interrupt at predetermined time intervals. Further, the CPU 10 carries out processes related to generation of musical tones such as a data conversion process, as described in detail hereinafter. A RAM (Random Access Memory) 11 provides a storage area for storing music contents data of a distribution format which are downloaded from a download center or the like connected via the basic station 2, a storage area for storing hardware tone generator control data converted from the music contents data, and a work area for the CPU 10. A ROM (Read Only Memory) 12 stores various programs executed by the CPU 12 such as telephone function programs for sending or receiving a call, programs for processes related to generation of musical tones, and various data, such as preset hardware tone generator control data.

[0057] The communication section 13 carries out demodulation of a signal received at the antenna 25, as well as modulation of a signal to be transmitted and supplies the modulated signal to the antenna 25. The incoming call signal demodulated by the communication section 13 is decoded by an audio processing section (coder/decoder) 14, and a call signal input from a microphone 21 is compression coded by the audio processing section 14. The audio processing

section 14 subjects a sound or audio signal to high-efficiency compression encoding/decoding, and is implemented by a coder/decoder based on a CELP (Code Excited LPC) method and an ADPCM (Adaptive Differential PCM encoding) method. A hardware tone generator 15 converts the call signal received from the audio processing section 14 into sound to be sounded via a received message speaker 22, or generates an incoming call music or music-on-hold by reproducing the converted hardware tone generator control data. It should be noted that the incoming call music is sounded via an incoming call speaker 23, while the music-on-hold is sounded via the received message speaker 22 after being mixed with the incoming call signal.

[0058] Further, as the format of music contents data, there are employed a MID format and a SMAF format which are convenient to distribution of data, and the CPU 10 converts the music contents data in these formats into hardware tone generator control data having a format specific to the hardware tone generator 15, whereby it is possible to reproduce musical tones based on the data in these formats. The converted hardware tone generator control data can be stored in the RAM 11. The hardware tone generator 15 reproduces musical tones based on the hardware tone generator control data, and to this end, has provided therein a FIFO for temporarily storing a predetermined amount of the hardware tone generator control data. The FIFO may have a storage capacity large enough to store the whole of one musical piece, but if the capacity of the FIFO is not large enough to store the whole music piece, it may be so configured that whenever a predetermined amount of unused area is produced in the FIFO, the hardware tone generator 15 sends a FIFO data request signal to the CPU 10. Responsive to this request signal, the CPU 10 continues to read the following portion of the hardware tone generator data stored in the RAM 11 or ROM 12, and delivers the read data to the hardware tone generator 15. This makes it possible to reproduce a musical piece formed by a large amount of hardware tone generator control data even with a smallcapacity FIFO.

[0059] Further, an interface (I/F) 16 provides interface for downloading music contents data and the like from an external apparatus 20, such as a personal computer. An input section 17 is an input means comprised of dial buttons for inputting "0" to "9", respectively, and other buttons. A display 18 displays a menu of options for selecting telephone functions, and images associated with operations of respective buttons, including the dial buttons. A vibrator 19 vibrates the body of the cellular phone 1 upon receipt of an incoming call in place of generating the incoming call sound. It should be noted that all the components and sections are connected to each other via a bus 24.

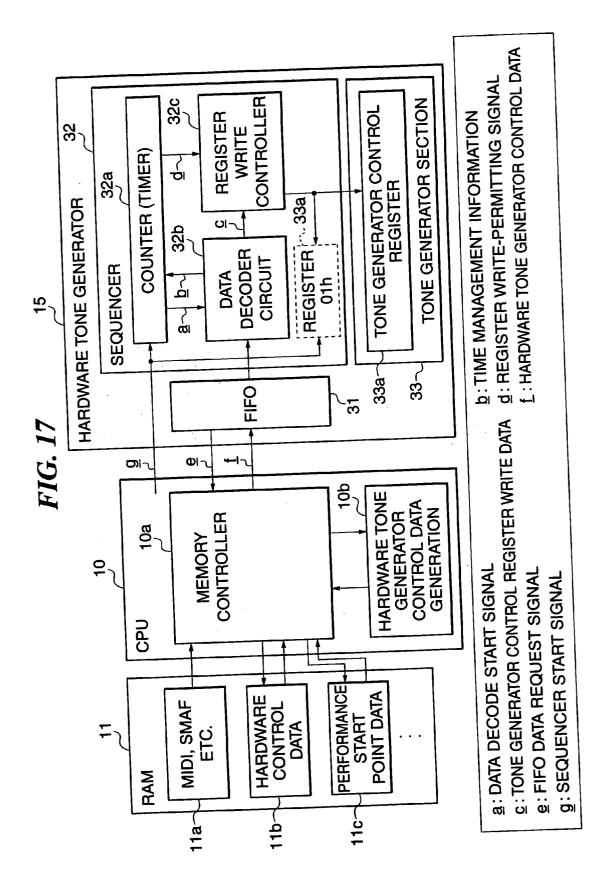

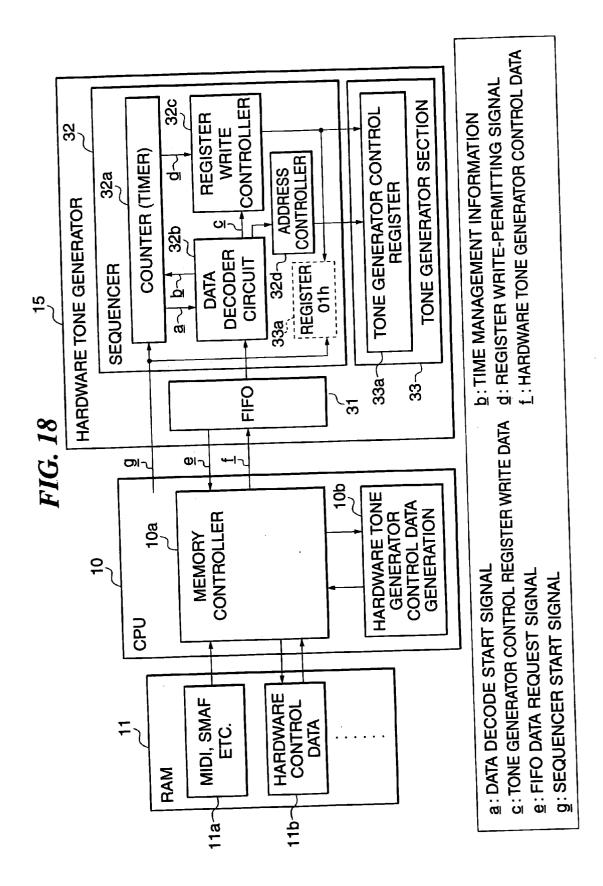

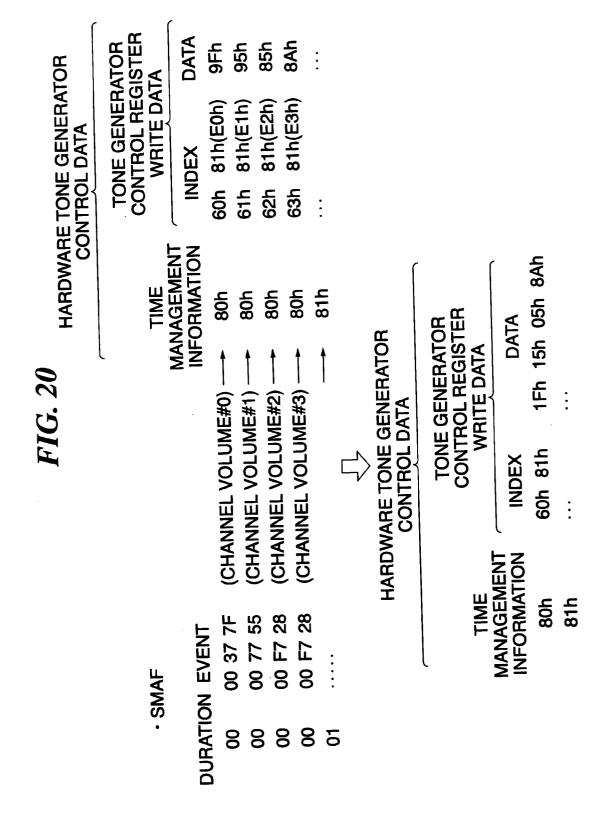

[0060] FIG. 2 shows the construction of the musical tone-generating apparatus according to the first embodiment of the present invention, which is used in the cellular phone 1 as its hardware tone generator 15. In FIG. 2, the received message speaker 22, the incoming call speaker 23, and components associated therewith are omitted. The CPU 10, the hardware tone generator 15, and the RAM 11 are communicated with each other for transfer of data therebetween by the bus 24, though not shown in FIG. 2.

[0061] In the FIG. 2 musical tone-generating apparatus according to the first embodiment, the RAM 11 stores MID

data, SMAF data and the like, formed as files, in an area 11a thereof. Further, when the CPU 10 has extra capability of processing or available processing time, the CPU 10 reads out musical contents data from the area 11a of the RAM 11 and carries out a converting process for converting the read data to hardware tone generator control data, to store the converted hardware tone generator control data in an area 11b of the RAM 11. The area 11a can store musical contents data of a plurality of musical pieces, and the area 11b can also store hardware tone generator control data of a plurality of musical pieces.

[0062] As described above, the CPU 10 reads out musical contents data from the area 11a of the RAM 11 and carries out the converting process for converting the read data to hardware tone generator control data, which is stored in the area 11b of the RAM 11. The converting process is executed by a hardware tone generator control data-generating means **10**b of the CPU **10**, which is implemented by software. When the CPU 10 converts the music contents data to the hardware tone generator control data, a memory controller 10a sequentially reads out music contents data to be converted from the area 11a of the RAM 11 starting from the leading portion of the data, and supplies the read data to a hardware tone generator control data-generating means 10b. The hardware tone generator control data-generating means 10b interprets the supplied music contents data and sequentially converts the same to hardware tone generator control data. The memory controller 10a sequentially writes the hardware tone generator control data thus obtained into the area 11b of the RAM 11. In this way, the CPU 10 converts the music contents data to the hardware tone generator

[0063] It should be noted that when the CPU 10 performs the reproduction of musical tones while executing the data-converting process, the memory controller 10a writes the hardware tone generator control data f thus obtained into a FIFO (First-In First-Out) 31 of the hardware tone generator 15

[0064] The hardware tone generator 15 includes the FIFO 31 capable of storing a predetermined amount of hardware tone generator control data, and a sequencer 32 sequentially reads out the hardware tone generator control data from the FIFO 31. The FIFO 31 is capable of storing e.g. 32 words of the hardware control data, in a First-In First-Out method, i.e. reads out the hardware tone generator control data in the order in which the data were written. When a predetermined amount of unused area occurs in the FIFO 31 as a result of reading of the hardware tone generator control data therefrom, the FIFO 31 sends a FIFO data request signal e to the memory controller 10a of the CPU 10, requesting the following hardware tone generator control data f to be transferred to the FIFO 31. This enables reproduction of a musical piece or pieces of a large amount of hardware tone generator control data by using a FIFO with a small capacity for the FIFO 31.

[0065] The sequencer 32 of the hardware tone generator 15 includes a data decoder circuit 32b, which separates the hardware tone generator control data read out from the FIFO 31 into time management information and tone generator control register write data. In this case, when a time management information-discriminating address is added to the hardware tone generator control data in a position immedi-

ately before the time management information, data, which is one byte, for example, following the time management information-discriminating address is separated as time management information. The remaining part of the hardware tone generator control data other than the time management information-discriminating address and the time management information, that is, tone generator control register write data provides a parameter for generating musical tone, and is written into a tone generator control register 33a of a tone generator section 33 under the control of a register write controller 32c. The register write controller 32c writes the tone generator control register write data into the tone generator control register 33a in timing in which a register write-permitting signal d is outputted. The register write-permitting signal d is outputted in timing in which the count of a counter (timer) 32a becomes equal to a value of duration or a value of gate time contained in the time management information, as will be described herein-

[0066] The counter 32a of the sequencer 32 counts clock pulses output, e.g. at time intervals of 1 millisecond, as reference time units. The counting of the clock pulses is started when a sequencer start signal g output from the CPU 10 is applied to the counter 32a. Further, the sequencer start signal g instructs starting of operation of the sequencer by writing data "01h" into a register 01h arranged within the sequencer 32 of the tone generator control register 33a, to thereby set "1" to a bit D0 (start) thereof. This causes the sequencer 32 to start sequencer processing, and when the counter 32a starts counting, the counter 32a applies a data decode start signal a to the data decoder circuit 32b. The data decoder circuit 32b is responsive to the data decode start signal a to read out hardware tone generator control data from the FIFO 31 and then extracts the time management information therefrom. The extracted time management information b is sent to the counter 32a, and when the count of the counter 32a becomes equal to or larger than the time management information b, the counter 32a applies the register write-permitting signal d to the register write controller 32c to write the tone generator control register write data c extracted by the data decoder circuit 32b into the tone generator control register 33a. This causes the tone generator section 33 to generate musical tones based on the tone generator control register write data c and output the musical tones. Then, the data decoder circuit 32b reads out the next hardware tone generator control data from the FIFO 31.

[0067] Then, the data decoder circuit 32b extracts the next time management information from the read hardware tone generator control data, and the same process as described above is repeatedly carried out. That is, when the count of the counter 32a becomes equal to or larger than the next time management information b, the counter 32a applies the register write-permitting signal d to the register write controller 32c, to write the next tone generator control register write data c extracted by the data decoder circuit 32b into the tone generator control register 33a. This causes the tone generator section 33 to generate musical tones based on the next tone generator control register write data c and output the generated musical tones. Then, the data decoder circuit 32b reads out the second next hardware tone generator control data from the FIFO 31. Thus, the hardware tone generator control data is sequentially read from the FIFO 31, whereby the tone generator 33 reproduces musical tones.

[0068] Next, the operation of the musical tone-generating apparatus shown in FIG. 2 performed in response to an instruction for reproduction will be described.

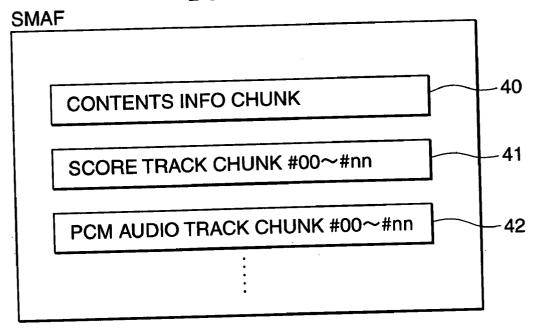

[0069] First, the SMAF format will be described. Data structures of the SMAF format are shown in FIGS. 3A, 3B and 4. As shown in FIG. 3A, the SMAF data has a chunk structure and is comprised of a contents information chunk (Contents Info Chunk) 40, a score track chunk 41, and a PCM audio track chunk 42. The contents information chunk 40 includes information and definitions of the contents, the score track chunk 41 stores a tone generator sequence track, and the PCM audio track chunk 42 stores compressed PCM-type audio sounding data, such as ADPCM data, MP3 (MPEG audio layer 3) data, and TwinVQ data, in the form of events.

[0070] The data structure of the score track chunk 41 is shown in FIG. 3B. As shown in the figure, the score track chunk 41 is comprised of data of a format type, a sequence type, etc., and chunks, such as a setup data chunk 43 and a sequence data chunk 44. The format type data indicates a status of the data in which the actual format of this chunk is defined, and can define the format type as a handy phone standard type, for instance. The sequence type data indicates one of two types of sequence data, i.e. a stream sequencer type and a sub-sequencer type. The setup data chunk 43 stores tone color data, settings of effects and the like, and the sequence data chunk 44 stores sequence data which is real performance data.

[0071] Next, the data structure of the sequence data stored in the sequence data chunk 44 is shown in FIG. 4. As shown in the figure, the sequence data is comprised of pairs of data, each pair formed by one byte of duration data, and two or three bytes of event data, which are arranged in an alternating manner. In this case, the format is configured such that duration data necessarily exists before each event data. The duration data indicates time information indicative of a time interval between the event immediately preceding the duration data and an event immediately following the duration data. Further, the events include a note message for controlling sounding, a control message for controlling a volume, a modulation, and the like, an exclusive message which can carry information peculiar to a maker of the data, etc. Further, the note message is comprised of a channel number indicative of a designated sounding channel, a note number indicative of a tone pitch of a musical tone to be sounded, a gate time indicative of a duration of sounding.

[0072] The FIG. 4 sequence data composed of duration data 1 to duration data 3 and event data 1 to event data 3 can be expressed along the time axis as shown in FIG. 5. Assuming that an event 1, an event 2, and an event 3 are note messages for note on (sounding), the sounding by the event 1 is started upon the lapse of a time period indicated by the duration 1. Further, the sounding by the event is stopped upon the lapse of a time period indicated by the gate time 1 after the start of sounding by the event 1, and then when a time period indicated by the duration 2 has elapsed after the lapse of the time period indicated by the duration 1, the sounding by the event 2 is started. Then, when a time period indicated by the gate time 2 has elapsed after the start of sounding by the event 2, the sounding by the event 2 is stopped. Further, when a time period indicated by the duration 3 has elapsed after the lapse of the time period indicated by the duration 2, the sounding by an event 3 is started. Then, when a time period indicated by the gate time 3 has elapsed after the start of sounding by the event 3, the sounding by the event 3 is stopped. Hereafter, the FIG. 4 sequence data is referred to as the "SMAF data".

[0073] Referring again to FIG. 2, the hardware tone generator control data-generating means 10b converts music contents data, e.g. SMAF data, to hardware tone generator control data. Here, the hardware tone generator control data formed by the conversion is sequentially transferred to the hardware tone generator 15, and the tone generator section 33 generates musical tones based on the hardware tone generator control data. To this end, the hardware tone generator control data is configured to have a data structure adapted to a register map of the tone generator control register 33a of the tone generator section 33. Here, an example of hardware tone generator control data formed by converting the SMAF data is shown. Although the hardware tone generator control data contains time management information corresponding to duration and gate time, the time management information is not written into the tone generator control register 33a. Tone generator control register map-adapted data formed by eliminating the time management information from the hardware tone generator control data is shown in FIG. 6 in a manner associated with the SMAF data before conversion.

[0074] In FIG. 6, duration data "00" and an event "00 30 47" of a program change message of SMAF data are converted to an index "18h" and data "10h". In these data, "h" indicates that the numerical value is in hexadecimal notation. The index designates the address of a register shown in the tone generator control register map of the tone generator control register 33a shown in FIG. 7, and the data following the index is written into a register having the address indicated by the index. In this case, each register has a capacity of one byte, and the tone generator control register 33a has one register to be addressed by an index "01h", eight registers to be addressed by respective indexes "18h" to 1Fh", sixteen registers to be addressed by respective indexes "B0h" to "BFh", sixteen registers to be addressed by respective indexes "C0h" to "CFh", and sixteen registers to be addressed by respective indexes "E0h" to "EFh". It should be noted that only the register "01h" to be addressed by the index "01h" is arranged within the sequencer 32, as shown in FIG. 2. Further, the length of each index is one byte, and hence each register is formed of eight bits, for storing data having the corresponding length of one byte.

[0075] Each of the eight registers to be addressed by the respective indexes "18h" to "1Fh" is used for designating a tone color number of a channel n and a tone color number of a next channel n+1. This enables designation of respective tone colors of sixteen channels. Further, each of the sixteen registers to be addressed by the respective indexes "B0h" to "BFh" stores less significant eight bits of an F number defined in ten bits representative of a numerical value proportional to the frequency of the tone pitch assigned to each key of a keyboard. Further, each of the sixteen registers to be addressed by the respective indexes "C0h" to "CFh" stores the remaining more significant two bits of the F number at respective bits D0 and D1 thereof, three bits defining octave information at respective bits D2, D3, D4 thereof, and key-on information at a bit D5 thereof. This

makes it possible to designate a tone pitch defined by the F number and the octave, and key-on, for each of the sixteen channels. Further, each of the sixteen registers to be addressed by the respective indexes "E0h" to "EFh" stores five bits defining channel volume information at respective bits D0 to D4. Thus, the channel volume information can be designated for each of the sixteen channels.

[0076] Therefore, through conversion of the duration data "00" and the event "00 30 47" of the program change message of SMAF data to the index "18h" and data "10h", the data "10h" is stored in the register 18h, whereby the tone color having the tone color number "01h" is designated for the channel 1, and the tone color having the tone color number "1h" is designated for the channel 2.

[0077] Further, duration data "00" and an event "00 37 7F" of a channel volume message of the next SMAF data are converted to the index "E0h" and data "1Fh". The data "1Fh" formed by the conversion is stored in the register E0h, whereby the data "1Fh" designates the volume value of the channel 1 as "1Fh".

[0078] Further, duration data "00" and an event "2C 50" of a note message of the next SMAF data are converted to the index "B0h" and data "B2h", and the index "C0h" and data "32h". The data "B2h" formed by the conversion is stored in the register B0h, and the data "32h" formed by the conversion is stored in the register C0h. Ten bits formed by 0-th to 8-th bits provided by the data "B2h" ("1010010" in binary notation) and 9-th and 10-th bits at bits D0 and D1 of the data "32h" ("00110010" in binary notation) designates the F number of the channel 1. Further, the three bits "100" at respective bits D2, D3, D4 of the data "32h" designate an octave of the channel 1. Further, "1" at a bit D5 of the data "32h" designates key-on of the channel 1.

[0079] Further, duration data "5C" and an event "2B 20" of a note message of the next SMAF data are converted to the index "B0h" and data "8Bh", and the index "C0h" and data "32h". The data "8Bh" formed by the conversion is stored in the register B0h, and the data "32h" formed by the conversion is stored in the register C0h. Ten bits "1010001011" formed by 0-th to 8-th bits provided by the data "8Bh" ("10001011" in binary notation) and 9-th and 10-th bits at bits D0 and D1 of the data "32h" ("00110010" in binary notation) designate the F number of the channel 1. Further, three bits "100" at bits D2, D3, D4 of the data "32h" designate an octave of the channel 1. Further, "1" at a bit D5 of the data "32h" designates key-on of the channel 1.

[0080] The SMAF data and tone generator control register map-adapted data formed by converting the SMAF data are associated with each other as described above, and the following data are also similarly converted.

[0081] It should be noted that the event "2C 50" of the note message and the event "2B 20" of SMAF data are shown in hexadecimal notation, and "50" and "20" within them are gate time data each indicative of a time period over which the sounding of musical tones is carried out. That is, the sounding by these note messages must be stopped when the reference time of "50h" or "20h" has elapsed. That is, to effect note-off upon the lapse of the reference time of "50h" or "20h" after the sounding was started, there are required duration data set to "50h" or "20h", and a not message instructing key off, with key-on/key-off information being set to "0".

[0082] Such note messages are not shown in FIG. 6, but are automatically generated by the hardware tone generator control data-generating means 10b during the data conversion, through interpretation of SMAF data before the conversion. Therefore, for the help of explanation, a first data structure of the hardware tone generator control data converted from the SMAF data which includes time management information is shown in FIG. 8, and an example of hardware tone generator control data having the first data structure formed by converting the FIG. 6 SMAF data is shown in FIG. 9. Further, the FIG. 9 hardware tone generator control data rearranged in sets of data is shown in FIG. 10.

[0083] As shown in FIG. 8, in the first data structure of the hardware tone generator control data, a time management information-discriminating address and time management information forms a set of data, and the time management information-discriminating address is arranged in a position immediately before the time management information. That is, when the time management information-discriminating address is detected, it is assumed that data following the detected time management information-discriminating address is time management information. Following the time management information, at least one set of data each formed by a pair of an index and data is provided. The index is information, as described hereinabove, which indicates an address of each register provided in the tone generator control register 33a, and the data following the index is written into the register indicated by the address. Further, the timing in which the data is written into the register is designated by the time management information arranged in a position immediately before the at least one pair of the index and data. The hardware tone generator control datagenerating means 10b converts the SMAF data to the hardware tone generator control data shown in FIG. 8.

[0084] FIG. 9 shows the hardware tone generator control data formed by the hardware tone generator control datagenerating means 10b interpreting and converting the FIG. 6 SMAF data. In the FIG. 9 hardware tone generator control data, sequencer terminating data is also added in addition to the time management information. That is, the first data is set to "FFh" defined as the time management informationdiscriminating address, and then time management information "00h" as the duration data follows. The data following the duration data are, as described above, the set of data formed by the pair of the index "18h" and data "10h", the set of data formed by the pair of the index "B0h" and data "B2h" and the pair of the index "C0h" and data "32h", and so forth. This sequence of data designates the tone colors of the channels 1 and 2, and the volume of the channel 1, as well as the key-on and a tone pitch of the channel 1.

[0085] The following data is data, not shown in FIG. 6, for terminating the sounding of musical tones reproduced via the channel 1. The timing of start of the sounding of the channel 1 is set to timing indicated by the time management information "00h" arranged in a position immediately before the sounding data. Then, the sounding is terminated in timing of the lapse of the gate time. In other words, the time management information of data of which the sounding is to be stopped is a data value corresponding to the gate time. That is, the data for terminating the sounding is formed by a set of data formed by a pair of "FFh" as the time management information-discriminating address and time

management information "50h" and a set of data subsequent thereto formed by a pair of the index "B0h" and data "B2h" and a pair of the index "C0h" and data "12h". This data causes the data "B2h" to be stored in the register B0h and the data "B2h" in the register C0h upon the lapse of the reference time "50h", whereby ten bits "1010110010" formed by 0-th to 8-th bits formed by the data "B2h" ("10110010" in binary notation") and 9-th and 10-th bits of "10" at bits D0 and D1 of the data "12h" ("00010010" in binary notation) designate the F number of the channel 1. Further, three bits "100" at bits D2, D3, D4 of the data "12h" designate the octave of the channel 1. Further, "0" at a bit D5 of the data "12h" designates the key-off of the channel 1. This causes the musical tone of the channel 1 being sounded based on the designated octave and F number to be stopped upon the lapse of the reference time "50h".

[0086] The following data are also written in the tone generator control register 33a. At the end of the hardware tone generator control data, there are provided data formed by a pair of the time management information-discriminating address "FFh" and the time management data "00h", and data subsequent thereto which is formed by a pair of the index "01h" and data "00h" ("00000000" in binary notation). In this case, the data "00h" is set to the register 01h of the tone generator control register 33a, which is arranged within the sequencer 32, in timing of the lapse of the reference time "01h" from the occurrence of the immediately preceding event. This sets "0" to the bit D0 (start) of the register 01h shown in FIG. 7, whereby the termination of sequencer operation is instructed to the sequencer 32. In short, the index "01h" and data "00h" form the sequencer terminating data.

[0087] FIG. 10 shows rearrangement of the hardware tone generator control data having the first data structure and formed by the hardware tone generator control data-generating means 10b through interpretation and conversion of the SMAF data, in sets of data. As shown in the figure, the hardware tone generator control data having the first data structure is composed of data each formed by a pair of a time management information-discriminating address and time management information and data each formed by a pair of an index and data. The operation of the FIG. 2 musical tone-generating apparatus performed when reproduction of a musical piece is instructed by designating the hardware tone generator control data thus converted from the SMAF data will be described with reference to FIGS. 2 and 10. It is assumed, however, that the hardware tone generator control data has been converted from the SMAF data by the CPU 10 and the resulting data has been stored in the area 11b of the RAM 11 prior to the reproduction of the musical

[0088] The memory controller 10a of the CPU 10 reads out hardware tone generator control data f shown in FIG. 10 which corresponds to the musical piece designated for reproduction from the area 11b of the RAM 1, e.g. by an amount of 32 bytes, and transfers the same to the FIFO 31 of the hardware tone generator 15. Simultaneously, the CPU 10 supplies the sequencer start signal g to the counter 32a of the sequencer 32.

[0089] Further, the sequencer start signal g is written into the register 01h as part of the tone generator control register 33a to set "1" to the bit D0 (start) thereof, thereby instructing

the sequencer operation to be started. This causes the sequencer 32 to start the sequencer operation, and the counter 32a operates in response to the sequencer start signal g to start counting clocks as units of the reference time, and at the same time applies the data decode start signal a to the data decoder circuit 32b. The data decoder circuit 32b operates in response to the data decode start signal a to read data from the FIFO 31 one byte by one byte. In this case, when the read data is the time management information-discriminating address "FFh", another byte is further read out. As shown in FIG. 10, data following the time management information-discriminating address is time management information, and therefore, this information is set to the counter 32a.

[0090] Further, the data decoder circuit 32b continues to read out the following data from the FIFO 31, and the index "18h" read out and the data "10h" read out in succession thereto are both tone generator control register write data, and hence sent to the register write controller 32c. The register write controller 32c prepares for writing the data "10h" into the register 18h having the address indicated by the index "18h". In this case as well, the time management information set to the counter 32a is "00h", and hence the counter 32a instantly applies the register write-permitting signal d to the register write controller 32c, whereupon, responsive to this signal, the register write controller 32c writes the data "10h" into the register 18h of the tone generator control register 33a. The register 18h designates the tone cooler numbers of the channels 1 and 2, so that the tone colors of the channels 1 and 2 of musical tones generated from the tone generator section 33 are designated.

[0091] Also further, the data decoder circuit 32b continues to read out the following data from the FIFO 31, and the index "E0h" read out and the data "1Fh" read out in succession thereto are both tone generator control register write data, and hence sent to the register write controller 32c. The register write controller 32c prepares for writing the data "1Fh" into the register E0h having the address indicated by the index "E0h". In this case as well, the time management information set to the counter 32a is "00h", and hence the counter 32a instantly applies the register write-permitting signal d to the register write controller 32c, whereupon, responsive to this signal, the register write controller 32cwrites the data "1Fh" into the register E0h of the tone generator control register 33a. The register E0h designates the channel volume of the channel 1, so that the channel volume of the channel 1 of a musical piece generated by the tone generator section 33 is designated.

[0092] Further, the data decoder circuit 32b continues to read out the following data from the FIFO 31, and the index "B0h" read out and the data "B2h" read out in succession thereto are both tone generator control register write data, and hence sent to the register write controller 32c. The register write controller 32c prepares for writing the data "B2h" into the register B0h having the address indicated by the index "B0h". In this case as well, the time management information set to the counter 32a is "00h", and hence the counter 32a instantly applies the register write-permitting signal d to the register write controller 32c, whereupon, responsive to this signal, the register write controller 32c writes the data "B2h" into the register B0h of the tone

generator control register 33a. The register B0h designates the less significant eight bits of the F number of the channel 1.

[0093] Further, the data decoder circuit 32b continues to read out the following data read out from the FIFO 31, and the read index "C0h" and the data "32h" read out in succession thereto are both tone generator control register write data, and hence sent to the register write controller 32c. The register write controller 32c prepares for writing the data "32h" into the register C0h having the address indicated by the index "C0h". In this case as well, the time management information set to the counter 32a is "00h", and hence the counter 32a instantly applies the register write-permitting signal d to the register write controller 32c, whereupon, responsive to this signal, the register write controller 32c writes the data "32h" into the register C0h of the tone generator control register 33a. The register C0h designates an octave in cooperation with the more significant two bits of the F number of the channel 1, and at the same time designates the key-on/key-off of the channel 1, and "1" is set to a bit D5 thereof (D5=1) to designate the key-on, whereby the key-on of the channel 1 is designated, to start generation of a musical tone with the tone pitch of the octave and F number, the volume, and the tone color, which are set in the tone generator control register 33a.

[0094] Then, the data decoder circuit 32b reads out the following data from the FIFO 31, and the data read out is time management information-discriminating address "FFh", and hence the time management information "50h" read out in succession thereto is set to the counter 32a as the time management information b. The data decoder circuit 32b reads out the following data from the FIFO 31, and the data read out is the index "B0h", which is tone generator control register write data, and hence sent to the register write controller 32c together with the data "B2h" read out in succession thereto. The register write controller 32c prepares for writing the data "B2h" into the register B0h having the address indicated by the index "B0h". In this case, the time management information set to the counter 32a is "50h", and hence the process waits for the counter 32a to count up to a value corresponding to "50h".

[0095] Then, the data decoder circuit 32b reads out the following data from the FIFO 31, and the data read out is the index "C0h", which is tone generator control register write data, and hence sent to the register write controller 32c together with the data "12h" read out in succession thereto. The register write controller 32c prepares for writing the data "12h" into the register C0h having the address indicated by the index "C0h". In this case, the time management information set to the counter 32a is "50h", and hence the process waits for the counter 32a to count up to the value corresponding to "50h". Then, the counting of the counter 32a progresses, and in timing a time period corresponding to "50h" has elapsed (time point 50h), the counter 32a applies the register write-permitting signal d to the register write controller 32c, whereupon, responsive to this signal, the register write controller 32c writes the data "B2h" into the register B0h of the tone generator control register 33a, and at the same time writes the data "12h" into the register C0h. The register B0h designates the less significant eight bits of the F number of the channel 1, while the register C0h designates an octave in cooperation with the more significant two bits of the F number of the channel 1, and at the same time designates the key-on/key-off of the channel 1, by the bit D5 thereof. In the present case, "0" is set to the bit D5 (D5=0) of the register C0h to designate the key-off. This instructs the key-off of the musical tone of the channel 1 being generated by the tone generator section 33 with the tone pitch of the designed octave and F number, thereby stopping the generation of the musical tone.

[0096] When the count of the counter 32a becomes equal to or larger than the value corresponding to "50h", the data decoder circuit 32b reads out the following data from the FIFO 31. The read data is time management informationdiscriminating address "FFh", and hence the time management information "0Ch" read out in succession thereto is set to the counter 32a as the time management information b. The data decoder circuit 32b reads out the following data from the FIFO 31, and the data read out is the index "B0h", which is tone generator control register write data, and hence sent to the register write controller 32c together with the data "8Bh" read out in succession thereto. The register write controller 32c prepares for writing the data "8Bh" into the register B0h having the address indicated by the index "B0h". In this case, the time management information set to the counter 32a is "0Ch", and hence the process waits for the counter 32a to count up to a value corresponding to "0Ch".

[0097] Then, the data decoder circuit 32b reads out the following data from the FIFO 31, and the data read out is the index "C0h", which is tone generator control register write data, and hence sent to the register write controller 32c together with the data "32h" read out in succession thereto. The register write controller 32c prepares for writing the data "32h" into the register C0h having the address indicated by the index "C0h". In this case, the time management information set to the counter 32a is "0Ch", and hence the process waits for the counter 32a to count up to a value corresponding to "0Ch". Then, the counting of the counter 32a proceeds, and in timing a time period corresponding to "0Ch" has elapsed from the time point "50h" (time point 5Ch (=50h+0Ch)), the counter 32a applies the register write-permitting signal d to the register write controller 32c, whereupon, responsive to this signal, the register write controller 32c writes the data "8Bh" into the register B0h of the tone generator control register 33a, and at the same time writes the data "32h" into the register C0h of the same. The register B0h designates the less significant eight bits of the F number of the channel 1, while the register C0h designates an octave in cooperation with the more significant two bits of the F number of the channel 1, and at the same time designates the key-on/key-off of the channel 1. In this case, "1" is set to the bit D5 (D5=1) of the register C0h to designate the key-on. This instructs the key-on of the musical tone of the channel 1, whereby the key-on of the channel 1 is designated, to start generation of a musical tone with the tone pitch of the octave and F number, the volume, and the tone color, which are set in the tone generator control register 33a.

[0098] Then, the data decoder circuit 32b continues to read out the following data from the FIFO 31. The read data is the time management information-discriminating address "FFh", and hence the time management information "20h" read out in succession thereto is set to the counter 32a as the time management information b. Then, the data decoder circuit 32b reads out the following data from the FIFO 31, and the data read out is the index "B0h", which is tone

generator control register write data, and hence sent to the register write controller **32**c together with the data "8Bh" read out in succession thereto. The register write controller **32**c prepares for writing the data "8Bh" into the register B0h having the address indicated by the index "B0h". In this case, the time management information set to the counter **32**a is "20h", and hence the process waits for the counter **32**a to count "20h".

[0099] Then, the data decoder circuit 32b reads out the following data from the FIFO 31, and the data read out is the index "C0h", which is tone generator control register write data, and hence sent to the register write controller 32c together with the data "12h" read out in succession thereto. The register write controller 32c prepares for writing the data "12h" into the register C0h having the address indicated by the index "C0h". In this case, the time management information set to the counter 32a is "20h", and hence the process waits for the counter 32a to count up to the value corresponding to "20h". Then, the counting of the counter 32a progresses, and in timing the time period corresponding to "20h" has further elapsed (time point 7Ch (=5Ch+20h)), the counter 32a applies the register write-permitting signal d to the register write controller 32c, whereupon, responsive to this signal, the register write controller 32c writes the data "8Bh" into the register B0h of the tone generator control register 33a, and at the same time writes the data "12h" into the register C0h of the same. The register B0h designates the less significant eight bits of the F number of the channel 1, while the register C0h designates an octave in cooperation with the more significant two bits of the F number of the channel 1, and at the same time designates the key-on/keyoff of the channel 1. In the present case, "0" is set to the bit D5 (D5=0) thereof to designate the key-off. This instructs the key-off of the musical tone of the channel 1 being generated by the tone generator section 33 with the tone pitch of the designated octave and F number, thereby stopping the generation of the musical tone.

[0100] Hereafter, data are read out one byte by one byte, and similar processing is carried out. Finally, an index "01h" and the following data "00h" are read out from the FIFO 31. Prior to the reading of these data, the time management information-discriminating address "FFh" and time management information "01h" are read out from the FIFO 31. The time management information "01h" is set to the counter 32a as the time management information k, and the index read out in succession thereto is sent to the register write controller 32c as the tone generator control register write data c. Further, the data decoder circuit 32b sends the data "00h" read out next to the register write controller 32c. The register write controller 32c prepares for writing the data "00h" ("00000000" in binary notation) to the register 01h having the address indicated by the index "01h". In this case, the time management information set to the counter 32a is "01h", and hence the process waits for the counter 32a to count up to the value corresponding to "01h". The counting of the counter 32a progresses and in timing the time period corresponding to "01h" has elapsed, the counter 32a applies the register write-permitting signal d to the register write controller 32c, whereupon, responsive to this signal, the register write controller 32c writes the data "00h" into the register 01h arranged in the sequencer 32. The bit D0 of the register 01h instructs the start/stop of the operation of the sequencer 32, and in this case, "0" is set to the bit D0 of the register 01h (D0=0) to designate the stop of operation of the sequencer 32. This instructs the sequencer 32 to terminate its operation, whereby the sequencer 32 stops its operation. As described above, this pair of data, index "01h" and "00h", is the sequencer terminating data.