# UM0225 User manual

## Configuration and programming software (CAPS) tool for STR9 families

## Introduction

Configuration and Programming Software (CAPS) is the configuration software for the STR9 family microcontroller. The CAPS configuration tool allows you to easily configure the STR9 using simple dragand-drop and point-and-click operations. CAPS also supports In-System-Programming through an external JTAG adapter, allowing fast In-System-Programming of the STR9 in both development and production environments.

This is the CAPS user manual, describing CAPS software functionality. When working with the CAPS tool, you are also encouraged to download the datasheet associated with your particular device; the datasheet may provide the only source of important configuration information needed for your design.

*Getting started* gives an introduction to CAPS installation procedures and hardware requirements. Although installation may seem trivial, it is highly recommended that you carefully follow: the instructions because many problems are often caused by incorrectly installing CAPS.

This is followed by *Introduction to the CAPS user interface*, which describes garanal CAPS usability and the design process.

The *Designing with CAPS* section gives detailed information about each CAPS feature.

The appendices provide reference material useful for design and analysis.

57

| 1              | Gettin | ig starte  | ed                                       | 3   |

|----------------|--------|------------|------------------------------------------|-----|

|                | 1.1    | Installati | ion                                      | 3   |

|                |        | 1.1.1 5    | System requirements                      | . 3 |

|                |        | 1.1.2 l    | nstalling CAPS                           | . 3 |

|                |        | 1.1.3 L    | Jninstalling CAPS                        | . 4 |

|                | 1.2    | Setting (  | up the target hardware                   | 4   |

|                | 1.3    | How to u   | use this manual                          | 5   |

|                | 1.4    | Recomn     | nended reading                           | 5   |

| 2              | Introd | uction     | to the CAPS user interface               | 6   |

|                | 2.1    | Project of | development                              | 6   |

|                | 2.2    | The use    | r interface                              | 6   |

|                |        | 2.2.1 T    | Гhe project menu                         | . 8 |

|                |        | 2.2.2 T    | The tools menu                           | 10  |

|                |        | 2.2.3 T    | The view menu                            | 11  |

|                |        | 2.2.4 T    | a project                                | 11  |

|                | 2.3    | Starting   | a project                                | 12  |

|                |        | 2.3.1 0    | Creating a new project                   | 12  |

|                |        |            | Dening an existing project               |     |

| 3              | Desig  | ning wi    | th CAPS                                  | 15  |

|                | 3.1    | Design f   | flow                                     | 16  |

|                |        | 3.1.1 N    | Manage Project dialog                    | 16  |

|                |        | 3.1.2 D    | Design entry forms                       | 17  |

|                |        | 3.1.3 A    | Additional settings form                 | 17  |

|                |        | 3.1.4 F    | Program device form                      | 18  |

|                | 3.2    | Specifyi   | ng the LVD voltage                       | 18  |

|                | 3.3    | Specifyi   | ng the clock source and frequency        | 19  |

| ~C             |        | 3.3.1 5    | Selecting the clock source and frequency | 19  |

| 205            |        | 3.3.2 5    | Specifying the clock divisor             | 22  |

| 0 <sup>v</sup> |        | 3.3.3 5    | Saving the clock settings                | 23  |

|                | 3.4    | Specifyi   | ng peripheral and GPIO pin assignment    | 24  |

|                | 3.5    | View the   | e GPIO pin assignment summary            | 29  |

|                | 3.6    | Configu    | ring optional device parameters          | 31  |

|                |        | 3.6.1 5    | Setting security                         | 32  |

|                |        | 3.6.2 F    | Power-up boot flash selection            | 32  |

|                |        |            |                                          |     |

| 3.6.3 Setting a JTAG/ISP user code           | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.6.4 Setting sector protection              | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.6.5 Firmware placement                     | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.6.6 Setting OTP programmable memory bytes  | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Validating and programming the target device | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.7.1 JTAG-ISP operations                    | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.7.2 Checksum the programming file          | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.7.3 Generate ATE file                      | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.7.4 Target hardware verification           | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.7.5 Chaining multiple devices              | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

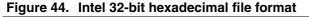

| Intel hex-32 record format                   | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Data record                                  | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| End record                                   | 5. 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Extended linear address record               | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DIO                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Project Report                               | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| HAL library C-header file example            | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| FlashLINK Cable – Install fast JTAG driver   | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Driver installation                          | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Driver installation                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                              | 3.6.4       Setting sector protection         3.6.5       Firmware placement         3.6.6       Setting OTP programmable memory bytes         Validating and programming the target device         3.7.1       JTAG-ISP operations         3.7.2       Checksum the programming file         3.7.3       Generate ATE file         3.7.4       Target hardware verification         3.7.5       Chaining multiple devices         Intel hex-32 record format       Intel hex-32 record format         Data record       Extended segment address record         Extended linear address record       Intel hex record         HAL library C-header file example       Intel hex record |

#### Getting started 1

Before using CAPS, install the software on your PC. Connect your target device, if you plan to program the device.

This section discusses the following topics needed to begin using the CAPS software.

- CAPS software installation.

- Setting up the target hardware.

- The recommended approach to using this manual.

- Complementary documentation considered to be useful when using the CAPS software.

#### 1.1 Installation

This section describes the requirements and procedures needed to install the CAPS software.

#### 1.1.1 System requirements

The CAPS PC configuration minimally requires:

- PC with an Intel Pentium processor running a 32-bit Microsoft operating system: soleteP

- Microsoft Windows XP

- Windows 2000

- Windows 98

- Windows ME

- Windows NT with Service Pack 6

- 32 MB RAM

- 25 MB hard disk space available

- To use RLINK-ST, a USB port is required with a USB-supporting Windows operating system; Note: e.g., Win98SE, Win2000, Me and XP. (Note that Win95, Win98 First Edition and NT4.0 do NOT support USB).

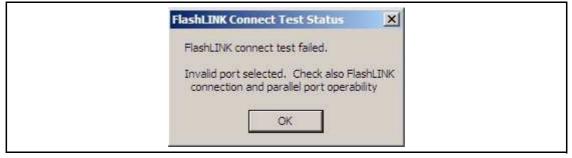

- Caution: FlashLINK Cable: JTD driver (OD) is NOT supported on dual-processor systems or hyperthreading enabled systems. Refer to Appendix D: FlashLINK Cable - Install fast JTAG driver, for workaround options for both dual-processor and hyperthreading systems.

#### Installing CAPS 1.1.2

Follow these procedures and the on-screen instructions to install CAPS.

- Download the compressed CAPS software from the website. 1.

- 2. Extract the contents of the .zip file into a temporary directory.

- Double-click the extracted executable, setup.exe, to initiate the installation, and follow the 3 on-screen prompts to install CAPS in the development environment. This executable installs all the necessary files and configures the PC environment for running CAPS. You may be prompted to restart your PC before running CAPS for the first time following the installation.

CAPS installation includes a number of utilities. Documentation for the utilities is located in the subdirectory \Docs where CAPS is installed.

| Utility Executable | Description                                                                    |  |

|--------------------|--------------------------------------------------------------------------------|--|

| ObjFileEditor.exe  | Programming data file (.OBJ) editor.                                           |  |

| uFLink.exe         | Standalone JTAG/ISP programming utility.                                       |  |

| uMerge.exe         | Merge firmware utility.                                                        |  |

| uObjOsf.exe        | Program data file conversion utility. Convert obj-to-osf and osf-to-obj files. |  |

Table 1.CAPS utility programs

Subdirectory *Projects* is also created, and is the default location for storing your CAPS project files. For example, if CAPS is installed in base directory *C*:\*CAPS*, the *Projects* directory is located at *C*:\*CAPS*\*Projects*.

### 1.1.3 Uninstalling CAPS

To uninstall CAPS, select **Start | Programs | STMicroelectronics - CAPS | Uninstall CAPS**. This removes all CAPS executable software and desktop references.

Note: Any project files and environment files are preserved so they are available following a CAPS software upgrade. However, it is a safe practice to backup your project files before uninstalling and reinstalling the software.

## 1.2 Setting up the target hardware

If you are using CAPS features that interact with the target hardware, such as programming the flash, configure and power the target hardware before starting a CAPS session. (Refer to the the User Guide for your particular target hardware, found at http://www.st.com/mcu/).

- Note: 1 When using FlashLINK, the 20-pin to 14-pin adapter (provided with the EVAL Kit or a customer board) is required.

- 2 The device under test must be the same as the target device you select when you created your project.

- *3* Follow the instructions below referring to the device-specific quick start guide or design guide as needed.

- 1. Connect either the RLINK-ST USB cable or the FlashLINK parallel cable to your PC, and connect the other end of the JTAG interface to the target board.

- 2. Configure jumpers according to the quick start or design guide documentation for the target board.

- Attach the power plug to the power jack of the target board.

- . Switch ON the target board.

## **1.3** How to use this manual

Use these recommendations as a guide to learning the CAPS software.

- Read *Getting started* to learn what CAPS is and to install the software for the first time.

- Read *Introduction to the CAPS user interface* for a basic understanding of the CAPS user interface. More advanced users may skip this section.

- For a detailed discussion of how to use CAPS features, read *Designing with CAPS*.

## 1.4 Recommended reading

You are encouraged to download the datasheet associated with a particular device. The datasheet may be the only source of important configuration information needed for your design. obsolete Product(s) - Obsolete Product(s)

#### 2 Introduction to the CAPS user interface

This section introduces you to the following CAPS topics:

- Project development steps and considerations. •

- A reference for the CAPS user interface.

- Beginning steps needed to start a project.

#### 2.1 Project development

The CAPS software guides the designer through the process of configuring a target device for a particular application, using the following project development steps.

- 1. Create a unique project for each device under test/application combination.

- 2. Configure voltage, clock source, peripheral and GPIO pins, and hardware and firmware parameters. Productls

- 3. Merge the design with your Intel hex-format firmware file.

- 4. Program the resulting programming data file into your device.

- 5. Save your project to a file for later use.

#### 2.2 The user interface

This section is a reference for the CAPS user interface. To learn how to begin using the interface to work with a project, see Starting a project.

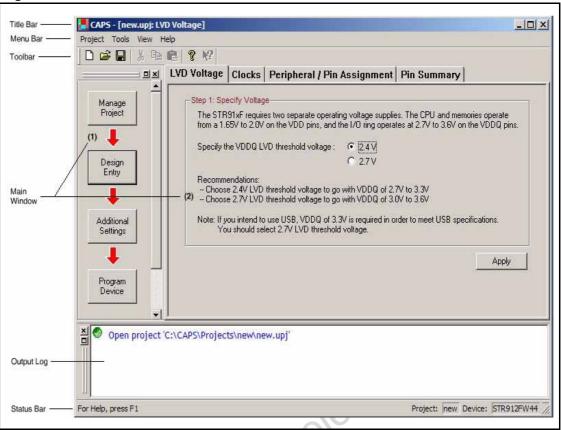

Figure 1: CAPS user interface shows the basic CAPS user interface components, followed by a brief description of each component. Following sections describes the menu bar in more detail. Specific functionality is described in Designing with CAPS.

The CAPS software is a Windows-based program. As such, the user interface implements uon duk obsolete Produk basic interface conventions commonly found in Windows programs.

Toolbar Produk Sosolete Use the menu bar to access these CAPS design functions: *The project menu, The tools menu, The view menu* and *The help menu.* (These functions are described in more detail beginning with *2.2.1: The project menu.*

The toolbar provides quick access to common menu bar functions, including:

- Create a new project.

- Open an existing project.

- Save a project.

- File editing functions: cut, copy and paste.

- Help using CAPS.

| Main window       |       | The main window displays the CAPS design entry forms.<br>The window may consist of multiple panes, depending on<br>the current design function.                          |

|-------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   |       | <i>Figure 1: CAPS user interface</i> shows an example of a typical design window with two panes.                                                                         |

|                   |       | 1. A navigation pane appears on the left.                                                                                                                                |

|                   |       | 2. A current work pane appears on the right.                                                                                                                             |

|                   |       | Some modes of operation may also have function tabs across the top of the work window, as shown in <i>Figure 1</i> .                                                     |

| Output log window |       | The output log window echoes all commands executed by CAPS along with informational and progress messages.                                                               |

|                   | Note: | This window is made visible by checking the Output Log option in the View menu.                                                                                          |

| Status bar        |       | <ul> <li>The status bar displays:</li> <li>Current project name.</li> <li>Target device.</li> <li>Today's date. (MM/DD/YYYY)</li> <li>Current time (HH:MM:SS)</li> </ul> |

|                   |       | *6                                                                                                                                                                       |

The CAPS user interface provides the following additional aids to using the software.

- Descriptive pop-up error messages.

- Explicit design flow sequencing that models the actual design process.

- Detailed directions on most forms that describe input field formats and how to use the form.

## 2.2.1 The project menu

The project menu allows users to manage the project life cycle, set project preferences and exit the CAPS program.

This section describes the operations available in the project menu.

Γ

|      | E                    | CAPS - [new.upj: Pin Summary] Project Tools View Help                                                                                                                                                                                              |

|------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                      | New Project Open Project Close Project                                                                                                                                                                                                             |

|      |                      | Save Project<br>Save As Project                                                                                                                                                                                                                    |

|      |                      | Change Target Device                                                                                                                                                                                                                               |

|      |                      | Delete Project                                                                                                                                                                                                                                     |

|      |                      | Import PSDsoft Project                                                                                                                                                                                                                             |

|      | -                    | Recent Projects                                                                                                                                                                                                                                    |

|      |                      | Preference                                                                                                                                                                                                                                         |

|      |                      | About                                                                                                                                                                                                                                              |

|      | r                    | Exit CAPS                                                                                                                                                                                                                                          |

|      | New Project          | Creates a new project.                                                                                                                                                                                                                             |

|      | Open Project         | Opens an existing project.                                                                                                                                                                                                                         |

|      | Close Project        | Closes the currently active project. Other projects previously opened within the same CAPS session remain open.                                                                                                                                    |

|      | Save Project         | Saves the currently active project.                                                                                                                                                                                                                |

|      | Save as Project      | <ul> <li>Saves the currently active project to a different file name.</li> <li>Follow these steps in the displayed dialog box:</li> <li>1. Enter the new project name (see 2.3.1: Creating a new project for project name constraints).</li> </ul> |

|      | 0100                 | 2. Optionally, enter or modify the project description                                                                                                                                                                                             |

|      | der.                 | 3. Click the <b>Save</b> button.                                                                                                                                                                                                                   |

| 0050 | Change Target Device | Selects another target device ONLY within the same product family, from the expandable device tree list.                                                                                                                                           |

| 00-  |                      | Changing the package type may invalidate the pin function re-assignment done in the <b>Peripheral/Pin Assignment</b> window.                                                                                                                       |

|      | Delete Project       | Deletes a project and all files associated with the project.                                                                                                                                                                                       |

|      |                      |                                                                                                                                                                                                                                                    |

57

| Import PSDsoft Project<br>Note: | Imports an existing project created using the PSDsoft tool. This option is only applicable to $\mu$ PSD projects.                                                                                                                              |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Recent Projects                 | Lists the most recently opened projects. A project may be opened by double-clicking on a list entry.                                                                                                                                           |

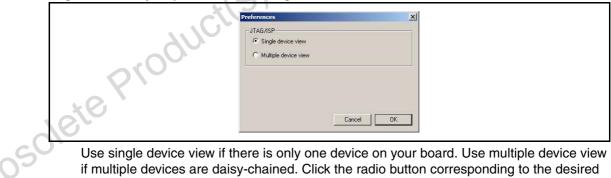

| Preference                      | Sets the CAPS design environment. Select either "Single device view" or "Multiple Device view" for the JTAG/ISP property. Single and multiple device operations are discussed in <i>3.7: Validating and programming the target device</i> .    |

| About<br>Note:                  | <ul> <li>Displays details about a project:</li> <li>Project name.</li> <li>Project folder.</li> <li>Device family.</li> <li>Part number.</li> <li>Voltage.</li> <li>Project description.</li> <li>The project must already be open.</li> </ul> |

| Exit CAPS                       | Exit the CAPS program.                                                                                                                                                                                                                         |

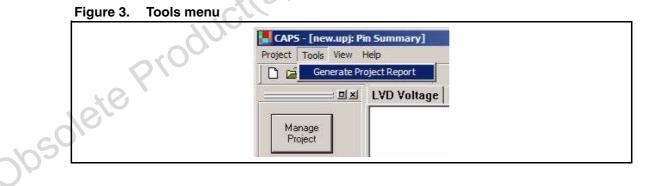

### 2.2.2 The tools menu

The tools menu provides the ability to produce a project report.

**Generate Project Report**

Produces a text file report of your design.

The result shows detailed peripheral and pin function assignments.

See *Project Report* for an example.

1C)

### 2.2.3 The view menu

The view menu selection allows the user to toggle the user interface panes to be displayed while working on a project. Check the menu item to enable the display.

This section describes the operations available in the view menu.

#### Figure 4. View menu

| Project Tools     | View Help                                                                    |

|-------------------|------------------------------------------------------------------------------|

| D 📽 🖬  <br>       | <ul> <li>✓ Design Flow</li> <li>✓ Output Log</li> <li>Full Screen</li> </ul> |

| Manage<br>Project | <ul><li>✓ Toolbar</li><li>✓ Status Bar</li></ul>                             |

| Design Flow | Display the CAPS design flow pane.                                                                                                                   |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output Log  | Display the output log pane that shows commands executed by CAPS, and informational and status messages (See <i>Figure 1: CAPS user interface</i> ). |

| Full Screen | Maximize the CAPS display interface on the screen.                                                                                                   |

| Toolbar     | Display the toolbar (See Figure 1: CAPS user interface).                                                                                             |

| Status Bar  | Display the status bar (See <i>Figure 1: CAPS user interface</i> ).                                                                                  |

## 2.2.4 The help menu

The help menu provides access to various links to obtain technical information about ST Microelectronics microcontroller products and to report questions or issues related to CAPS.

This section describes the operations available in the help menu.

| oject View | Help          |                                    |      |

|------------|---------------|------------------------------------|------|

| 🗅 🗃 🖬      | Web Sites 🔹 🕨 | Home Page                          | ×    |

|            | About CAPS    | CAPS Update                        |      |

|            |               | Related Documentation and Software | uPSD |

|            |               | FAQs                               | STR9 |

|            |               | Forums                             |      |

Web SitesDisplays links to obtain technical information about ST<br/>Microelectronics microcontroller products and to report<br/>questions or issues regarding CAPS. A link to Frequently<br/>Asked Questions (FAQs) is also provided. (See Figure 5.:<br/>Help menu for a list of the links provided).About CAPS ...Displays CAPS software version, copyright, contact and<br/>licensing information.

## 2.3 Starting a project

Every CAPS session begins by opening a project. You may either create a new project or open an existing project.

This section describes the basic steps common to all projects.

### 2.3.1 Creating a new project

1.

Follow these steps to create a new project.

- Use either the **New** icon in the toolbar or the **Project** | **New Project** ... menu item (*Figure 2.: Project menu*) to create a new project.

- 2. Enter an optional project description in the *Description* text box.

- 3. In the *Create Project* dialog, use the **Browse** button to specify the name of your project and directory where the project files are to be created. (The default project name is *new.upj* and the default directory is *c:\CAPS\Projects\new*). The project name is the same as the directory name).

- 4. To accept the default project name and directory, click **Open** in the file browser dialog. To choose another directory, use the file browser to navigate to the desired directory. Then,

either use the default *Project Name* or enter a new name for your project. After a new directory and project name are entered, click **Open**.

Note: A project is saved to disk only after choosing one of the **Save** project menu options.

A valid project name,

- Can have a maximum number of 45 characters.

- Must begin with an alphanumeric character, an underscore (\_) or a tilde (~). Names are not case-sensitive.

- Cannot include symbols or punctuation marks.

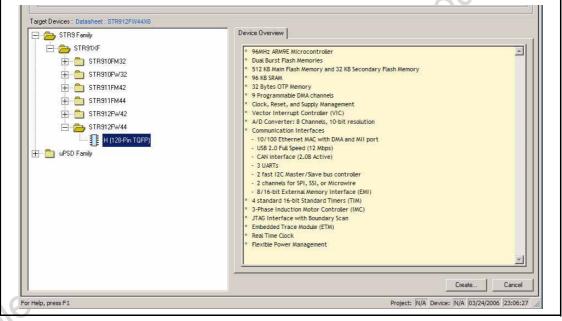

- 5. For new projects, a target device must also be specified. Using the device list tree in the *Target Devices* dialog, expand the tree until your target device appears, then click on the device icon. A description of the device appears in the *Device Overview* window to the right, and the name of the datasheet associated with the device appears in the *Target Devices* line, above the device selection tree.

Available devices include all devices currently supported by CAPS software.

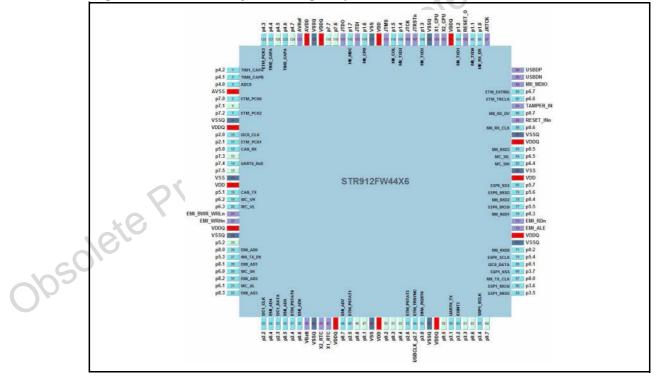

*Figure 6.: Target device selection example* shows an example in which the 128-pin STR912FW44 device is selected.

## 2.3.2

## Opening an existing project

Follow these steps to open an existing project.

- 1. Use either the **Open** icon in the toolbar or the **Project** | **Open Project** ... menu item (*Figure 2.: Project menu*) to open an existing project.

- 2. In the Open Project dialog, use the **Browse** button to use the file browser to locate the directory where your existing project file resides. The dialog displays the project file names with extension *.upj*, as shown in *Figure 7.: Open an existing project example*. Click on the desired file name, then click **Open** to open the file to display your previously saved project.

|       |                       | Open<br>Look in: |                                                                   |

|-------|-----------------------|------------------|-------------------------------------------------------------------|

|       |                       | File name:       | new.upj Open                                                      |

|       |                       | Files of type:   | CAPS Files (*.upj)                                                |

| Note: | You may e<br>changed. | dit the projec   | ct description, however, notice that the target device may not be |

|       |                       |                  | lete Pro                                                          |

|       |                       |                  | 005010                                                            |

|       |                       |                  | (ct(S)                                                            |

|       |                       | Ploq,            |                                                                   |

| 0050  | lete                  |                  |                                                                   |

|       |                       |                  |                                                                   |

Figure 7. Open an existing project example

# **3 Designing with CAPS**

This section provides a detailed description of how to use CAPS features, including:

- The design flow model that guides you through the design process.

- Firmware placement.

- Specifying peripheral and GPIO pin function assignment.

- Setting security.

- Setting JTAG/ISP parameters.

- Setting sector protection.

- Validating and programming the target device.

From the window used to create a new project, click the **Create** button to begin designing a project, as shown in *Figure 8.: Create a project dialog*.

Figure 8. Create a project dialog

| STR9 Family | Device Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STR91XF     | <ul> <li>96MHz ARM9E Microcontroller</li> <li>Dual Burst Flash Memory and 32 KB Secondary Flash Memory.</li> <li>96 KB SRAM.</li> <li>32 Bytes OTP Memory.</li> <li>9 Programmable DMA channels</li> <li>Clock, Reset, and Supply Management.</li> <li>Vector Interrupt Controller (VIC).</li> <li>A/D Converter: 8 Channels, 10-bit resolution.</li> <li>Commincation Interfaces.</li> <li>10/100 Ethernet MAC with DMA and MII port.</li> <li>USB 2.0 Full Speed (12 Mbps).</li> <li>CAIN Interface (2.08 Active).</li> <li>3 UARTS.</li> <li>2 fast 12C Master/Slave bus controller.</li> <li>8 (16-bit External Memory Interface (EMI).</li> <li>4 standard 16-bit Standard Timers (TIM).</li> <li>3 "Fhase Induction Motor Controller (IMC).</li> <li>3 JTAG Interface with Boundary Scan.</li> <li>Embedded Trace Module (ETM).</li> <li>Real: Time Clock.</li> </ul> |

|             | Create Cancel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Project names must be unique. Otherwise, CAPS displays the error message shown in *Figure 9.: Create project dialog error*.

Figure 9. Create project dialog error

| CAPS | ×                                                                                |  |

|------|----------------------------------------------------------------------------------|--|

| 8    | A project name entered already exists.<br>Please enter a different Project name. |  |

|      | OK                                                                               |  |

Click **OK** and enter a different project name to continue.

## 3.1 Design flow

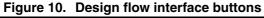

The CAPS design flow interface models the typical steps used in the design process. These steps have corresponding navigation buttons, shown in the left frame of the main window, as shown in *Figure 10: Design flow interface buttons*.

The red arrow indicates the next action to be performed in the design process.

Click the button corresponding to the desired design and programming operation.

- Manage Project

- Design Entry

- Additional Settings

- Program Device

## 3.1.1 Manage Project dialog

Click the **Manage Project** button to access the project management functions listed below. Invoke the function by clicking the radio button associated with the function, then click **OK**.

Create a new project

Select this option to create a new project for your design.

Open an existing project

Select this option to open a project that you have previously created.

| Save current opened project to a different name | Select this option to rename the current project.<br>The project with the new name becomes the<br>currently active project. |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Delete an existing project                      | Select this option to delete a project and all of its associated files.                                                     |

| Close current opened project                    | Select this option to close the currently active project.                                                                   |

#### **Design entry forms** 3.1.2

Use one or more of the design entry forms for CAPS design. These forms are accessed by clicking the **Design Entry** button, then selecting the appropriate tab:

| LVD Voltage               | Use this form to choose the desired voltage specification option. See <i>Specifying the LVD voltage</i> for a detailed discussion on using this feature.                                                           |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clocks                    | Use this form to choose the desired clock source option. See <i>Specifying the clock source and frequency</i> for a detailed discussion on using this feature.                                                     |

| Peripheral/Pin Assignment | Use this form to select the desired peripheral for<br>your design and its pin function assignment. See<br><i>Specifying peripheral and GPIO pin assignment</i><br>for a detailed discussion on using this feature. |

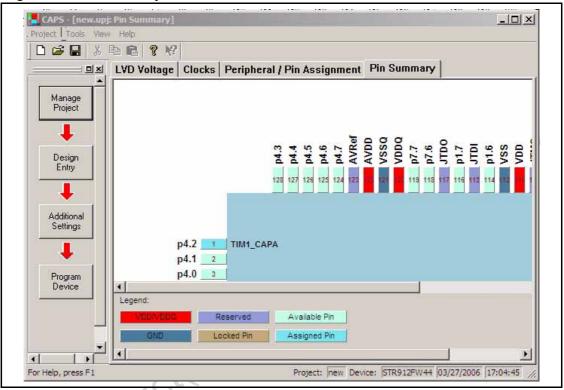

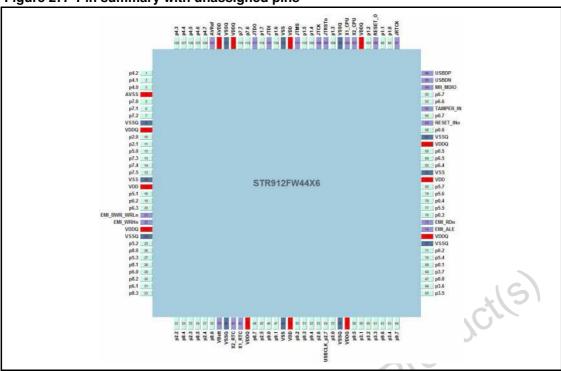

| Pin Summary               | Use this form to graphically display the results of                                                                                                                                                                |

Pin Summary

Additional settings form 3.1.3

> Optional configuration choices are available by clicking on the design flow Additional Settings button, then clicking the **Configuration** tab.

your Peripheral/Pin Assignment operations.

#### Configuration

Use this form for additional design settings, including setting security, selecting the power-up boot flash, specifying a user code, setting the internal memory sector protection, specifying OTP memory programming, and your firmware placement information.

#### 3.1.4 **Program device form**

Click the **Program Device** design flow button to program your design into the target device. Options are also available to calculate the file checksum, generate an SVF or JAM file, and validate the target device. See *Validating and programming the target device* for a detailed description on using this feature.

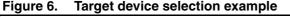

## 3.2 Specifying the LVD voltage

Click the LVD Voltage tab to select the LVD threshold voltage.

The STR91x requires separate operating voltage supplies. The CPU and memory operate from at 1.65 to 2.0 volts on the VDD pins, and the I/O ring operates at 2.7 to 3.6 volts on the VDDQ pins

- Note: 1 Choose 2.4 volts LVD threshold voltage to go with a VDDQ of 2.7 to 3.3 volts.

- 2 Choose 2.7 volts LVD threshold voltage to go with a VDDQ of 3.0 to 3.6 volts.

- 3 If you to use USB, VDDQ of 3.3 volts is required to meet USB specifications. Select the 2.7 volt LVD threshold voltage.

The dialog shown in *Figure 11.: LVD Voltage tab*, is used to select the desired LVD threshold voltage.

#### Figure 11. LVD Voltage tab

| 1004004               | 1 <b>?</b> <i>N</i> ?                                                   | - · · · ·                                                                                                              |

|-----------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|                       | VD Voltage Clocks Peripheral /                                          | Pin Assignment   Pin Summary                                                                                           |

| Manage                | -Step 1: Specify Voltage                                                |                                                                                                                        |

| Project               |                                                                         | perating voltage supplies. The CPU and memories operate<br>and the I/O ring operates at 2.7V to 3.6V on the VDDQ pins. |

| · 🔶 🚬                 | Specify the VDDQ LVD threshold volta                                    | age: 🕫 🔼 🚺                                                                                                             |

| Design                |                                                                         | C 2.7V                                                                                                                 |

| Entry                 | Recommendations:                                                        |                                                                                                                        |

|                       | Choose 2.4V LVD threshold voltage<br>Choose 2.7V LVD threshold voltage  |                                                                                                                        |

| 1                     |                                                                         | -                                                                                                                      |

| dditional<br>Settings | Note: If you intend to use USB, VDDQ<br>You should select 2.7V LVD thre | of 3.3V is required in order to meet USB specifications.<br>eshold voltage.                                            |

| +                     |                                                                         | Apply                                                                                                                  |

| Program               |                                                                         |                                                                                                                        |

| Device                |                                                                         |                                                                                                                        |

|                       |                                                                         |                                                                                                                        |

|                       |                                                                         |                                                                                                                        |

|                       |                                                                         |                                                                                                                        |

Click either the 2.4V or 2.7V LVD threshold radio button, as applicable.

## 3.3 Specifying the clock source and frequency

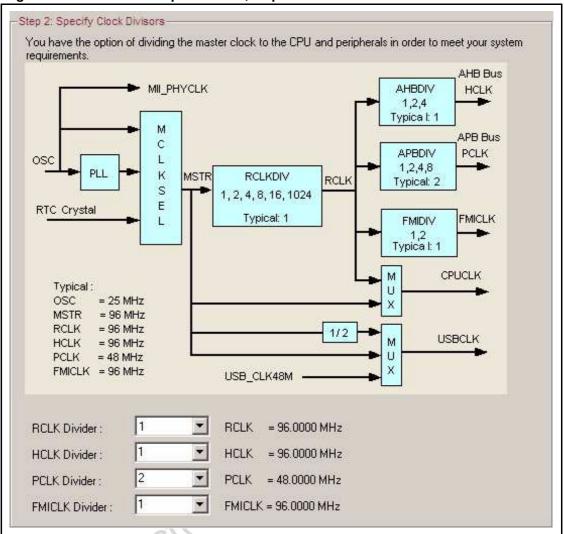

Click the **Clocks** tab for the following clocking options.

- Specify the clock source and master clock frequency.

- Specify the clock divisors.

- Save clock settings in a C-header file.

- Note: The clock settings affect the Hardware Abstraction Layer (HAL) library so the capability is provided to produce a C-header file to be included in your source code.

The following subsections discuss the clock configuration options in more detail.

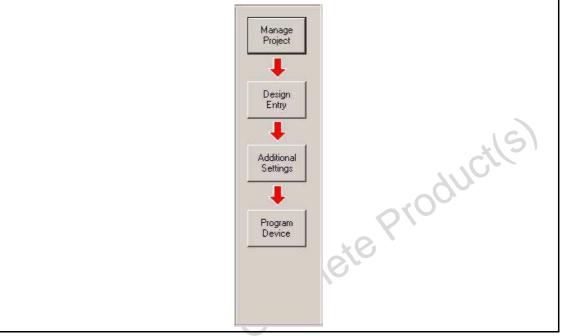

### 3.3.1 Selecting the clock source and frequency

There are three clock source options available.

- Main oscillator input clock (OSC)

- PLL clock

- RTC clock

Which clock source is selected affects which other clock configuration options are available. Clicking the radio button associated with the desired clock source automatically displays the configurable parameters, as describe below.

Note: Typical system values are displayed as default values in the following dialogs.

Selecting the *Main Oscillator input clock - 4 to 25 MHz external crystal*, requires you to enter the external crystal frequency, as shown in *Figure 12.: Main oscillator clocks selection, step 1*.

Figure 12. Main oscillator clocks selection, step 1

| ) 🖨 🔛 🐇 🖻              |                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Manage<br>Project      | Step 1: Specify Clock Source and Master Clock Frequency<br>The master clock (MSTR) in the Clock Control Unit (CCU) is derived from one of three clock input sources.<br>Select clock source to the CCU:<br>Main Oscillator input clock (OSC) - 4 to 25 MHz external crystal<br>C PLL clock                                                                                                                      |

| Additional<br>Settings | RTC clock - 32.768 KHz external crystal The source for the OSC is a 4 to 25 MHz external crystal connected to STR91xF. Enter your OSC frequency:     25 MHz                                                                                                                                                                                                                                                     |

| Program<br>Device      | Note: If you want STR91xF to provide clock to the external Ethermet PHY interface device,<br>OSC frequency should be 25 MHz. Otherwise, a separate clock is needed for the PHY.         PLL can be used to generate the desired master clock, frequency used by the CPU and various<br>peripherals. Maximum master clock, output is 36 MHz.         Enter the desired PLL clock frequency.         96       MHz |

|                        | Note: If you plan to use USB; master clock should be either 48 MHz or 96 MHz unless you provide an external USB clock. Click here to validate and refresh clock calculation >> Refresh                                                                                                                                                                                                                          |

The frequency must be in the range from 4 to 25 MHz.

Note: If the STR91x provides clock to the external Ethernet PHY interface device, the frequency must be 25 MHz. Otherwise, a separate clock is needed for the PHY.

The PLL can be used to generate the desired master clock frequency used by the CPU and various peripherals.

- Note: 1 The maximum master clock output is 96 MHz.

- 2 When using USB, the master clock frequency should be either 48 MHz or 96 MHz, unless an external USB clock is provided.

Selecting the *PLL clock*, requires you to enter the external crystal frequency and the PLL frequency, as shown in *Figure 13.: PLL clocks selection, step 1*.

57

| Figure 13. | PLL | clocks | selection, | step | 1 |

|------------|-----|--------|------------|------|---|

|------------|-----|--------|------------|------|---|

| Step 1: Spe                             | cify Clock So  | urce and Master Clo                            | ck Frequency-      |                                                |                           |   |

|-----------------------------------------|----------------|------------------------------------------------|--------------------|------------------------------------------------|---------------------------|---|

| 100000000000000000000000000000000000000 | 2012 N.        | TR) in the Clock Con<br>e to the CCU:          | trol Unit (CCU) is | derived from one of t                          | hree clock input sources. |   |

|                                         | 🔿 Main Osci    | llator input clock (OS)                        | C) - 4 to 25 MHz   | external crystal                               |                           |   |

| 4                                       | PLL clock      |                                                |                    |                                                |                           |   |

|                                         | C RTC clock    | < - 32.768 KHz extern                          | ial crystal        |                                                |                           |   |

| The sou                                 | ce for the OS  | C is a 4 to 25 MHz ex                          | ternal crystal co  | nnected to STR91xF.                            |                           |   |

| Ente                                    | r your OSC fre | equency: 25                                    | MHz                |                                                |                           |   |

| Note                                    |                |                                                |                    | mal Ethernet PHY inte<br>eparate clock is need |                           |   |

|                                         |                | enerate the desired m<br>master clock output i |                    | uency used by the CP                           | U and various             |   |

| Ente                                    | r the desired  | PLL clock frequency                            | 96                 | <br>MHz                                        |                           |   |

| Note                                    |                | o use USB, master clo<br>xternal USB clock.    | ock should be ei   | ther 48 MHz or 96 MH                           | tz unless you             |   |

|                                         |                | Click here t                                   | n validate and re  | fresh clock calculati                          | n >> Refresh              | 1 |

Enter the external crystal frequency, between 4 and 25 MHz, and with the same constraints as described, above.

Enter the PLL frequency.

obsolete Product(s)

Selecting the *RTC clock - 32.768 KHz external crystal*, requires you to enter the external crystal frequency, as shown in *Figure 14.: RTC clocks selection, step 1*.

Figure 14. RTC clocks selection, step 1

Enter the external crystal frequency, between 4 and 25 MHz, and with the same constraints as described, above.

After selecting the clock source and specifying the frequencies, click **Refresh** to validate he input and refresh the clock calculation.

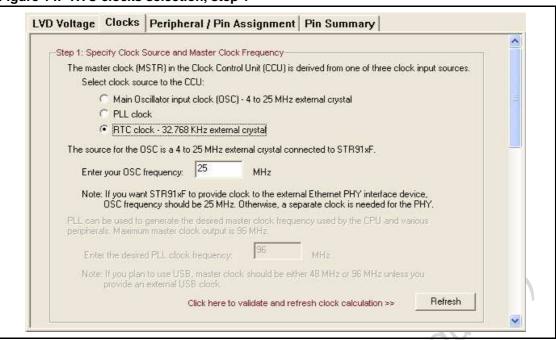

### 3.3.2 Specifying the clock divisor

CAPS provides the facility for dividing the master clock to the CPU and peripherals to meet particular system requirements; *Step 2: Specify Clock Divisors* provides the following divider options.

- RCLK Divider

- HCLK Divider

- PCLK Divider

- FMICLK Divider

Jbsolete

From the drop-down menu for each clock signal, select the desired divider value.

### 3.3.3 Saving the clock settings

It is recommended that you continue to step 3 of this dialog to create a C-header file. The header file  $91x\_conf.H$  is automatically created for your project along with *Project.H* file. The header file  $91x\_conf.H$  is used by the STR9 HAL library to initialize clock source and peripheral usage. (See *Figure 16.: Clock C-header create, step 3*).

| Constant of the second Class | name to save the entries in this session to a | - Chandar Ga   |

|------------------------------|-----------------------------------------------|----------------|

| specify folder and file      | name to save the entries in this session to a | a c-neader nie |

| Select folder and file:      | 1                                             | Save           |

Click the **Save...** button to save the C-header file.

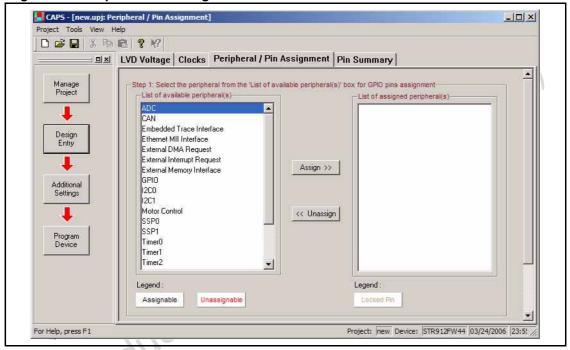

## 3.4 Specifying peripheral and GPIO pin assignment

Click the **Peripheral/Pin Assignment** tab to select the peripherals for your design. Pin resources are dynamically allocated and de-allocated based on peripheral selection. Therefore, the peripheral selection sequence directly affects pin resource assignment.

Note: The selected peripherals affect the initialization module in the HAL library. A default C-header file, 91x\_conf.H, is automatically generated to be included with the HAL library source code. It is recommended to generate a C-header file to be included in your source code, as described in Section 3.3.3, to facilitate integration of the CAPS design and initialization.

*Figure 17.: Peripheral/Pin Assignment tab* shows a list of peripherals available for the target device.

Figure 17. Peripheral/Pin Assignment tab

Select a peripheral from the list and click the *Assign>>* button to assign the pin, moving it to the list in the right window.

As peripherals are assigned, a dialog window displays configurable peripheral parameters. Enter the desired information and values to configure the peripheral. For peripherals that have predefined pin assignments, the following prompt is displayed to either accept the default assignment or enter a different pin assignment.

#### Figure 18. Accept default pin assignment prompt

| 12C0 |                                                                                      |

|------|--------------------------------------------------------------------------------------|

| (?)  | Do you wish to assign the pin function of your selected peripheral?                  |

| ~    | Default: Pin assignment is dynamically allocated based on pin resource availability. |

|      |                                                                                      |

|      | Yes No                                                                               |

Click **Yes** to define new pin assignments. Click **No** to accept the default pin assignments for the peripheral.

The following is a peripheral configuration example, using the Timer1 peripheral.

Figure 19. Example - assign Timer1 peripheral

| External Interrupt Request<br>External Memory Interface<br>GPI0<br>I2C0<br>I2C1<br>Motor Control | Assign >>   |  |

|--------------------------------------------------------------------------------------------------|-------------|--|

| SSP0<br>SSP1<br>Timer0<br>Timer1                                                                 | Assign >>   |  |

| Timer2<br>Timer3<br>UART0                                                                        | << Unassign |  |

| UART1<br>UART2<br>USB                                                                            | <u> </u>    |  |

| Legend :                                                                                         | Legend :    |  |

To select the *Timer1* peripheral, left-click Timer1 in the list of available peripherals, then click the *Assign >>* button.

For configurable peripherals, such as Timer1, a dialog window appears with the configuration options, as shown in *Figure 20.*

20. 20. CtlS ProductlS

| ADC<br>CAN                                                                      | List of assigned peripheral(s)                                                                      |

|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Embedded Trace Interface<br>Ethernet MII Interface<br>External DMA Request      | Peripheral Assignment - Timer                                                                       |

| External Interrupt Request<br>External Memory Interface<br>GPI0<br>I2C0<br>I2C1 | Select the desired timer/counter clock:      for Internal timer clock      for External timer clock |

| Motor Control<br>SSP0<br>SSP1<br>Timer0<br>Timer1<br>Timer2                     | Select the desired timer/counter mode as:                                                           |

| Legend :<br>Assignable Unassignable                                             | Pulse Width Modulation      Output Compare A      Output Compare B                                  |

| Step 2: Save C-header file                                                      |                                                                                                     |

Figure 20. Example - configure Timer1 peripheral

This example specifies the *Internal timer clock* (default) as the clock source, and *Input Capture* A and *Pulse Width Modulation* as the desired counter/timer modes.

Click **Pin Assignment...** to select the pin assignments for the peripheral function. The program displays the dialog shown in *Figure 21*.

|       | Assign the desired pin for its respective function.                                                    |

|-------|--------------------------------------------------------------------------------------------------------|

|       | Note: The Apply button assigns the pin to its function, and locks all<br>pin assignment automatically. |

|       | - Timer 1 - Capture A                                                                                  |

|       | € p4_2                                                                                                 |

| leteP | C p6_2                                                                                                 |

| e.    | Timer 1 - Compare/PWM A                                                                                |

|       |                                                                                                        |

|       | C p3_7                                                                                                 |

|       | C p4_2                                                                                                 |

|       | C p6_2                                                                                                 |

|       | \$ <u>po_</u> 2                                                                                        |

|       | Apply Cancel                                                                                           |

Figure 21. Peripheral pin assignment

57

Click the desired radio buttons to assign the pins to the respective function. Click the **Apply** button to save the assignment and to automatically lock the pin to the function.

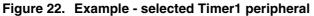

When the dialog shown in *Figure 20* is displayed, click **OK** to accept the configuration and continue. The Timer1 peripheral is selected and displayed in the *List of assigned peripheral(s)*, as shown in *Figure 22*.

| ADC<br>CAN                 | Timer1      |

|----------------------------|-------------|

| Embedded Trace Interface   |             |

| Ethernet MII Interface     |             |

| External DMA Request       |             |

| External Interrupt Request |             |

| External Memory Interface  | Assign >>   |

| GPIO                       |             |

| 1200                       |             |

| 12C1                       |             |

| Motor Control<br>SSP0      | << Unassign |

| ISSP1                      |             |

| Timer0                     |             |

| Timer2                     |             |

|                            | -           |

| All and a second data      |             |

| .egend :                   | Legend :    |

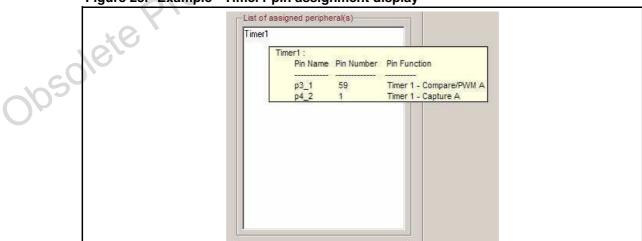

Mouse-over the *Timer1* peripheral in the *List of assigned peripheral(s)* to view pin resource utilization, as shown in *Figure 23*.

The example shows the functions dynamically assigned to pins 1 (P4\_2) and 50 (P3\_1).

Note: As an alternative, you may also view resource utilization using the **Tools**, **Generate Project Report** menu, or use **Pin Summary** for a graphic display of pin utilization.

#### Figure 23. Example - Timer1 pin assignment display

Because of STR91x pin dependencies, some peripherals may become unavailable for assignment as pins are assigned. CAPS, dynamically, makes the necessary pin assignments and reassignments. Peripherals no longer available for assignment, due to GPIO resource limitations, are highlighted in red.

Note: As a design aid, during pin assignment, you may always choose the Pin Summary tab to graphically show the current pin assignments. (See Figure 26.: Pin Summary tab).