## DISTRIBUTED COMPUTING AND OPTIMIZATION SPACE EXPLORATION FOR FAIR AND EFFICIENT BENCHMARKING OF CRYPTOGRAPHIC CORES IN FPGAS

by

Benjamin Brewster A Thesis Submitted to the Graduate Faculty of George Mason University in Partial Fulfillment of The Requirements for the Degree of Master of Science Computer Engineering

Committee:

KGa -h a Date:

Dr. Kris Gaj, Thesis Director

Dr. Jens-Peter Kaps, Committee Member

Dr. Brian Mark, Committee Member

Dr. Andre Manitius, Department Chair

Dr. Lloyd J. Griffiths, Dean, Volgenau School of Engineering

Spring Semester 2012 George Mason University Fairfax, VA Distributed Computing and Optimization Space Exploration for Fair and Efficient Benchmarking of Cryptographic Cores in FPGAs

A thesis submitted in partial fulfillment of the requirements for the degree of MasterMaster of Science at George Mason University

by

Benjamin Brewster Bachelor of Science West Virginia University, 2005

Director: Kris Gaj, Associate Professor Department of Computer Engineering

> Spring Semester 2012 George Mason University Fairfax, VA

This work is licensed under a <u>creative commons</u> <u>attribution-noderivs 3.0 unported license</u>.

## DEDICATION

This is dedicated to my wonderful wife Megan who put up with the long late nights and endless semesters of work.

## ACKNOWLEDGEMENTS

I would like to thank the CERG team that assisted me with all of my research needs and spent many long hours running tests and verifying results.

## TABLE OF CONTENTS

| Pag                                            |    |

|------------------------------------------------|----|

| List of Tables                                 | ii |

| List of Figures is                             | Х  |

| List of Equations                              | X  |

| List of Abbreviationsx                         | i  |

| Abstractxi                                     | ii |

| 1. Introduction                                | 1  |

| Problem                                        | 2  |

| 2. Background                                  | 4  |

| Cryptographic Standards Competitions           | 4  |

| Previous Competitions                          | 4  |

| SHA-3 Competition                              | 5  |

| Hardware Benchmarking                          | 5  |

| Benchmarking Pitfalls                          | 5  |

| Orchestration Algorithms                       | 7  |

| 3. ATHENa                                      | 1  |

| What is ATHENa                                 | 1  |

| Design and Workflow                            | 2  |

| Strategies and Searches                        | 2  |

| Areas for Improvement14                        | 4  |

| 4. Batch Systems and High Throughput Computing | 6  |

| Batch System Comparison 1'                     | 7  |

| Requirements1                                  | 7  |

| Batch Systems Investigated                     | 0  |

| 5. ATHENa Condor Architecture                  | 5  |

| Condor Architecture                            | 6  |

| Class Ad Mechanism                             | 6  |

|    | Condor Pool                       | . 27 |

|----|-----------------------------------|------|

|    | Condor Master                     | . 28 |

|    | Condor Startd                     | . 28 |

|    | Condor Starter                    | . 28 |

|    | Condor Schedd                     | . 29 |

|    | Condor Shadow                     | . 29 |

|    | Condor Collector                  | . 29 |

|    | Condor Negotiator                 | . 30 |

|    | Roles                             | . 30 |

|    | Central Manager                   | . 30 |

|    | Submit Host                       | . 31 |

|    | Execute Host                      | . 31 |

|    | ATHENa Client/Server Architecture | . 32 |

| 6. | Related Tools                     | . 37 |

|    | eBACS                             | . 37 |

|    | Xilinx PlanAhead                  | . 38 |

|    | Altera Design Space Explorer      | . 39 |

| 7. | Optimization Space Exploration    | . 40 |

|    | Least Effort                      | . 40 |

|    | Most Effort                       | . 40 |

|    | Batch Elimination                 | . 41 |

|    | Iterative Elimination             | . 44 |

|    | Orthogonal Array                  | . 46 |

|    | Frequency Search                  | . 50 |

|    | Placement Search                  | . 51 |

|    | Tool Separation                   | . 52 |

|    | Metrics                           | . 53 |

| 8. | SHA-3 Case Study                  | . 55 |

|    | SHA-3 Candidates                  | . 55 |

|    | Experimental Design               | . 56 |

|    | Results                           | . 58 |

| 9. | Conclusion                        | . 77 |

|    |                                   |      |

| Appendix A: Configuration Files | 83 |

|---------------------------------|----|

| Condor Submit File              |    |

| ATHENa Design Config            | 85 |

| ATHENa Option File              | 86 |

| Appendix B: Users Guide         | 87 |

| GUI                             | 87 |

| References                      |    |

## LIST OF TABLES

| Table                                                   | Page |

|---------------------------------------------------------|------|

| Table 1 Batch System Comparison                         |      |

| Table 2 Batch Elimination                               |      |

| Table 3 Iterative Elimination                           | 45   |

| Table 4 Orthogonal Array                                | 49   |

| Table 5 Experiment 1 Options                            | 57   |

| Table 6 Experiment 2 Options                            | 58   |

| Table 7 JH Results                                      |      |

| Table 8 BLAKE Results                                   | 63   |

| Table 9 Skein Results                                   | 65   |

| Table 10Keccak Results                                  |      |

| Table 11 Performance Relative to Most Effort Spartan 3  | 71   |

| Table 12 Performance Relative to Most Effort Virtex 6   | 71   |

| Table 13 Performance Relative to Least Effort Spartan 3 | 71   |

| Table 14 Performance Relative to Least Effort Virtex 6  | 72   |

| Table 15 Maximum Performance                            | 73   |

## LIST OF FIGURES

| Figure                                                        | Page |

|---------------------------------------------------------------|------|

| Figure 1 Condor Roles                                         | 32   |

| Figure 2 Client GUI Submissions                               | 34   |

| Figure 3 Client GUI Execute Hosts                             | 34   |

| Figure 4 Client/Server Architecture                           | 36   |

| Figure 5 Batch Elimination Parallel Task Decomposition        | 43   |

| Figure 6 Iterative Elimination Parallel Task Decomposition    | 46   |

| Figure 7 Orthogonal Array                                     | 47   |

| Figure 8 Orthogonal Array Parallel Task Decomposition         | 50   |

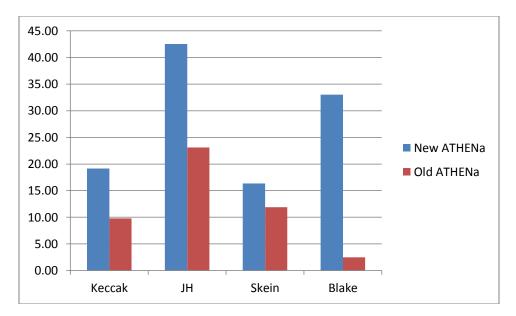

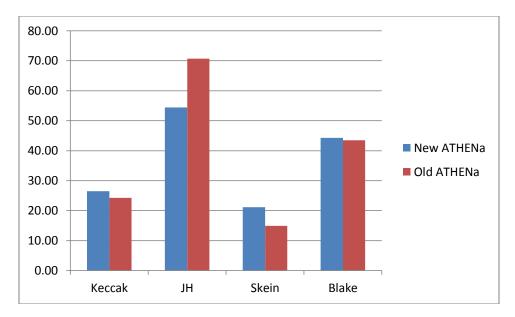

| Figure 9 New ATHENa vs. Old ATHENa: Max Performance Spartan 3 | 74   |

| Figure 10 New ATHENa vs. Old ATHENa: Max Performance Virtex 6 | 75   |

| Figure 11 Configuration Wizard Icon                           | 87   |

| Figure 12 Job Submission Process                              | 89   |

# LIST OF EQUATIONS

| Equation                                 | Page |

|------------------------------------------|------|

| Equation 1 Relative Improvement          | 41   |

| Equation 2 Relative Improvement Baseline |      |

| Equation 3Relative Improvement OA        |      |

## LIST OF ABBREVIATIONS

| Automated Tool for Hardware Evaluation                               | ATHENa      |

|----------------------------------------------------------------------|-------------|

| Batch Elimination                                                    | BE          |

| Iterative Elimination                                                | IE          |

| Orthogonal Array                                                     | OA          |

| Frequency Search                                                     | FS          |

| Batch Elimination with nine options                                  | BE9         |

| Iterative Elimination with nine options                              | IE9         |

| Frequency Search followed by Batch Elimination with nine options     | FS=>BE9     |

| Frequency Search followed by Iterative Elimination with nine options | FS=>IE9     |

| FS followed by BE9 followed by Placement Search                      | FS=>BE9=>PL |

| FS followed by IE9 followed by Placement Search                      | FS=>IE9=>PL |

|                                                                      |             |

### ABSTRACT

## DISTRIBUTED COMPUTING AND OPTIMIZATION SPACE EXPLORATION FOR FAIR AND EFFICIENT BENCHMARKING OF CRYPTOGRAPHIC CORES IN FPGAS

Benjamin Brewster, MSCpE.

George Mason University, 2012

Thesis Director: Dr. Kris Gaj

Benchmarking of digital designs targeting FPGAs is a time intensive and challenging process. Benchmarking results depend on a myriad of variables beyond the properties inherent to the designs being evaluated, encompassing the tools, tool options, FPGA families, and languages used. In this thesis we will be discussing enhancements made to the ATHENa benchmarking tool to utilize distributed computing as well as optimization space exploration techniques to increase the efficiency of the ATHENa benchmarking process. Capabilities of the environment are demonstrated using four example designs from the SHA-3 cryptographic hashing function competition, BLAKE, JH, Keccak and Skein.

#### 1. INTRODUCTION

The development of new cryptographic standards through competition has necessitated the need for fair and comprehensive benchmarking tools and a methodology for their use that deals with the inherent objective difficulties in these evaluations. Proposed algorithms must be compared in terms of security, cost and implementation flexibility for both their hardware and software implementations. The end goal of ATHENa[1] is to remove the burden of generating high quality benchmarking results from the algorithm designer and generate benchmarking results in a clear unbiased manner for publication and comparison.

Open competition has become the method of choice for adopting new cryptographic standards starting with the AES competition sponsored by NIST in 1997-2000, and followed by the NESSIE and eSTREAM competitions in Europe and the CRYPTREC competition in Japan. The move from traditional standards development to open competition has driven the need for evaluation environments that allow for the fairest possible benchmarking of competing algorithms. Algorithms are typically evaluated based on four criteria, security, performance in software, performance in hardware, and flexibility. While of the utmost concern, the security provided by these algorithms can be incredibly difficult to quantify in the timeline provided by these competitions. After careful examination of an initial pool of algorithm candidates

elimination of a few can be done based on inherent security flaws in the algorithms themselves and the remaining candidates can be considered to be equally secure. It has been shown, interestingly enough, that the largest differences tend to emerge in the hardware implementation of the algorithms and this can often serve as the deciding criteria for algorithm adoption in the face of no other clear advantages.

Fair comparison of the hardware efficiency of cryptographic algorithms modeled in Hardware Description Languages and targeted to FPGA platforms is a computationally complex problem that depends on many factors beyond just the algorithm being evaluated and includes targeted architectures, implementation techniques, FPGA families, languages and tools. ATHENa is an evaluation environment that is meant to address these issues with respect to FPGAs and provide a platform to more objectively evaluate and compare new designs. The inherent computational complexity makes the development of a tool that can automate this task as efficiently as possible vitally important to algorithm developers and evaluators alike.

#### Problem

The main focus of this thesis is the objective evaluation of functionally equivalent algorithms across different metrics implemented in hardware targeted to FPGA platforms focusing on their use in future cryptographic standards. Evaluations of this kind are subject to many pitfalls and difficulties that must be addressed to arrive at a fair comparison which is of interest to a cryptographic community that has become reliant on competition for standards adoption. It is necessary to remove the burden of performing benchmarking and comparisons of algorithms from the algorithm designer and create an

environment that addresses these needs objectively and efficiently. Benchmarking of digital designs targeting FPGAs is a time intensive and challenging process. Benchmarking results depend on a myriad of variables beyond the properties inherent to the designs being evaluated, encompassing the tools, tool options, FPGA families, and languages used. In this paper we will be discussing enhancements made to the ATHENa benchmarking tool to utilize distributed computing as well as optimization space exploration techniques to increase the efficiency of pre-existing process. Select candidates for the ongoing NIST SHA-3 competition are used as a case study in utilizing the improved ATHENa benchmarking environment. It is shown that through the use of the ATHENa environment the process of objectively comparing candidate algorithms with respect to optimization can be performed much more efficiently and thus aid in their evaluation.

## 2. BACKGROUND

#### **Cryptographic Standards Competitions**

In 1997 NIST announced the desire to adopt a new encryption standard as a replacement to DES. The new standard, AES, was adopted through an open competition in the cryptographic community and competitions of this type have become the preferred method for the development and adoption of new cryptographic algorithms. These competitions require the competing algorithms to be scrutinized and compared in the finest detail. The algorithms must pass rigorous cryptanalysis, hardware and software benchmarking and implementation examination. The amount of work that goes into analysis of these types is incredible and time consuming.

### **Previous Competitions**

Apart for the previously mentioned AES competition, open competition has been used successfully in other cases. NESSIE was a competition in Europe that was aimed at identifying different classes of secure cryptographic primitives. The competition included block ciphers, public-key encryption, MAC algorithms and cryptographic hash functions, digital signature algorithms, and identification schemes. The NESSIE competition lead directly to the formation of the eSTREAM competition to identify stream ciphers due to the fact that all stream ciphers submitted to NESSIE fell to cryptanalysis. Another related competition was the Japanese competition CRYPTREC which was sponsored by the

Japanese government with intent to find cryptographic primitives suitable for industrial and government use.

### SHA-3 Competition

The latest cryptographic competition is the NIST sponsored SHA-3 competition. Announced in 2007 its aim is to develop a replacement to the SHA-2 cryptographic hash algorithm. The competition is in its final round of algorithm evaluation and the five finalist algorithms are all used as an illustration of the improvements made to ATHENa as outlined in this text.

### Hardware Benchmarking

Hardware benchmarking is a process that requires a lot of care and effort to accomplish properly. With respect to digital systems targeting FPGAs modeled with hardware description languages, many difficulties can arise. The goal of the ATHENa project is to address these goals by creating an environment that tries to eliminate evaluation pitfalls while benchmarking as much as possible.

#### **Benchmarking Pitfalls**

Benchmarking pitfalls, also known as evaluation pitfalls are easier to identify and remedy if the evaluation and benchmarking is done with care. One of the most common benchmarking pitfalls is metric selection. Metric Selection is simply ensuring that the designs being compared are using a fair and common metric. Comparison metrics must be chosen with care and must be common across the algorithm implementations that are being used for comparison. Common comparison metrics that are used by ATHENa are throughput, area, and throughput to area ratio. It is also important that a metric such as area is common between designs because area can be composed of different things such as slices, look-up tables, flip-flops, or BRAMs. Within ATHENa the common area metric for Xilinx devices is slices used while Altera devices rely on comparisons using ALUTs.

Another common pitfall is taking credit for technology improvement as algorithm improvement. In FPGAs this can most notably be seen when comparing an algorithm targeting one FPGA family and device to another. The newer devices are higher performing and it is important to only compare algorithms targeting the same device family to account for these technology improvements.

It is also extremely important to ensure that the algorithms being compared and benchmarked against each other have similar functionality. It would be unfair to compare two algorithms with different functionality as proof that one algorithm was superior to the other. It must be ensured that the two algorithms have the same intent and functionality before a meaningful comparison can be made.

Optimization target is another issue that is very similar in nature to the metric pitfall described earlier but relates more directly to targeted optimization than the metric itself. Optimization targets are goals that a system is trying to achieve relative to a given metric. For example if my optimization target was speed I would optimize my design and especially the implementation to achieve the highest throughput. If this was the case it would be unfair for me to compare the speed of my algorithm to that of an algorithm with an area optimization target. It is also essential that the correct numbers are compared. This is especially true in the field of FPGAs where there are many steps to the design implementation and performance metrics could be generated at many of the intermediate steps. It is important that the final placed and routed designs only be compared as these

are the true numbers that would manifest themselves on a device. You must ensure that you are not comparing synthesis results to final timing results for instance.

These pitfalls are quite prevalent in many algorithm comparisons and arise for various reasons from simple mistakes to purposefully misleading results. ATHENa has functionality that helps combat these pitfalls and offer a fairer system for comparison and benchmarking.

## **Orchestration Algorithms**

The main area for improvement for ATHENa was identified to be the way that the various option sets offered by the Synthesis and Implementation software were explored and an optimal set chosen for each algorithm. Experimentally it has been shown that changes in the tool options can have an enormous impact on the realized performance of an algorithm with respect to a given metric. The options are numerous enough that it is non-trivial to determine the best option combination provided by the software tools. The goal of a fair comparison of the competing algorithms necessitates the exploration of many option sets for all algorithms to ensure that the true performance is fully discovered. If two algorithms are being compared using handpicked option sets by their creators, it is hard to determine the better design. This is compounded by the fact that option sets vary depending on the specific device, family and vendor chosen as an implementation target.

Previous related research has been undertaken by the computer science community focusing on compiler option selection for optimization of computer programs[4]. While there are differences and caveats that have to be taken into account

when comparing work done for software compilers and FPGA synthesis and implementation tools, many parallels exist and previous work can be leveraged to a certain extent. In the section focused on comparing hardware and software benchmarking some of these issues are discussed in greater depth especially pertaining to the methods used by ATHENa as opposed to the eBASH system for software benchmarking. Modern compilers offer many optimization option flags that can be selected to extract greater performance from a given source code. These optimizations offer potentially large performance gains but are largely underutilized given their complexity and the number of options to choose from. The compilers themselves are generally unable to find the best options at compile time and require a user to manually perform feed-back driven analysis of different options sets. The process is further hindered by the fact that certain optimizations can have a negative performance impact on certain source codes so applying a highest optimization level for all options is not always the best approach. The time consuming tedious nature of feed-back driven analysis has led to the development of different orchestration algorithms for the determination of optimization option selection.

Compiler construction-time pruning as proposed in Compiler Optimization-Space Exploration is a method that determines the hot-paths of a program based on profiling data and iteratively constructs new optimization sets for these hot-paths based on unions of previous iterations' sets. The ability to determine hot-paths, or the sections of a program that is executed most often, could be very useful in the domain of FPGAs. Optimizations could be found that benefit individual modules or sections of an FPGA

implementation and then optimized separately. While the concept appears promising it is outside the scope of this investigation but could be a subject of future research.

Orthogonal arrays are proposed as a means to statistically analyze profile information generated by an optimized program and measure the main effect of different optimization options in Statistical Selection of compiler Options. The large number of compiler options is too great to perform a full exhaustive search to arrive at the optimal solution, this would require approximately  $2^k$  option sets, where k is the number of options if all options are binary(on/off). The method employed is borrowed from the framework of the Design of Experiments. Orthogonal Arrays are a matrix of 1's and 0's where each column represents an option and each row is an option set for the compiler, 1 representing the option is on, 0 representing the option is off. An Orthogonal Array has the property that two arbitrary columns contain the patterns 00, 01, 10, 11, equally often. Orthogonal Arrays provide a method for obtaining a fractional factorial design allowing information about a large set of variables be analyzed with much fewer runs than an exhaustive search over the full factorial search space. This approach has many applications in experimental design and testing but the creation of orthogonal arrays that map to the options used by FPGA synthesis and implementation tools is difficult because of the existence of options with more than two levels. This method can be adapted to the binary options provided by the tools and used as a method for FPGA optimization within ATHENa.

Fast and Effective Orchestration of Compiler Optimizations for Automatic Performance Tuning also investigates the use of feed-back driven methods to determine the most effective compiler optimizations. Batch Elimination (BE) and Iterative Elimination (IE) are put forth as viable alternatives to an exhaustive search in terms of the optimality of the solution and the time that is required to achieve near optimal results. It is shown that by isolating each option and comparing the isolated option's effect against a baseline that the effect of loosely interacting options can be determined. This is the idea behind batch elimination. To take into account the effect of one option on another iterative elimination can be employed to perform successive batch eliminations in a way that the interactions of options can be taken into account. Both batch elimination and iterative elimination can be mapped easily to ATHENa and need only minor changes to handle options that are not binary as they were originally intended.

## 3. ATHENA

The open-source benchmarking environment called ATHENa (Automated Tool for Hardware EvaluatioN) aims to address the difficulties associated with the fair comparison of digital systems designed and modeled using hardware description languages and implemented on FPGAs. These comparisons require thorough benchmarking of the digital systems to determine the optimal set of design tool options to use given an FPGA family and device target that achieves the highest performance relative to the selected evaluation metric. Determining the optimal set of tool options is a task that requires searching the entire option space of the tools used for FPGA implementation. This task becomes infeasible for large tool option sets provided by modern FPGA implementation tools. ATHENa aims to alleviate the complexity of this task, overcome the pitfalls and difficulties inherent to these evaluations, and to spread awareness of good practices for the benchmarking of algorithms belonging to the same class. The goal of this section is to describe the ATHENa environment and introduce a number of improvements to this system that can greatly increase its usefulness as a benchmarking tool.

## What is ATHENa

ATHENa is at its most basic a set of Perl scripts that allow a user to easily run FPGA synthesis and implementation tools in the batch mode from the command line. It is free and open source software under development by the Cryptographic Engineering Research Group at GeorgeMasonUniversity. The scripts support tools from the two largest FPGA vendors, Xilinx and Altera and can utilize both licensed and unlicensed versions of the tools. Both VHDL and Verilog description languages are supported. ATHENa also supports automated functional verification of the designs and detailed report generation.

#### **Design and Workflow**

ATHENa allows a user to take VHDL codes that they have written and easily execute synthesis and implementation tools on these codes using configurations that have been developed by the ATHENa team as well as other users who have uploaded results to the ATHENa database. A designer can specify a number of options such as the devices they wish to target, timing constraints, generic values they wish to set and then execute the design tools for their device target through the command line and automatically generate results that can be uploaded to the ATHENa results database.

#### **Strategies and Searches**

One of the goals of the ATHENa environment is to provide a tool that aids in the optimization of design targeting FPGAs. These optimizations are carried out through the use of strategies and searches.

Strategies are predetermined option sets that target a certain performance metric such as throughput to area. The options have been determined to yield good results for

the specific metric that they target making it easy for a designer to optimize their design for a specific metric even if they are ignorant to the underlying tools and how they work. While strategies do not guarantee best performance or optimal results for the metric that they target, they provide good targeted results with no effort or tool knowledge from the designer.

Searches are like strategies except that they aim to achieve more optimal results than strategies aim at. Instead of a static predetermined set of options the options and their values are programmatically determined. This process requires running the design tools multiple times varying the input options in response to the output performance results. Placement Search permits the exploration of result dependencies on the starting point of placement. This starting point is determined by the options of the FPGA implementation tools called: Cost Table in Xilinx tools and Seed in Altera tools. Cost Table can take any integer value between 1 and 100, and Seed any value between 1 and 2^32. Placement search is done by exhaustively searching a subset of the valid placement values. Exhaustive search is an extension of placement search and includes options other than placement options. Any tool option can be evaluated in the exhaustive search, but the number must be constrained to a relatively low value because if not the search is unfeasible. The last search provided by ATHENa is frequency search. Both Xilinx and Altera tools have an option corresponding to the desired frequency of the resulting implementation. By adjusting this value the performance of the design can change leading to greater performance. Frequency search aims to determine the best value for input frequency that yields the best resultant performance.

#### **Areas for Improvement**

One of the largest drawbacks to the previous version of ATHENa is the inability of the system to efficiently process large benchmarking and comparison workloads. In the general case ATHENa executes all jobs in a serial batch manner. Limited parallelism existed with some search algorithms but is limited to the logical cores of the host system. It was determined that a way to extract the parallelism that exists in these jobs and distribute it across multiple compute nodes would greatly increase the effectiveness of the system. Many of the benchmarking tasks executed by ATHENa have few dependencies on other tasks and are candidates for parallel execution. By utilizing the parallelism offered by a distributed batch system this inherent parallelism can be exploited.

It was also determined that besides the nearly serial nature of the execution of tasks in ATHENa, more effective optimization algorithms should be developed that can make better use of the distributed system architecture and find a more efficient way to reach an optimized design solution. This shortcoming lead to the design of the optimization space exploration algorithms presented in this text as well as the Frequency Search and Placement Search that was designed with the distributed system in mind.

The last issue that needed to be addressed was the user interface of the system. ATHENa up to this point was a command line tool. The ability to effectively monitor and manage large benchmarking workloads was missing. In the design of the new ATHENa a GUI front-end was developed to help alleviate these issues and allow easy monitoring and management of ATHENa tasks.

By combining these new features ATHENa becomes much more powerful and practical to use. It also helps the system to become much more approachable from a user perspective and not just a pure engineering tool that requires knowledge of the implementation details to use effectively.

#### 4. BATCH SYSTEMS AND HIGH THROUGHPUT COMPUTING

Benchmarking algorithms designed with hardware description languages and targeted to FPGA devices require the use of synthesis and implementation tools that can utilize a large amount of CPU time to complete. This fact is compounded by the need to run many benchmarks with separate option sets to comprehensively benchmark any single implementation. The result is that it can take many days and even weeks to properly synthesize and implement a candidate algorithm for evaluation across all of the option sets required. One solution to this problem is to utilize High Throughput Computing (HTC) architectures to help alleviate the massive CPU hours required to complete benchmarking and evaluation tasks.

HTC is the use of computing systems to maximize the number of operations that can be completed per month or year as opposed to how to minimize the latency of an operation. They are specifically computing environments that can deliver large amounts of processing capacity over long periods of time. They are specially suited for problems with long compute times that can be parallelized over the input data sets that need to be processed. Many systems exist for setting up HTC environments, but a subset, Batch Systems, are of interest to this study. Batch systems are systems that can distribute the execution of batch programs across multiple computing nodes simultaneously. They are primarily used in research environments where the same program needs to process a large

set of varying data. This applies directly to the ATHENa problem space where the program is ATHENa and the data are the various option sets used to benchmark the cryptographic algorithms. By leveraging the parallelism offered by a HTC batch system, multiple benchmarking jobs can be run at once alleviating the time to comprehensively benchmark any single algorithm.

#### **Batch System Comparison**

In the case of ATHENa a HTC environment needs to be able to distribute and manage multiple benchmarking runs across heterogeneous computing resources. This will allow ATHENa to decrease the time needed to complete benchmarking substantially and increase the utilization of the existing resources. A set of requirements was gathered and ranked in importance to help compare various systems. Many different batch systems as well as other HTC environments exist and are widely used. Below is an investigation of a subset of such systems that were identified for their potential use with ATHENa.

#### Requirements

The requirements are listed below and given a weight that ranks their importance. Each system is given a score for each requirement and then the weighted result is used for final comparison. The weighting scheme used to determine the best system and the scores for the different systems that were evaluated are located in Table 1.

#### Architecture

The architecture of the system is important for ATHENa. It is desirable to have a system that has a centralized server that manages the batch jobs with compute and submit nodes that communicate with this server. The systems should impose no language restrictions on the jobs that are run and would preferably not require any special build steps for the ATHENa software. The last architectural requirement would be the ability of the system to transparently fall back to a single machine system if the user is not connected to the central server requiring only one ATHENa environment that would work in a HTC and single node system. This flexibility is paramount to making the system intuitive and easy to use.

#### Administration

The system should be easy to administer and setup as well as easy to use. It should also support remote administration allowing a user to schedule and monitor submitted jobs remotely. Once jobs are submitted a user of the system should be able to leave it unattended for long periods of time and monitor the submitted jobs from any machine with network access to the system. A graphical user interface to monitor and administer jobs would also be recommended.

#### **Resource Specification**

The batch system should be flexible enough to handle multiple types of resources. In the context of ATHENa, the resources would be available machines, processing cores and software licenses that are needed by the ATHENa programs.

### Fault Tolerance

The system should be able to recover from basic errors and reschedule work accordingly. The fault tolerance needs to exist at both the central server if one exists and at the compute nodes that do the actual processing. In the most basic case the system needs to allow work to not be lost if the central server goes down, and the central server should be able to allow for nodes that execute jobs to leave the system without failure.

#### Security

The system should try to minimize the potential security threats inherent to distributed systems. Basic authentication and other measures must be present.

## Stage In/Out

The system should allow files to be specified that must be transferred to execution nodes in order to process the batch job and files that must be transferred back upon completion. The system optionally should provide a mechanism to transfer the executable batch program with the input for maximum flexibility. The transfers would preferably use ssh/scp for transmission.

## **Platform Support**

The batch system should support multiple operating systems. ATHENa currently runs on both Windows and Linux and the batch system should utilize both if possible.

#### Scheduling

Scheduling is a very important aspect of batch systems. Scheduling effects how the compute resources are used and to what extent the resources are utilized. The system should provide flexibility to define multiple scheduling options, change job priorities, pause/resume/terminate jobs, and define different user profiles.

#### **Batch Systems Investigated**

For the purpose of this investigation, six different batch systems where found and compared for use with ATHENa. While some of the systems are not pure batch systems all can be used for this purpose. All of the systems are FOSS (free open source software) systems and are under active development.

#### Condor

Condor is a HTC project under development by the University of Wisconsin-Madison department of computer science. The system was first put into production 15 years ago and is still under active development. Condor is a specialized workload management system for compute intensive jobs that provides job queuing mechanisms, scheduling policies, priority schemes, resource monitoring, and resource management. Condor can process serial or parallel jobs and can utilize idle machines for processing. Condor contains many other features as well as third party additions for things such as graphical displays and accounting. Stage In/Out is supported as well as the ability to transfer the application to be executed to the remote compute node. Condor also has the ability to run on a single machine in the absence of a cluster, though this behavior is not transparent to the user and requires specialized configuration. Condor is a multi-platform system and can run on many flavors of Linux, Solaris as well as Windows.

#### Globus

Globus is a tool kit for grid computing. Unlike the traditional batch systems Globus is a meta-scheduler, used to schedule work across multiple compute clusters. Globus can be adapted and used to administer a single compute cluster although with slightly less functionality than the full system. Globus provides a basic scheduler but does not provide a mechanism for data transfer without the existence of a shared file system. Third party tools have also been created for Globus for the monitoring and accounting of jobs.

#### **Torque**

Torque is a resource manager providing control over batch jobs on distributed compute nodes. Torque is a community effort that was based on the PBS (portable batch system) project. Torque has a basic scheduler but is primarily used as only a resource manager with an external scheduler. Torque provides job management, resource management, resource and job monitoring, job queuing and basic batch scheduling. Torque has stage in/out capabilities utilizing SCP or networked file systems. Torque can be configured on a standalone machine although is not intended to be configured this way.

#### **Toque with MAUI Scheduler**

The MAUI scheduler is an open source scheduler for clusters and super computers. It has an array of scheduling policies, can handle dynamic priorities, resource reservations, and other advanced scheduling capabilities. It also contains useful monitoring and diagnostic tools and keeps track of resource utilization. MAUI while not a batch system can be integrated into Torque, increasing Torque's scheduling capabilities.

#### **JPPF**

JPPF is the Java Parallel Processing Framework. JPPF enables applications with large processing requirements to be run on any number of computers. JPPF is written in Java and requires jobs to wrapped in a simple java class for execution. Because JPPF is a Java framework any platform that supports Java can run JPPF jobs. There are extensive examples and third party tools for JPPF. While JPPF is a parallel processing framework it can easily be adapted for batch processing. While the documentation appears to be good, information was scarce on support for stage in/out and what is used for security and internode communications. Basic scheduling is supported with job prioritization and tools for monitoring and managing resources and job execution. JPPF also contained a full featured GUI for job management and monitoring, a feature that no other system had to this extent.

#### **SLURM**

SLURM (simple Linux utility for resource management) is an open source cluster management and job scheduling system for Linux clusters. It was developed by Lawrence Livermore National Laboratory and has been used on many projects. It provides exclusive or non-exclusive access of compute resources, a framework for starting, executing and monitoring work on the compute nodes, and it arbitrates

## Table 1 Batch System Comparison

|                               |                                   | Condor | Globus | Torque | MAUI | JPPF | SLURM |

|-------------------------------|-----------------------------------|--------|--------|--------|------|------|-------|

|                               | Centralized Server(1)             | 5      | 5      | 5      | 5    | 5    | 5     |

| iure                          | No Language Restrictions(2)       | 5      | 5      | 5      | 5    | 2    | 5     |

| Architecture                  | No Special Build Steps(2)         | 5      | 5      | 5      | 5    | 3    | 5     |

| Arc                           | Transparent Single Machine Use(1) | 3      | 0      | 0      | 0    | 4    | 0     |

| Total                         | (30)                              | 28     | 25     | 25     | 25   | 19   | 25    |

| c                             | Ease of Use(1)                    | 4      | 2      | 4      | 4    | 2    | 4     |

| tratio                        | Remote Admin(2)                   | 4      | 3      | 4      | 4    | 4    | 4     |

| Administration                | Remote Monitoring(2)              | 4      | 3      | 4      | 4    | 4    | 4     |

| Ad                            | GUI(1)                            | 2      | 0      | 0      | 0    | 4    | 2     |

| Total                         | (30)                              | 22     | 14     | 20     | 20   | 22   | 22    |

| ati                           | Machines(2)                       | 5      | 0      | 5      | 5    | 3    | 5     |

| Resource<br>Specificati<br>on | CPU Cores(1)                      | 4      | 0      | 5      | 5    | 0    | 5     |

| Sp Re                         | Licenses(2)                       | 5      | 0      | 3      | 4    | 0    | 3     |

| Total                         | (25)                              | 24     | 0      | 21     | 23   | 6    | 21    |

| Fault<br>Toleran<br>ce        | Server(1)                         | 5      | 0      | 4      | 4    | 0    | 5     |

| Faul<br>Tole<br>ce            | Compute Node(1)                   | 5      | 0      | 4      | 4    | 0    | 5     |

| Total                         | (10)                              | 10     | 0      | 8      | 8    | 0    | 10    |

| Securi<br>ty                  |                                   |        |        |        |      |      |       |

| ty Se                         | System Security(2)                | 4      | 4      | 2      | 2    | 0    | 4     |

| Total                         | (10)                              | 8      | 8      | 4      | 4    | 0    | 8     |

|                               | Stage In/Out(2)                   | 5      | 5      | 4      | 4    | 3    | 0     |

| Stage<br>In/Out               | Binary/Program Transfer(1)        | 5      | 0      | 3      | 3    | 0    | 0     |

| Sta<br>In/(                   | SSH/SCP(2)                        | 0      | 2      | 5      | 5    | 0    | 0     |

| Total                         | (25)                              | 15     | 14     | 21     | 21   | 6    | 0     |

| for                           | Windows(2)                        | 5      | 0      | 0      | 0    | 5    | 0     |

| Platfor<br>ms                 | Linux(2)                          | 5      | 5      | 5      | 5    | 5    | 5     |

| Total                         | (20)                              | 20     | 10     | 10     | 10   | 20   | 10    |

|                               | Job Priorities(2)                 | 5      | 0      | 5      | 5    | 5    | 5     |

| þ                             | Flexibility(1)                    | 4      | 0      | 2      | 5    | 2    | 3     |

| Scheduling                    | Manual Pause/Resume/Terminate(2)  | 5      | 0      | 5      | 5    | 5    | 5     |

| Sch                           | User Profiles(1)                  | 5      | 0      | 0      | 5    | 0    | 3     |

| Total                         | (30)                              | 29     | 0      | 22     | 30   | 22   | 26    |

|                               |                                   |        | *      |        |      |      |       |

| Overall<br>Score              | (175)                             | 156    | 71     | 131    | 141  | 95   | 122   |

contention for resources by managing a queue of pending work. SLURM is intended as a resource management system with other utilities used for stage in/out and complicated scheduling.

### 5. ATHENA CONDOR ARCHITECTURE

ATHENa in the initial version is a non-distributed multiprocessing program that consists of a set of Perl scripts that are used to interact with FPGA synthesis and implementation tool command line interfaces. The scripts take user configurations provided in structured configuration files that specify tool options, project options and formulas for latency calculations that are used to manage the execution of the command line tools and provide detailed reports after execution has completed. The parallelism was limited to the number of processors on the host system and was thus limited in the ability to efficiently process large sets of configurations as needed in benchmarking tasks. Due to the computational load of running benchmarks with the ATHENa system, a new approach was adopted to deal with these shortcomings. Distributed batch systems would allow the existing ATHENa scripts to remain for the most part intact and leverage the parallelism provided by a compute cluster to scale the system to the extent that compute resources are available. Parallelism is extracted at the run level, each run is a job that can be submitted to a remote compute node for processing. This is extremely beneficial with respect to advanced benchmarks such as exhaustive search and other orchestration algorithms for optimization because each run or option set being investigated is an independent work unit that can leverage the parallelism provided by the new architecture.

It was found in the investigation of distributed batch systems that Condor was the candidate system that most completely met the various requirements that ATHENa needed. The adoption of a distributed architecture required an evolutionary revision in the design of the ATHENa system as detailed here.

#### **Condor Architecture**

Condor as described previously is a distributed batch system for high throughput computing under development by the University of Wisconsin Department of Computer Science[5],[6]. The system allows for the distribution of computing across a cluster of heterogeneous computing resources.

### **Class Ad Mechanism**

Condor utilizes a specialized class ad mechanism, similar to newspaper classified ads, to match jobs to compute resources[7]. Class Ad Matchmaking as described in Matchmaking: Distributed Resource Management for High Throughput Computing allows a program to specify what requirements it has and properly allocate the processing to a compute node that contains these requirements. It is particularly effective in an environment where various dissimilar resources such as compute nodes and software licenses change between available and unavailable states without advance notice. This is particularly important with respect to ATHENa because it needs to be deployed in an environment where compute nodes are not necessarily dedicated to processing ATHENajobs and the availability of software licenses needed for the design tools being executed can change continually.

#### **Condor Pool**

Condor organizes the processes and compute resources at its disposal into what is referred to as a condor pool. A condor pool consists of a single machine known as the central server and an arbitrary number of machines that have joined the pool as either a submit or execute host. Conceptually the pool is a collection of resources and resource requests. The role of Condor is to match the requests to the appropriate resources for processing. All of the machines that are part of the Condor pool send periodic updates to the central server which is the centralized repository for all pool state information.

Each resource, or execute host within the Condor pool has an owner that defines the policies by which that particular resource will be used. These policies can include things such as the number of slots available to Condor and the software and licenses provided by the resource. Slots are analogous to processors and represent the number of jobs a resource will execute simultaneously. Condor can be configured to minimize the impact to an owner of a resource while in use or leverage as much processing power as possible. The policies and specific attributes of the resource are defined in Condor ClassAds.

Resource requests, or jobs are the units of work that are distributed to the execute hosts for processing. Each resource request has an owner, the individual who submitted the resource for execution. Resource requests are defined in Condor submit files that

represent the requirements that the resource request has. These requirements can be very simple or complex. A description of the Condor submit files and an example of one generated by ATHENa are in the appendix.

#### **Condor Master**

The condor\_master daemon is a software process that is responsible for maintaining the availability of the various software processes needed by a Condor pool running on all of the nodes within a condor pool.

### **Condor Startd**

The condor\_startd daemon is the process responsible for representing a computing resource to the Condor pool. It advertises the attributes and capabilities of a resource through the ClassAds defined by the owner of the resource. It is responsible for providing the information to the central manager that it needs to match resource requests to a particular resource. Condor\_startd will run on all machines in the condor pool that wish to be an execute host. When a resource request has been matched to the resource represented by condor\_startd it spawns the condor\_starter process as described below.

### **Condor Starter**

The condor\_starter process is the process that spawns the job that is to be executed remotely on an execute host. It sets up the environment needed by the job and monitors the job while it is running. It is also responsible for sending status about a job back to the submit host that submitted the job when the job completes.

### **Condor Schedd**

The condor\_schedd daemon is the process responsible for representing resource requests to the Condor pool. The condor\_schedd daemon needs to be running on any machine that wishes to play the role of a submit host in the Condor pool. The condor\_schedd stores all jobs submitted by users in a job queue that is managed by the schedd. The condor\_schedd advertises the jobs in the job queue to the Condor pool and is responsible for claiming the resources needed to serve the job requests. Once the condor\_schedd has been matched with a particular resource it spawns the condor\_shadow process as described below to serve the request.

### **Condor Shadow**

The condor\_shadow process is responsible for managing a remote job that is executing on a remote host. It handles file input and output for the remote job and handles retrieving the results produced by a remote job and delivering them to the submit host that submitted the job.

#### **Condor Collector**

The condor\_collector process runs on the central server of a Condor pool and collects all of the information about the state of the Condor pool. It is responsible for managing all of the ClassAd updates from the resources that comprise the pool. It also maintains the information needed for all submit hosts to communicate with all of the execute hosts in the pool.

#### **Condor Negotiator**

The condor\_negotiator is the intelligence that manages resources and resource requests within the pool. It is responsible for all matchmaking in the pool. The process that the negotiator uses to match resources and resource requests is known as a negotiation cycle. Periodically the negotiator begins a negotiation cycle where it queries the collector for the state of the pool. It then contacts each condor\_schedd that has jobs in its job queue and tries to match the pending jobs with available resources in the pool. The negotiator enforces the priorities of all users and jobs within the pool and users this information as a basis for scheduling. The negotiator runs on the central manager.

#### Roles

There are three roles that a machine can take on in a Condor pool with respect to ATHENa. These roles define what daemons and processes run on the machine and what capabilities the machine has. In addition to being able to take on a single role in the pool a machine can encompass multiple roles at once. A machine can be both a submit host and an execute host. A single machine pool can also be configured where a single machine takes on all roles and runs in isolation.

#### **Central Manager**

The central manager is the machine that contains the scheduling ability within the pool. It collects all of the state information about the resources provided by execute hosts

and the pending jobs offered by the submit hosts. It's job is to effectively match resource requests with the available resources while enforcing the policies provided by the ClassAds in the system. The processes that need to run on the central manager include the condor\_negotiator, the condor\_collector, and the condor\_master. A Condor pool generally contains a single central manager although it can contain more for redundancy in the case that the central manager becomes inoperable.

#### Submit Host

Submit hosts are machines that users submit jobs from. The submit hosts run the condor\_schedd daemon and host the condor\_shadow process for each remote job that has been submitted by that particular submit host. The submit host communicates pending jobs and their requirements to the Condor pool for consumption by the central server for matchmaking. It is also responsible for file I/O to the remote jobs that it manages.

### **Execute Host**

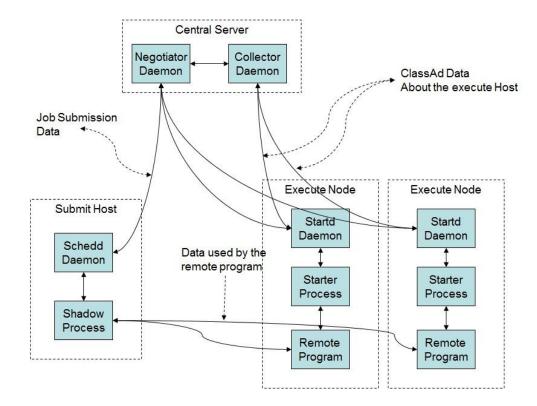

Execute hosts are machines in the Condor pool that actually process the resource requests made by submit hosts. The condor\_startd daemon and condor\_starter run on the execute hosts as well as the remote job specified by a resource request. The execute host communicates state and resource information to the central manager via Condor ClassAds. The execute host manages the jobs that are matched to it and provide job status to the central manager as well as the submit host that submitted the job. Figure 1 shows

the different roles within a condor pool and how they interact. The daemons that make up the roles are listed for each.

**Figure 1 Condor Roles**

# **ATHENa Client/Server Architecture**

Enhanced ATHENa was designed from the beginning to utilize parallelism as much as possible. The enhanced ATHENa software is developed in Python and follows object oriented design principles. The new design was divided into two distinct pieces, a client application where a user submitted benchmarking jobs, and a server side application that processes the jobs. The client application consists of a GUI for submitting and monitoring jobs. Information regarding each job is displayed as well as controls to pause, resume, and cancel existing jobs. Behind the GUI is an application that extracts the relevant information from the job configurations then sends the job to the server side application via the Condor batch system. The application will determine if a user submitted job can be broken up into independent subtasks for processing in parallel and send these subtasks to the batch system separately. The client application resides on a machine that takes on the submit host role within the system. The application generates Condor submit files for scheduling and interacts with the Condor daemons to schedule, process, and monitor the jobs submitted by a user. The new design space exploration algorithms that are explained in more detail to follow are also a part of the client application. By residing on the client, the algorithms can utilize the parallelism offered by Condor. Figure 2 and Figure 3 are screenshots of the GUI designed for the client application. Figure 2 shows the job monitoring table. The table lists what jobs have been submitted, by whom, and what state they are currently in. Figure 3 is the node monitoring table. It displays data on the connected execute hosts in the condor pool. Information is displayed about the operating system, CPU architecture as well as the state of the execute hosts.

| -       ben-laptop         1.3       Idle       0       ben@ben-laptop         1.2       Idle       0       ben@ben-laptop         1.1       Running       0       ben@ben-laptop         1.0       Running       0       ben@ben-laptop | ID | ▲ Status | Priority | Owner |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------|----------|-------|

| 1.2         Idle         0         ben@ben-laptop           1.1         Running         0         ben@ben-laptop                                                                                                                         |    |          |          |       |

| 1.1 Running 0 ben@ben-laptop                                                                                                                                                                                                             |    |          |          |       |

|                                                                                                                                                                                                                                          |    |          |          |       |

| 1.0 Running 0 ben@ben-laptop                                                                                                                                                                                                             |    |          |          |       |

|                                                                                                                                                                                                                                          |    |          |          |       |

Figure 2 Client GUI Submissions

Figure 3 Client GUI Execute Hosts

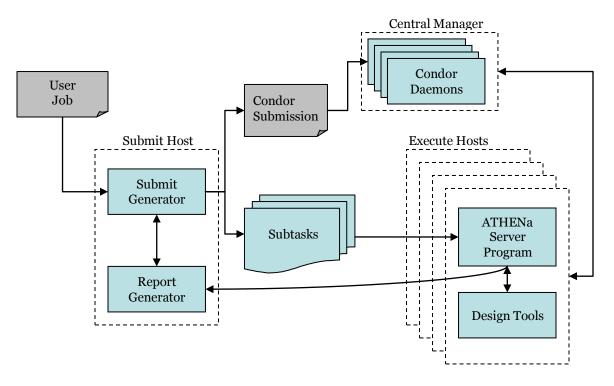

The server side application is very similar to the original ATHENa in design. It receives sets of configuration options and executes the synthesis and implementation tools with those options. The server side application is executed by the batch system when a job is submitted and matched to the compute node that the server side application resides on. The server application resides on a machine that takes on the Execute Host role in the system. Results are generated by the application and the batch system is notified of job completion and collects these results for transporting back to the machine that the user submitted the job from. Figure 4 shows the general dataflow and architecture of the combined ATHENa Condor Client/Server system. The User Job is the configuration file used as input by the user. The Submission generator extracts subtasks from thee User Job. These subtasks are described in the Condor Submission that is consumed by the Central Manager and used for matching the jobs to an appropriate execute host. The execute hosts communicate classAds as well as state information to the Central Manager to aid in the Match Making process. Once the jobs have been matched to execute hosts, the ATHENa server application executes the design tools with the proper command line options to generate results. Once the results are generated the server application packages the data for consumption by the client application for report generation.

Figure 4 Client/Server Architecture

## 6. RELATED TOOLS

There are other systems that aim to accomplish similar goals to the ones being accomplished with enhanced ATHENa. The main advantages of ATHENa over most other offerings are the multi-vendor device and tool chain support, optimization strategies aimed at maximum performance as opposed to design closure, and the automated extraction of results that integrates seamlessly with a results database.

### eBACS

eBACS (ECRYPT Benchmarking of Cryptographic Systems)[2], [3] is a system similar to ATHENa that focuses on the benchmarking of cryptographic primitives in software. Different processor architectures are evaluated as well as various compiler options. eBACS contains the eBATS(ECRYPT Benchmarking of Asymmetric Systems), eBASC(ECRYPT Benchmarking of Stream Ciphers), and eBASH(ECRYPT Benchmarking of All Submitted Hashes) systems. The eBASH portion of the system compares hashes, including the SHA-3 candidates utilized in the experiments for ATHENa. eBASH has already collected 51 implementations of 28 different hashes from 14 different families. These have been benchmarked on 69 different computers recompiled with 1201 different options. The system defines a standardized Application Programming Interface (API) for the supported cryptographic primitives. The goal of the system is to determine the best option set for each design on each machine architecture investigated. The concept and goal for ATHENa was inspired by the eBACS system, to remove the burden of generating high quality benchmarking results from the algorithm designer and generate benchmarking results in a clear unbiased manner for publication and comparison. The biggest difference between the systems is the software focus of eBACS. The job of optimizing the software algorithms is also simpler for eBACs because of their focus on one compiler, gcc. Software benchmarking and optimization also has an advantage in that one tool is used for optimization, the compiler, where with FPGA optimization there are multiple tools that need to be optimized to reach a final solution, Synthesis, Mapping, Placement, and more depending on the specific tool chain used.

#### Xilinx PlanAhead

Xilinx has developed an integrated design environment called PlanAhead that contains many similar features to ATHENa. The PlanAhead software allows multiple synthesis and implementation attempts using different options and constraints. The synthesis and implementation attempts can be queued to launch sequentially or simultaneously with multiprocessor machines using the Xilinx synthesis and implementation software. PlanAhead also can be deployed in a distributed cluster environment to increase the throughput of the benchmarking tasks. PlanAhead also contains predefined option sets for benchmarking purposes. One of the main differences between the optimization techniques employed by PlanAhead and those used by ATHENa is the isolation of each specific tool in PlanAhead. PlanAhead optimizes each stage of the tool chain in isolation, reducing the total number of runs to explore the same search space. Enhanced ATHENa has limited support for this capability, allowing each

tool to be run in isolation but providing little optimization algorithm support other than Most Effort optimization while in this mode. PlanAhead while similar to ATHENa does not support any other vendor device or tool chains limiting its use to Xilinx devices and tools alone.

### **Altera Design Space Explorer**

Design Space Explorer is a tool similar to Xilinx PlanAhead but integrated into the Quartus tools for use with Altera devices. It is meant to be an easy-to-use design optimization utility that can assist in optimizing a design in terms of power, area, and speed. A predefined set of Quartus II options are searched to determine optimal settings for a particular design. Different optimization targets are predefined that choose option sets to achieve performance relative to a given metric. Design Space Explorer can optimize for area, speed, and power. Design Space Explorer can also work on multiprocessor systems as well as distributed cluster environments. As with the Xilinx specific tool PlanAhead, Design Space Explorer only utilizes Altera devices and the Altera tool set to optimize designs.

### 7. OPTIMIZATION SPACE EXPLORATION

# **Least Effort**

Least effort optimization is not really an optimization method at all, but simply a method used to compare other algorithms against. Least effort consists of setting all options to their perceived high state. This enables us to compare the actual benefit of searching the option space more thoroughly. Running tests with this method will help establish a baseline for the minimum time that you can spend tuning and what sort of results you could expect. It serves as a useful baseline for comparison of all other optimization methods. The exact options and the states that are used are described in the case studies.

## **Most Effort**

Most effort optimization is comprised of an exhaustive search of all option combinations within the option search space. An exhaustive search will yield the optimal option set for the design but places an enormous burden on resources by requiring that all option combinations be tested. An exhaustive search requires  $2^n$  runs to test the entire option search space for on/off options where *n* is the number of options being investigated. While limited in use it is incredibly powerful for a small search space and

will be used to compare the effectiveness of the other algorithms using a constrained set of options.

### **Batch Elimination**

The Batch Elimination algorithm proposed here is adapted from previous research in compiler option selection [8]. Batch elimination is an algorithm that aims to approximate an exhaustive search of the optimization options in a much more efficient manner. The benefit of this algorithm is that it requires onlyn + 2optimization combinations to complete, (with n being the number of options), a significant savings compared to exhaustive search. While significantly faster than an exhaustive search, there is no guarantee that an optimal combination will be discovered. It will be shown through experimentation that a near optimal solution can be achieved if there is minimum interaction between options for the tested design.

The algorithm itself is quite simple in design. The effect of one option,  $O_i$  is represented by a metric called Relative Improvement Percentage,  $RIP(O_i)$ , which is the difference in performance relative to a chosen metric of the benchmark with and without option  $O_i$ .  $P(O_i = 0)$  is the performance measured when the option is off, and  $P(O_i = 1)$  is the performance measured when the option is on.

#### **Equation 1 Relative Improvement**

$$RIP(O_i) = \frac{P(O_i = 1) - P(O_i = 0)}{P(O_i = 0)} \times 100\%$$

The baseline used for comparison is the performance of the design with all options switched off. The relative improvement of an option as compared to the baseline is defined as:

**Equation 2 Relative Improvement Baseline**

$$RIP_B(O_i) = \frac{P(O_i = 1) - P_B}{P_B} \times 100\%$$

If,  $RIP(O_i = 1) > 0$ , the option  $O_i$  has a positive effect. The Batch elimination algorithm enables this option in the final option set. The pseudo code for the algorithm is as follows:

- 1. Run the FPGA synthesis and implementation tools using the baseline option set (all options set to off) to generate  $P_B$ .

- 2. For each option being investigated  $O_i$ , switch the option on and run the synthesis and implementation tools to generate  $P(O_i = 1)$ . Determine  $RIP(O_i = 1)$ .

- 3. Enable all options with positive RIPs. Run the synthesis and implementation tools with this tuned option set to determine the final performance metric.

The options are not limited to binary on/off option types as shown above and can be n-ary in nature. In the case of an n-ary option performance is calculated for each option state  $P(O_i=1)$ ,  $P(O_i=2)$ , ...  $P(O_i=n)$  and the option state with the greatest RIP is used in the final option set. To help illustrate the example Table 2 represents the option set at each step of the batch elimination algorithm. 0 represents the default option where a 1 represents a non-default option state. A + for the Relative improvement denotes an improvement over the baseline and a – denotes none, or negative impact.

| Table 2 Batch Elimination |

|---------------------------|

|---------------------------|

|     | Option | Option | Option | Option | Option | Relative    |

|-----|--------|--------|--------|--------|--------|-------------|

| Run | 1      | 2      | 3      | 4      | 5      | Improvement |

| Ob  | 0      | 0      | 0      | 0      | 0      | N/A         |

| 01  | 1      | 0      | 0      | 0      | 0      | +           |

| 02  | 0      | 1      | 0      | 0      | 0      | -           |

| O3  | 0      | 0      | 1      | 0      | 0      | -           |

| 04  | 0      | 0      | 0      | 1      | 0      | +           |

| O5  | 0      | 0      | 0      | 0      | 1      | +           |

| Of  | 1      | 0      | 0      | 1      | 1      | N/A         |

Note: 1 Ob is the baseline, Of is the final run

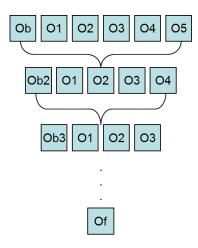

Batch Elimination takes n+1 runs of the design tools to complete where n is the number of options being investigated but can be completed in the equivalent of 2 runs by utilizing n compute resources. Figure 5 illustrates the task decomposition of the Batch Elimination algorithm. *Ob* is the baseline and *O1-O5* are the runs representing the optios being investigated.

Figure 5 Batch Elimination Parallel Task Decomposition

#### **Iterative Elimination**

Iterative elimination is a modification to the previously defined batch elimination that takes into account the interaction of optimizations into consideration. The price that is paid to deal with interactions is an increase in algorithm time complexity. Iterative elimination performs the RIP calculation described in batch elimination for each option but then only sets the most beneficial option at a time, creating a new baseline and continuing the process iteratively until options no longer yield a positive RIP. Iterative elimination requires at most  $n * \frac{n}{2} + \frac{n}{2}$ runs to complete while on average it can be much less. The following pseudo code describes the algorithm in more detail.

- 1. Run the FPGA synthesis and implementation tools using the baseline option set (all options set to off) to generate  $P_B$

- 2. For each option being investigated O<sub>i</sub>, switch the option on and run the synthesis and implementation tools to generate P(O<sub>i</sub>=1). Determine the RIP(O<sub>i</sub> = 1).

- 3. Find the option  $O_i$ , that has the greatest RIP. Create a new baseline with this option set to on instead of off.

- 4. Repeat the previous steps until there is no positive RIP for any option.

The final baseline will represent the fully optimized option set. To help illustrate the example Table 3 represents the option set at each step of the iterative elimination algorithm. 0 represents the default option where a 1 represents a non-default option state. A + for the Relative improvement denotes an improvement over the baseline and a -

denotes none, or negative impact.

#### **Table 3 Iterative Elimination**

| Run | Option 1 | Option 2 | Option 3 | Option 4 | Option 5 | Relative<br>Improvement |

|-----|----------|----------|----------|----------|----------|-------------------------|

| Ob  | 0        | 0        | 0        | 0        | 0        | N/A                     |

| 01  | 1        | 0        | 0        | 0        | 0        | +5                      |

| O2  | 0        | 1        | 0        | 0        | 0        | -                       |

| O3  | 0        | 0        | 1        | 0        | 0        | -                       |

| O4  | 0        | 0        | 0        | 1        | 0        | +7                      |

| O5  | 0        | 0        | 0        | 0        | 1        | +2                      |

| Ob2 | 0        | 0        | 0        | 1        | 0        | +7 from<br>baseline 1   |

| 01  | 1        | 0        | 0        | 1        | 0        | +3                      |

| 02  | 0        | 1        | 0        | 1        | 0        | -                       |

| 03  | 0        | 0        | 1        | 1        | 0        | -                       |

| 04  | 0        | 0        | 0        | 1        | 1        | +1                      |

| 0b3 | 1        | 0        | 0        | 1        | 0        | +3 from<br>baseline 2   |

| 01  | 1        | 1        | 0        | 1        | 0        | -                       |

| O2  | 1        | 0        | 1        | 1        | 0        | -                       |

| O3  | 1        | 0        | 0        | 1        | 1        | -                       |

| Of  | 1        | 0        | 0        | 1        | 0        | +10 total               |

Iterative Elimination can take as little as n + n - 1 runs of the design tools to complete and up to  $n * \frac{n}{2} + \frac{n}{2}$  where *n* is the number of options being investigated. The algorithm can be realized in at most *n* runs if there are at least n compute resources available. Figure 6 illustrates the task decomposition of Iterative elimination. The ellipses is used to signify the unknown number of runs required to complete the optimization. *Ob*- *Obn* represent the baselines used at each step of the Iterative Elimination process. *Of* represents the final optimized option state.

Figure 6 Iterative Elimination Parallel Task Decomposition

# **Orthogonal Array**

Orthogonal arrays have been used as an efficient means to design experiments in many fields of engineering. Recent research has been done using orthogonal arrays as a means to choose gcc compiler options, an application that mirrors ours [9], [10]. In our experiment we have n factors being considered creating an optimization space with  $2^n$  settings. This is known as a full factorial design. As n increases, it is not possible to test the entire search space to determine the optimal option combination. Orthogonal arrays are a means to create an experiment that is called a fractional factorial design, allowing meaningful information to be determined about option combinations while searching only a fraction of the full factorial design optimization space. An Orthogonal Array is an  $N \times k$  matrix where the columns represent optimization options and the rows represent the settings used for each experiment. The matrix is filled with 1's and 0's to represent whether or not a specified option is on or off. The property that makes Orthogonal Arrays useful for creating fraction factorial designs is that any two arbitrary columns contain the patterns {00, 01, 10, 11} equally often. An Orthogonal array of this type is said to be of strength 2, referring to the two column patterns. A strength 2 array allows the discovery of main effects for options, similar to the non-interacting option detection that is used in batch elimination. The effect of options interacting among one another can be analyzed with greater strength Orthogonal Arrays and should achieve results similar to iterative elimination. An example of an Orthogonal Array of strength 2 is shown with eight rows corresponding to eight separate experiments, or sets of options. The array contains five columns, representing a search space of five options. Figure 7 shows the orthogonal array used in the Orthogonal Array Optimization implementation demonstrated in this thesis.

| 1 | 0 | Ο | Ο | 0 |

|---|---|---|---|---|

| 0 | 1 | 0 | 1 | Ο |

| 1 | 1 | 1 | Ο | 1 |

| 0 | Ο | 1 | 1 | 1 |

| 1 | Ο | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | Ο |

| Ο | Ο | 1 | 1 | Ο |

Figure 7 Orthogonal Array