Edited by Bill Travis and Anne Watson Swager

# Neat idea nets \$1500 in *EDN*'s yearly Design Ideas contest

*EDN* is pleased to announce this year's \$1500 grand-prize winner for Design Ideas: Art Hogrefe of State College, PA, a consultant who specializes in communications and analog-circuit design. He takes the honor for "Inverted bipolar transistor doubles as a signal clamp," which was published in *EDN*'s Nov 9, 2000, issue. In case you missed it the first time around, you can read all about it below.

In Hogrefe's innovative idea, he uses a bipolar transistor in an inverted configuration as a rectifier, or clamp, with low forward voltage. He offers a meticulously thorough comparison of the characteristics of the transistor versus those of a germanium diode. The idea of using bipolar transistors in an inverted mode is not new: these devices were pop-

ular as low-offset switches in R/2R ladder networks in D/A converters in the 1960s and 1970s. In his eminently useful Design Idea, Hogrefe takes the application a step further and thoroughly characterizes the bipolar transistor's attributes as a low-offset clamp and rectifier. Check it out for yourself.

And be sure to send us your own Design Idea. *EDN* publishes about 150 Design Ideas per year, and each one is automatically entered into a best-of-issue and year-end competition. You can find guidelines at www.ednmag.com/ednmag/write\_di.htm along with a coupon to email submissions or use the coupon on pg 152 to submit your ideas by mail.

# Inverted bipolar transistor doubles as a signal clamp

Art Hogrefe, Puma Instrumentation, State College, PA

A NUMBER OF CIRCUITS, such as level detectors and AM demodulators, benefit from a rectifier with a low offset voltage. Silicon diodes have an offset of approximately 0.6V and do not work well in low-level circuitry. A Schottky diode is a bit better with an offset of approximately 0.4V. A few germanium diodes are still available, but they do not tolerate the temperature range of silicon. Also, you can't include a germanium diode in an IC. A superior configuration uses a bipolar transistor for these applications.

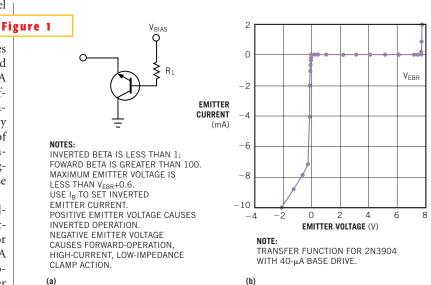

Figure 1 shows the bipolar-invertedclamp circuit and a typical transfer function. The collector connects to ground or any other desired reference voltage. A fixed current drives the base. In the absence of any external drive, the emitter voltage is near zero. Driving the emitter with an external voltage produces the transfer function in Figure 1.

The bipolar inverted clamp (a) has an excellent rectification characteristic (b) because of the 2N3904's large forward-beta-to-reverse-beta ratio.

The circuit achieves this excellent rectification characteristic by using a transistor with a large forward-beta-to-reverse-beta ratio. Many of these transistors are still available. The 2N3904 provides excellent characteristics at a low cost. The reverse beta of the 2N3904 is only 0.25, so that for positive voltage on the emitter, and, with 40  $\mu$ A of base drive, the emitter, current is around 10  $\mu$ A. This current is sufficient in most level-detector applications for which the ac input amplitude changes slowly.

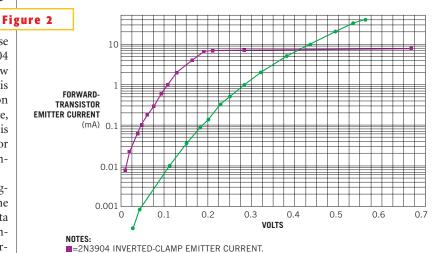

The emitter current at even small negative voltages is much greater than in the inverted region because the forward beta of the 2N3904 is greater than 100. Impedance is low up to the beta-limited forward current, at which point the impedance increases to approximately the value of R<sub>1</sub>/beta. **Figure 2** shows the forward-transistor emitter current of the 2N3904 and the forward current of the 1N34 germanium point-contact diode. The logarithmic current scale shows the impressive response of the 2N3904 at small voltages.

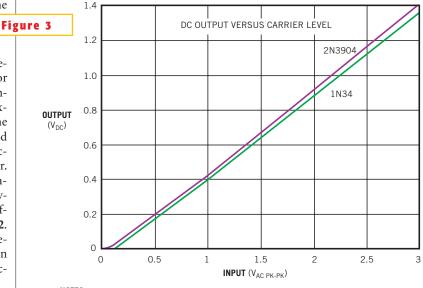

Figure 3 shows the output as a level detector for the two clamps. The transistor circuit that produced these results is similar to the demodulator in Figure 4 except the base drive is 40 µA. For the 1N34, the anode connects to ground, and the cathode connects to the input capacitor in place of the transistor's emitter. Figure 3 shows that the two configurations have similar responses to input levels and that the 2N3904 has a bit less offset, as you would expect from Figure 2. The output can drive a signal level meter or following electronics as part of an automatic-level-control or automaticgain-control loop.

The transfer function in **Figure 1** also shows a sudden increase in inverted current at approximately 7.6V, which occurs at the reverse breakdown voltage for the emitter-to-base junction. Because you know in this case that the base is near 0.6V, the breakdown voltage for the tested part is near 7V. Production circuits would have an input limit of 6.6V p-p because of the minimum specified breakdown voltage of 6V. Note that, for a small

A logarithmic scale of the 2N3904's forward-transistor emitter current and the forward current of the 1N34 show the impressive response of the 2N3904 at small voltages.

=1N34 GERMANIUM-DIODE FORWARD CURRENT

**NOTES:** FOR 2N3904,  $V_{DC}$ =0.5 $V_{AC}$ -0.08, AND  $I_{BASE}$ =41  $\mu$ A. FOR 1N34,  $V_{DC}$ =0.5 $V_{AC}$ -0.11.

When operating as demodulators, the two configurations have similar input-level responses.

production, such as for test equipment, it is practical to select individual transistors to slightly increase the dynamic range. A 6V p-p input dynamic range is sufficient in many applications.

The RF demodulator in Figure 4 has

a base drive current of 300  $\mu$ A. This current is necessary to track the RF-modulation envelope and depends on the size of the input capacitor, modulation frequency, and maximum signal amplitude. The reverse current, which is  $I_{BASE}$  times

150 EDN | JUNE 7, 2001 www.ednmag.com

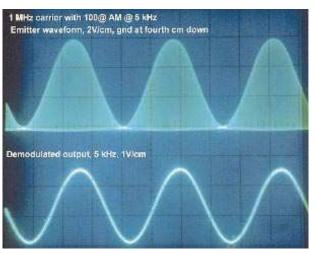

the reverse beta, must be large enough to discharge the input capacitor at the highest modulation frequency and amplitude to prevent distortion in the output waveform. Figure 5 shows the running demodulator with the upper trace at the emitter node and the lower trace at the output.

Figure 4 1-MHz CARRIER WITH 100% AMPLITUDE MODULATION AT 5 kHz 120k O OUTPUT 1 nF

NOTES:

BASE-DRIVE CURRENT IS 300 μA, EMITTER REVERSE CURRENT IS APPROXIMATELY 75 LA.

2N3904 FORWARD BETA IS GREATER THAN 100: REVERSE BETA IS APPROXIMATELY 0.25.

EMITTER-BASE REVERSE-BREAKDOWN VOLTAGE IS GREATER THAN 6V.

AC-DRIVE VOLTAGE IS LESS THAN 6.6V P-P.

Using the inverted clamp as an AM demodulator requires a base current of 300 µA to track the RF-modulation envelope.

Figure 5

A scope photo shows the running demodulator: the upper trace is the emitter node, and the

lower trace is the output.

#### **Design Idea Entry Blank**

Entry blank must accompany all entries. \$100 Cash Award for all published Design Ideas. An additional \$100 Cash Award for the winning design of each issue, determined by vote of readers. Additional \$1500 Cash Award for annual Grand Prize Design, selected among biweekly winners by vote of editors. Find the entry blank at http://www.ednmag.com/ednmag/di entry.htm to email submissions.

To: Design Ideas Editor, EDN Magazine 275 Washington St, Newton, MA 02458

I hereby submit my Design Ideas entry. (Please print clearly)

Title

\_\_\_\_\_ Fax \_\_\_\_ E-mail \_\_

Company \_\_\_\_\_

Address \_\_\_

\_\_\_\_\_ Zip \_\_\_\_\_ Country \_\_\_

Design Idea Title \_\_\_\_\_

Entry blank must accompany all entries. (A separate entry blank for each author must accompany every entry.) Design entered must be submitted exclusively to EDN, must not be patented, and must have no patent pending. Design must be original with author(s), must not have been previously published (limited-distribution house organs excepted), and must have been constructed and tested. Fully annotate all circuit diagrams. Please submit text, software listings, and all other computer-readable documentation on a PC disk by mail or by e-mail to b.travis@cahners.com.

Exclusive publishing rights remain with Cahners Business Information unless entry is returned to author, or editor gives written permission for publication elsewhere. The author must be willing to sign and return our publication agreement if the Design Idea is accepted for publication and must complete a W-9 tax form (W-8 for non-US residents) before payment can be processed.

| Signed _ |  |  |  |  |

|----------|--|--|--|--|

| a.g.     |  |  |  |  |

| Data     |  |  |  |  |

www.ednmag.com

152 EDN | JUNE 7, 2001

## Stepdown converter uses a ceramic output capacitor

Karl R Volk, Maxim Integrated Products, Sunnyvale, CA

ANY STEPDOWN (BUCK) dc/dc-converter ICs incorporate a voltage-mode-control algorithm. As a result, for stable operation in continuous-conduction mode, the application circuit's output capacitor is normally a high-ESR tantalum type for two reasons. The portion of output ripple due to ESR provides the current-mode signal that's necessary for cycle-to-cycle stability. In the frequency domain, this capacitor also provides a zero that cancels a pole in the buck converter's second-order LC filter, thereby shifting operation back to the stable region by reducing the ripple's phase shift to less than 90°.

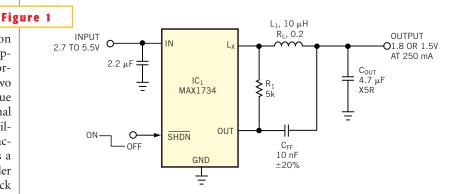

The circuit in **Figure 1**, however, allows the use of an inexpensive ceramic output capacitor. To remove the effects of phase lag in the feedback loop, the circuit derives feedback from the  $L_x$  pin, via the first-order RC filter comprising  $R_1$  and  $C_{\rm FF}$  instead of the output. Connecting the tail of  $C_{\rm FF}$  to the output node instead of to ground, as you would for a normal filter, provides a fast "feedforward" load-transient response.

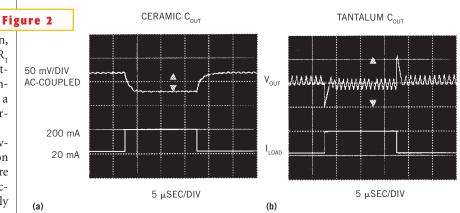

A ceramic-capacitor circuit offers several benefits over a standard application circuit. First, ceramic capacitors are more reliable than tantalum capacitors. Second, ceramic capacitors are more readily available than tantalum types. Third, ceramic capacitors cause output ripple of less than 5 mV p-p versus more than 20 mV p-p (**Figure 2**). For this circuit, the

A stepdown dc/dc converter, which normally requires a tantalum output capacitor, can operate with a ceramic output capacitor by deriving feedback from the  $L_v$  pin via the  $R_v/C_{\rm EE}$  filter.

Load-transient response waveforms show that using a ceramic output capacitor produces lower output ripple and less overshoot (a) than the standard application circuit with a tantalum output capacitor (b).

load-transient overshoot is also lower: less than 50 mV p-p versus more than 100 mV p-p.

IC<sub>1</sub>, a stepdown dc/dc converter with an internal synchronous rectifier that supplies a fixed 1.8 or 1.5V output at 250 mA from an input range of 2.7 to 5.5V, needs 20 mV p-p or more at its output pin for stable operation under load. To meet this requirement, calculate the value of R<sub>1</sub>:

$$R_1 \cong \left(\frac{20 \text{ mV}}{2 \times V_{OUT}}\right) \left(\frac{L_1}{T_{MIN}}\right) \left(\frac{I_{LOADMAX}}{2 \times I_{OUTSENSE}}\right).$$

Per the data sheet for the MAX1734,  $V_{OUT}$  is 1.5 or 1.8V,  $L_1$  is 10  $\mu$ H,  $T_{MIN}$  is 0.4

μsec,  $I_{LOADMAX}$  is 250 mA, and  $I_{OUTSENSE}$  is 4 μA. The result is  $R_1$ =4.3 k $\Omega$  for  $V_{OUT}$ =1.8V, and  $R_1$ =5.2 k $\Omega$  for  $V_{OUT}$ =1.5V. You can therefore round  $R_1$  to 5 k $\Omega$ .

Next you calculate the feedforward capacitor value:

$$C_{FF} \le \left(\frac{2 \times V_{OUT}}{20 \text{ mV}}\right) \left(\frac{T_{MIN}}{R_1}\right).$$

If  $R_1$ =5 k $\Omega$  and  $V_{OUT}$ =1.5V, then  $C_{FF}$ =12 nF. Select  $C_{FF}$ =10 nF. Choosing a much smaller value causes excessive load-transient overshoot, and choosing a larger value causes instability under loaded conditions. For optimized load

transients, the inductor series resistance should be as follows:

$$R_L \cong \frac{L_1}{R_1 \times C_{FF}}$$

.

Note that this expression is the typical, not the maximum, inductor resistance. In this case, the value of  $R_{\rm L}$  should be approximately 200 m $\Omega$ , which allows you to use a small inductor and causes an approximate efficiency drop of only 3% at maximum loads and much less at lighter loads. Because the inductor time constant,  $L_{\rm l}/R_{\rm L}$ , matches the feedback time constant,  $R_{\rm l}\times C_{\rm FF}$ , the short-term load-transient response equals the dc load regulation (**Figure 2**). If  $R_{\rm L}$  is less

than 200 m $\Omega$ , the peak-to-peak load-transient voltage increases, but the dc-load regulation decreases.

Finally, choose  $C_{\text{OUT}}$  large enough for stability:

$$C_{OUT} \ge 2 \times \left(\frac{\Delta I_L}{20 \text{ mV}}\right) \times T_{MIN},$$

where  $\Delta I_{\rm L}$  is approximately 100 mA when the MAX1734 operates with a 10- $\mu$ H inductor. In this case,  $C_{\rm OUT}$  should be greater than 4  $\mu$ F.

Is this the best Design Idea in this issue? Vote at www.ednmag.com/edn mag/vote.asp.

#### Single printer-port pin acts as an encoder output

Haobin Dong, Huazhong University of Science and Technology, China

NCODERS AND DECODERS are common elements in alarm, re-Figure 1 mote-control, and measurement systems. However, most of these ENCODER devices require many I/O lines when under microprocessor or PC control. For example, the HT-12E encoder has eight At power-up, the HT-12E encoder begins a 4-word transmission cycle. address pins, four data pins, and one transmit-enable-control pin. As an alternative, you can simulate the HT-Figure 2 12E using a single pin of a PC's printer port as the encoder output. Soft-ONE-THIRD-BIT ware determines the functions of the en-SYNC PERIOD DATA-CODE coder. ADDRESS-CODE PERIOD 12-BIT PILOT PERIOD

One complete transmission period includes a pilot period, a bit-sync period, an address-code period, and a data-code period.

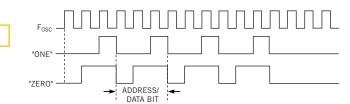

The HT-12E is a CMOS IC. This encoder serially transmits data as defined by the state of the  $A_0$  to  $A_7$  and  $D_0$  to  $D_3$  input pints. On power-up, the  $D_{OUT}$  pin is low. The HT-12E begins a 4-word transmission cycle on receipt of a transmission enable, or TE, signal, which is active low. The cycle repeats as long as the TE signal is low. When TE goes high, the encoder completes its final 4-word transmission cycle and then stops (Figure 1).

You can preset the status of each address or data pin independently to logic high or low. If the TE signal is low, the encoder scans and sequentially transmits

the status of the 12 bits of address and data in the order of  $A_0$  to  $A_8$  and  $D_0$  to  $D_3$  (**Figure 2**).

The IC encodes each logic high or low into pulses (**Figure 3**). The encoder represents a logic low as a long pulse (011) and a logic high as a short pulse (001). Every logic bit takes three OSC periods. The information sequentially transmits via the D<sub>OUT</sub> pin.

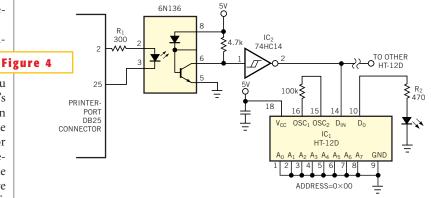

**Figure 4** shows the test circuit for a virtual encoder that includes an optocou-

pler and the decoder,  $\rm IC_1$ . The encoder output comes from printer Port Pin 2 of the DB25 connector. The data port is at address 0x378h of the PC's LPT.  $\rm R_1$  limits drive current from the PC's printer port.  $\rm IC_2$ 's Schmitt trigger shapes the optocoupler's output. The  $\rm D_0$  pin of  $\rm IC_1$  connects to  $\rm R_2$  and an LED.

According to **Figure 2** and **Figure 3**, one complete transmission period consists of 73 OSC periods. The pilot period, which is 12 bits, is all logic low (0, 36

156 EDN | JUNE 7, 2001 www.ednmag.com

OSC periods) followed by a one-third-bit sync period (one OSC). After those periods follows 8 bits of address and 4 bits of data, all of which need 36 OSC periods. Every bit of address or data is either a "001" encoded pulse for a logic high or a "011" for all other cases. A time interval exists between two pulses, and a software loop controls the interval. Also, the interval must be in accordance with the OSC periods of the decoder.

Software listings consist of implementation routines in Turbo C, the main code for determining the delay time, and a test-program site. You can download the listings from EDN's Web site, www.ednmag.com. Click on "Search Databases" and then enter the Software Center to download the file for Design Idea #2713. The delay time, T\_delay, is a global variable in the codes. The variables T\_min, T\_max, and T\_step are properly predefined based on the PC. After you compile and execute the delaytime program, the T\_delay value is read when the LED starts to flash. The value for the current design and the PC is 1000. Compile and run the test program, and

A short pulse of "001" represents a logic high, or a "one," and a long pulse of "011" represents a logic low, or a "zero."

A test circuit includes an optocoupler and a decoder IC.

you will observe that the LED continues to flash until you hit any key to stop the code.

Is this the best Design Idea in this issue? Vote at www.ednmag.com/edn mag/vote.asp.

#### VFC makes simple capacitance meter

K Suresh, Indira Gandhi Centre for Atomic Research, Kalpakkam, India

HEN YOU DEVELOP the prototype of a circuit using capacitors or when you replace an old, defective capacitor with a new one, you often need to know the value of the capacitor you use or replace. At times, the values printed on the capacitors are no longer readable. Also, the wide tolerance band of the capacitors can leave you making a wild guess about the capacitor value. In these situations, you normally go looking for an LCR bridge of a DMM with a capacitance-measurement facility. Not all DMMs have this feature, and finding the capacitance value from an LCR bridge is a cumbersome process.

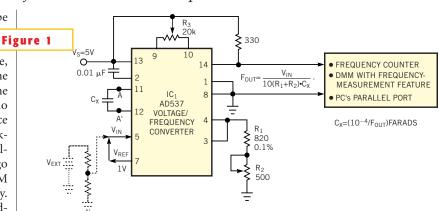

An alternative is a simple, low-cost VFC (voltage/frequency converter) with a few inexpensive components (**Figure 1**). This circuit can measure capacitance values of nanofarads to tens of microfarads. The output transfer function is

A simple VFC uses its internal reference to produce a serial pulse train whose frequency is inversely proportional to unknown capacitance  $C_{\chi^*}$  Options for measuring the VFC's output include: using a frequency counter, using a DMM with a frequency-measurement feature, and hooking the output to a PC parallel port through simple counters and buffers.

$$F_{OUT} = \frac{V_{IN}}{10(R_1 + R_2) \times C} Hz,$$

where  $V_{IN}$  is in volts,  $R_1$  and  $R_2$  are in ohms, and C is in farads. For  $IC_1$ , with an input range of 0 to 10V, the output of the

VFC is a serial pulse train in the frequency range of 0 to 150 kHz with a nonlinearity error of less than 0.05%.

In normal operation of the VFC, you provide a  $V_{\rm IN}$  of 0 to 10V and choose  $R_1$  and  $R_2$  such that you get  $V_{\rm IN}/(R_1+R_2)$ , a current range of 0 to 1 mA to obtain a good linearity between  $V_{\rm IN}$  and  $F_{\rm OUT}$ . However, in this design, there is no external input to the VFC. Instead, the design exploits an internal reference voltage,  $V_{\rm REF}$ , by simply connecting the  $V_{\rm REF}$  output to the  $V_{\rm IN}$  input. To avoid the possibility of loading the reference source, you can also apply  $V_{\rm REF}$  to  $V_{\rm IN}$  through a buffer. Also, you can use an external voltage input from a constant voltage source, such as a battery, and connect it, as the dotted lines in the figure indicate.

To measure an unknown capacitance value, you connect the capacitor between terminals A and A' very close to the VFC. With  $V_{\rm IN} = V_{\rm REF} = 1.00 {\rm V}$  and  $R_1 + R_2$  trimmed to  $1~{\rm k}\Omega$ , the resulting output of the VFC is a serial pulse train whose frequency varies inversely with the value of the unknown capacitance  $C_{\rm X}$  as follows:

$$C_{X} = \frac{10^{-4}}{F_{OUT}} \text{FARADS.}$$

You use the  $R_3$  and  $R_2$  trims to obtain calibrations at the higher and lower ends of the capacitance range, respectively. Thus, after due calibration, a 1-Hz output of the VFC indicates the unknown capacitance as 100  $\mu$ F, and the maximum output of the VFC, 150 kHz, indicates that the capacitance is approximately 0.6 nF. If you want to increase the measurable capacitance range, you use a VFC with a wider output-frequency range, such as 0 to 1 MHz. In this case, you must take care of the parasitic capacitances.

You can measure the output of Figure 1's circuit in a number of ways. One simple and direct approach is to use a simple frequency counter or a low-cost DMM with a frequency-measuring feature. Thus, the simple VFC becomes a handy capacitance interface for your DMM to enable you to measure the capacitance. Alternatively, you can also use a programmable counter, such as the Intel 8254, which is available in most PC add-on cards. One more approach is to attach a simple 16-bit counter, such as the CD4040 and CD4520, to your printer port using the necessary buffering and control (Reference 1). In the last two cases, you can exploit a special BIOS interrupt, INT1Ch of your PC, without affecting its normal service routine to provide a measuring window of 1 second. During the measuring window, the serial output of the VFC drives a counter. A the end of the measuring window, the counter contents transfer to the PC, and you manipulate the data to display the unknown capacitance value directly on the PC's screen.

#### REFERENCE

1. "Use your printer port as a high-current ammeter," *EDN*, July 6, 2000, pg 144.

Is this the best Design Idea in this issue? Vote at www. ednmag.com/ednmag/vote.asp.

160 EDN | JUNE 7, 2001 www.ednmag.com