# ERCIM

European Research Consortium for Informatics and Mathematics www.ercim.org

Number 52

January 2003

# Special: Embedded Systems

### Contents

### JOINT ERCIM ACTIONS

- 4 ERCIM New European Host of W3C

- 5 About the World Wide Web Consortium

- 5 W3C Activities

- Recommendations published by W3C in 2002

- 7 World Wide Web Consortium launched Hungarian Office at SZTAKI by László Kovács and Éva Megyaszai, SZTAKI

- 8 Human Resources Managers Task Force by José Koster, CWI and Heather Weaver, CLRC

- 8 Euro-Legal by Heather Weaver, CLRC

- Andreas Rauber Winner of the 2002 Cor Baayen Award

Cover:

The European Ariane 5 launcher crashing after takeoff on 4 June 1996. The explosion was the result of a software error. Embedded systems play an important role in many safety critical systems.

Photo: courtesy by AFP.

Next issue: April 2003

Special theme: Cognitive Systems

### SPECIAL THEME

- **10 Embedded Systems Introduction** by Erwin Schoitsch, ARC Seibersdorf Research (AARIT)

- 12 An Approach to Dependable Architectures and Components for Railways by Andrea Bondavalli, Felicita Di Giandomenico and Luca Simoncini, ISTI-CNR

- **13 Monitoring and Controlling Scientific Experiments: Anywhere - Anytime** by Christian Wattinger, Peter Fornaro, Martin Guggisberg,

Tibor Gyalog, and Helmar Burkhart, University of Basel (SARIT)

- 15 Emerging Frontiers in Miniature Computer and Embedded Systems by Angelos Bilas and Evangelos Markatos, ICS-FORTH

- **16 Wearable Systems for Everyday Use** by Spyros Lalis, Anthony Savidis and Constantine Stephanidis, ICS-FORTH

- 18 New Solutions for In-Vehicle Embedded System Development

by Françoise Simonot-Lion, Laboratoire Lorrain de Recherche en Informatique et ses Applications, France and Yvon Trinquet, Institut de Recherche en Cybernetique de Nantes, France

- 20 Remote Control and Monitoring over the Internet -Wireless Construction Site by Leila Rannanjärvi, VTT

- 21 Creating a Network for Those working with Embedded and Real-Time Systems by Barrie Ross-Dow, Institute of Electrical Engineers, UK

- 22 DECOS Dependable Embedded Components and Systems by Dieter Donhoffer and Erwin Schoitsch,

ARC Seibersdorf Research (AARIT)

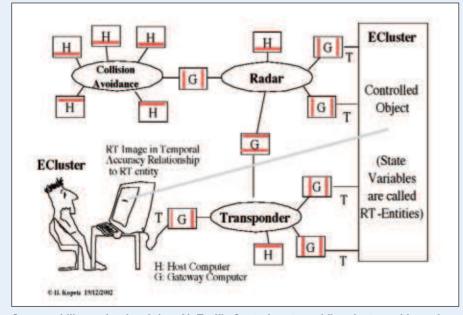

- 24 Time Triggered Architecture by Hermann Kopetz, Vienna University of Technology, Austria

- **26 Automatic Distribution of Synchronous Programs** by Alain Girault, INRIA

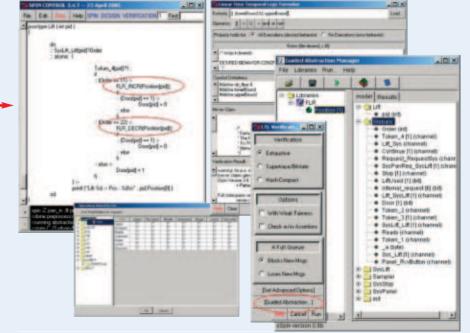

- 28 synERJY: a High-Level Language for Embedded Controllers by Reinhard Budde, Axel Poigné and Karl-Heinz Sylla, Fraunhofer-Gesellschaft

ERCIM has been chosen as European host of the World Wide Web Consortium (W3C). Read about this event and the W3C on pages 4-7.

29 STOREQ: Storage Requirement Estimation and Optimisation Tool for Data-Intensive Embedded Applications

by Per Gunnar Kjeldsberg, NTNU

- **31 Composing Embedded Real-Time Software Components: the PECOS Data-Centric Approach** *by Stéphane Ducasse, Oscar Nierstrasz and Roel Wuyts, University of Berne (SARIT)*

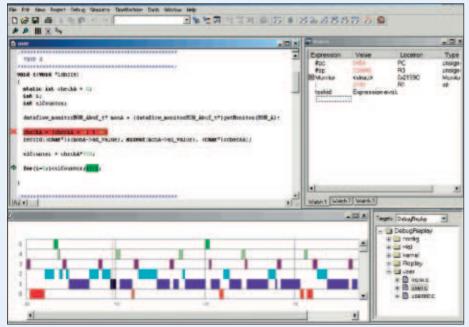

- 32 Time Machines and Black Box Recorders for Embedded Systems Software by Henrik Thane, Malardalen University, Sweden

- **33 Design of Embedded Systems: New Challenges** by Gilbert Cabillic and Isabelle Puaut, INRIA

- **35 Transforming Specifications to verify Embedded Systems** by María del Mar Gallardo, Jesús Martínez, Pedro Merino and Ernesto Pimentel, University of Malaga, Spain

- **36 EUDEMES: Component-Based Development Methods for Small-Size Embedded Systems** *by Nicolas Guelfi, Luxembourg University of Applied Sciences (FNR), Aloyse Schoos, IEE S.A, Luxembourg, Gérard Sébastien and François Terrier, National Institute of Nuclear Sciences and Techniques (CEA), France*

- 37 Model Checking of Embedded Systems by Stefania Gnesi, ISTI-CNR

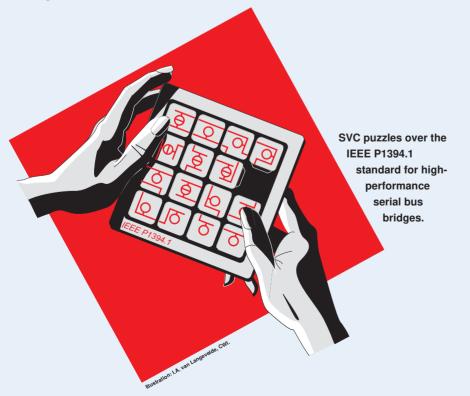

- **39** Systems Validation Centre shows Benefits of Formal Methods

by Henk Eertink, Telematica Instituut, Wan Fokkink, CWI, Holger Hermanns, University of Twente, and Izak van Langevelde, CWI

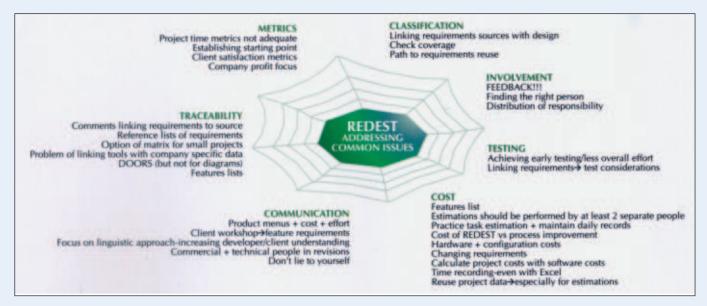

- 40 REDEST Sharing Experiences in the Field of Embedded Software Requirement Gathering by János Nacsa, SZTAKI

- **42 EmbLab A Laboratory for Teaching Embedded Systems** *by Amund Skavhaug, Trygve Lunheim and H. Skinnemoen, NTNU*

- **43 Master Course Embedded Systems at Eindhoven University of Technology** *by Jan Friso Groote, Eindhoven University of Technology, The Netherlands*

### R&D AND TECHNOLOGY TRANSFER

- **45 SOMLib New Approaches for Information Presentation and Handling** *by Andreas Rauber, Vienna University of Technology*

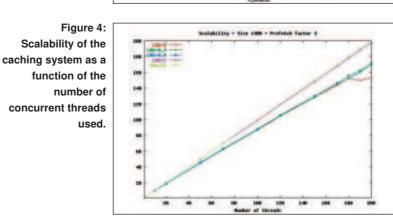

- **46 Hybrid Caching of Search Engine Results** *by Tiziano Fagni and Fabrizio Silvestri, ISTI-CNR*

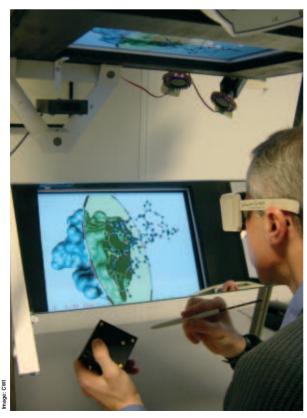

- **48 Personal Space Station handles Virtual 3D Objects** *by Jurriaan Mulder, CWI*

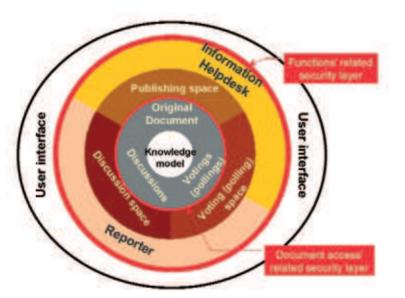

- **49 Augmented Virtual Table Tennis** with Real Racquets by Charles Woodward and Petri Honkamaa, VTT

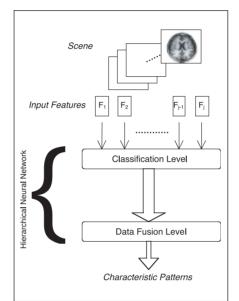

- 51 Scene Understanding using Hierarchical Neural Networks by Gabriele Pieri and Ovidio Salvetti, ISTI-CNR

- 52 A Digital Film-Saver for Archives by George L. Kovács and Iván Kas, SZTAKI

- 54 Knowledge Technologies in Support of e-Government and e-Democracy by Jan Paralic and Tomas Sabol, Technical University of Kosice (SRCIM)

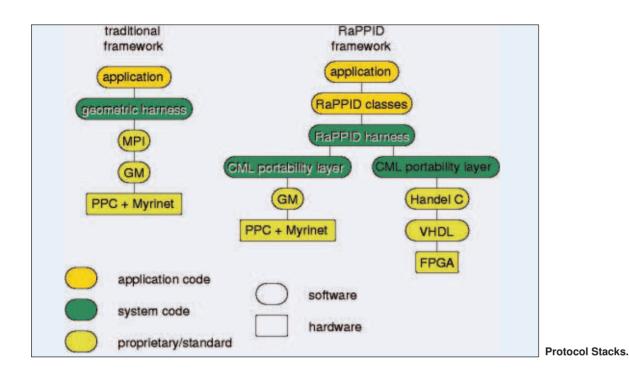

- 55 Rapid Prototyping for Embedded Parallelism

by David Johnston, Martin Fleury and Andy Downton, University of Essex, UK

57 Discretizing Continuous Attributes in AdaBoost for Text Categorization by Pio Nardiello, Fabrizio Sebastiani, and Alessandro Sperduti, ISTI-CNR

### EVENTS

58 The 7th ERCIM Workshop on 'User Interfaces for All' by Noëlle Carbonell, INRIA and Constantine Stephanidis, ICS-FORTH

### **59** Announcements

### 63 IN BRIEF

Tim Berners Lee, Director of W3C (left) and Gerard van Oortmerssen, President of ERCIM.

### **ERCIM New European Host of W3C**

The change of W3C European Host from INRIA to ERCIM took place on 1 January 2003. This organisational change aims to strengthen research relationships throughout Europe to better support Web technology development.

As the Web has grown into a more widespread and essential resource for industry, academia, governments, and their citizens, there is a pronounced need for an even more diverse infrastructure and support network. Establishing the W3C's European base at ERCIM will be beneficial to all involved. W3C's move to ERCIM opens new opportunities to integrate Web research and industry in Europe.

"The Web grows stronger and more useful when there are real commitments to engaging international presence and influence in Web technology development," explained Tim Berners-Lee, W3C Director. "For W3C, it means having one headquarters supported by three global partners — MIT, Keio University and now ERCIM. With the move to ERCIM, there is the potential for considerable growth and synergies of Web technologies across Europe."

"As a network of IT research centers, ERCIM encompasses over 10,000 researchers. W3C will benefit from this reservoir of expertise. For ERCIM, this change brings an opportunity to enhance cooperation on a global scale," noted Gerard van Oortmerssen, President of ERCIM.

Since its inception in the United States at MIT's Laboratory for Computer Science in October 1994, W3C has made sure that the World Wide Web lives up to its name and its promise. At the insistence of its Director, Tim Berners-Lee, the W3C has equal presence in North America, Europe and Asia. W3C identifies not-for profit institutions to serve as regional headquarters and provide physical locations for staffing. These institutions are identified as W3C 'hosts'. Moving the European host to ERCIM allows W3C to expand its base from one country to 16 for improved research and development opportunities throughout Europe, while maintaining its historically strong relationship to INRIA, one of the ERCIM founders.

"INRIA provided the necessary foundations for European involvement in Web infrastructure development, and now we have the opportunity to expand into a new phase," explained Bernard Larrouturou, President of INRIA and Manager of ERCIM. "Moving the host to ERCIM is consistent with INRIA's culture of incubating new initiatives and our commitment to strengthening the IT community in Europe." When INRIA became the first W3C European host in 1995, W3C had 50 Members in four countries. Today, the W3C Membership exceeds 450 organizations, with representation in nearly every country in Europe. INRIA's resources attracted both member organisations and technical staffing to W3C. INRIA also provided crucial links to European research communities. During this time, W3C received financial support from the European Commission to build a network of Offices throughout Europe. Currently, W3C has 13 Offices worldwide, with eight in Europe. Seven of the European Offices are already based at ERCIM Institutes, including CWI (Benelux), Fraunhofer IMK (Germany and Austria); FORTH (Greece), SZTAKI (Hungary), CNR (Italy), SICS (Sweden) and CCLRC (UK and Ireland). Offices work with W3C hosts promoting local languages, broadening W3C's geographical base, and encouraging international participation in W3C Activities.

### About the World Wide Web Consortium

The World Wide Web Consortium was created in October 1994 to lead the World Wide Web to its full potential by developing common protocols that promote its evolution and ensure its interoperability. W3C has nearly 450 member organizations from all over the world and has earned international recognition for its contributions to the growth of the Web.

By promoting interoperability and encouraging an open forum for discussion, W3C commits to leading the technical evolution of the Web. In just over seven years, W3C has developed more than 40 technical specifications for the Web's infrastructure. However, the Web is still young and there is still a lot of work to do, especially as computers, telecommunications, and multimedia technologies converge.

### W3C's Goals

W3C's long term goals for the Web are:

- Universal Access: To make the Web accessible to all by promoting technologies that take into account the vast differences in culture, languages, education, ability, material resources, and physical limitations of users on all continents

- *Semantic Web*: To develop a software environment that permits each user to make the best use of the resources available on the Web

- *Web of Trust*: To guide the Web's development with careful consideration for the novel legal, commercial, and social issues raised by this technology.

### W3C's Role

As with many other information technologies, in particular those that owe their success to the rise of the Internet, the Web must evolve at a pace unrivaled in other industries. Almost no time is required to turn a bright idea into a new product or service and make it available on the Web to the entire world; for many applications, development and distribution have become virtually indistinguishable. At the same time, easy customer

### W3C Activities

W3C Activities are organized into groups: Working Groups (for technical developments), Interest Groups (for more general work), and Coordination Groups (for communication among related groups). These groups produce the bulk of W3C's results: technical reports, open source software, and services (eg, validation services). There are currently over thirty W3C Working Groups. To facilitate management, the Team organizes W3C Activities and other work into four domains:

Style

Multimodal Interaction

· Voice Browser.

Activities include:

· Semantic Web

XML Encryption

• XML Signature.

XML Key Management

Web Accessibility Initiative

WAI Technical Activity.

**Further information:**

W3C's commitment includes

promoting a high degree of usability

for people with disabilities. The activ-

WAI International Program Office

In addition, the Quality Assurance

Activity and Patent Policy apply to all

http://www.w3.org/Consortium/Activities/

Privacy

ities are:

domains.

Synchronized Multimedia

**Technology and Society Domain**

The W3C Technology and Society

Domain seeks to develop Web

infrastructure to address social,

legal, and public policy concerns.

### **Architecture Domain**

The Architecture Domain develops the underlying technologies of the Web. Activities include:

- The Document Object Model

- Internationalization, to make sure that Web technology meets the needs of the global community

- Jigsaw, W3C's Web server platform

- Uniform Resource Identifier (URI), the Web's naming and addressing technology

- Web Services, programmatic interfaces for application to application communication

- Extensible Markup Language, XML.

### Interaction Domain

The Interaction Domain seeks to improve user interaction with the Web, and to facilitate single Web authoring to benefit users and content providers alike. Activities include:

- Amaya, W3C's own editor/browser

- Device Independence

- Graphics

- Hypertext Markup Language (HTML)

- Math (primary focus is the MathML language)

feedback has made it possible for designers to fine tune their products almost continually. With an audience of millions applying W3C specifications and providing feedback, W3C concentrates its efforts on three principle tasks:

- *Vision*: W3C promotes and develops its vision of the future of the World Wide Web. Contributions from several hundred dedicated researchers and engineers working for Member organizations, from the W3C Team (led by

- Tim Berners-Lee, the Web's inventor), and from the entire Web community enable W3C to identify the technical requirements that must be satisfied if the Web is to be a truly universal information space.

- *Design*: W3C designs Web technologies to realize this vision, taking into account existing technologies as well as those of the future.

- *Standardization*: W3C contributes to efforts to standardize Web technologies by producing specifications

(called 'Recommendations') that describe the building blocks of the Web. W3C makes these Recommendations (and other technical reports) freely available to all.

#### **Design Principles of the Web**

The Web is an application built on top of the Internet and, as such, has inherited its fundamental design principles:

- *Interoperability*: Specifications for the Web's languages and protocols must be compatible with one another and allow (any) hardware and software used to access the Web to work together.

- *Evolution*: The Web must be able to accommodate future technologies. Design principles such as simplicity, modularity, and extensibility will increase the chances that the Web will work with emerging technologies such as mobile Web devices and digital television, as well as others to come.

- *Decentralization*: Decentralization is without a doubt the newest principle and most difficult to apply. To allow the Web to 'scale' to worldwide proportions while resisting errors and breakdowns, the architecture(like the Internet) must limit or eliminate dependencies on central registries.

These principles guide the work carried out within W3C Activities.

### Activities

W3C organizes the work necessary for the development or evolution of a Web technology into activities. Each activity has its own structure, but an activity typically consists of one or more working group, interest group, and coordination group. Within the framework of an activity, these groups generally produce recommendations and other technical reports as well as sample code. Important to every W3C activity is quality assurance (QA) and patent policy. To manage related activities, the W3C team groups them into four domains: Architecture, Interaction, Technology and Society, and the Web Accessibility Initiative.

Guided by these design principles, W3C has published more than forty Recommendations since its inception. Each Recommendation not only builds

### Recommendations published by W3C in 2002

- User Agent Accessibility Guidelines 1.0

17 December 2002, Ian Jacobs, Jon Gunderson, Eric Hansen

- XML Encryption Syntax and Processing 10 December 2002, Donald Eastlake, Joseph Reagle

- Decryption Transform for XML Signature

10 December 2002, Merlin Hughes, Takeshi Imamura, Hiroshi Maruyama

- XML-Signature XPath Filter 2.0 8 November 2002, John Boyer, Merlin Hughes, Joseph Reagle

- Exclusive XML Canonicalization Version 1.0 18 July 2002, John Boyer, Donald E. Eastlake 3rd, Joseph Reagle

- The Platform for Privacy Preferences 1.0 (P3P1.0) Specification 16 April 2002, Massimo Marchiori

- XML-Signature Syntax and Processing 12 February 2002, Donald Eastlake, Joseph Reagle, David Solo

Further information: http://www.w3.org/TR/#Recommendations

on the previous, but is designed so that it may be integrated with future specifications as well. W3C is transforming the architecture of the initial Web (essentially HTML, URIs, and HTTP) into the architecture of tomorrow's Web, built atop the solid foundation provided by XML.

### **Challenges for Tomorrow**

In other specifications, W3C is addressing a number of challenges for the Web of tomorrow:

- Ensure access to the Web by many devices.

- Promote best practices.

- Coordinate with international regulatory bodies

- Account for cultural diversity

- Encourage research.

### W3C Organization

To meet its goals (universal access, semantic Web, Web of trust) while exercising its role (vision, design, standardization) and applying its design principles (interoperability, evolution, and decentralization), W3C process is organized according to three principles:

- *Vendor neutrality*: The W3C hosts are vendor and market neutral, as is the Team. W3C promotes neutrality by encouraging public comment on specifications during their entire life cycle.

- *Coordination*: The Web has become phenomenon so important (in scope and investment), that no single organi-

zation can or should have control over its future. W3C coordinates its efforts with other standards bodies and consortia such as the IETF (Internet Engineering Task Force), the Unicode Consortium, the Web3D Consortium, and several ISO committees.

• *Consensus*: Consensus is one of the most important principles by which W3C operates. When resolving issues and making decisions, W3C strives to achieve unanimity of opinion.

### W3C Team

The W3C Team includes more than seventy researchers and engineers from around the world who lead the technical activities at W3C and manage the operations of the consortium. Most of the team works physically at the three host institutions. ERCIM currently hosts 19 team members.

More information: http://www.w3.org/

### World Wide Web Consortium launched Hungarian Office at SZTAKI

### by László Kovács and Éva Megyaszai

## W3C strengthens presence in Central Europe through Hungarian outreach by W3C Hungarian Office, located at SZTAKI's Department of Distributed Systems. The Office was launched in Budapest, on September 24, 2002.

The opening ceremony was a public event, with presentations and tutorials from the W3C Team, including Daniel Dardailler (W3C Deputy Director for Europe), Marie-Claire Forgue (W3C European Communications Officer), Ivan Herman (Head of Offices at W3C), Vincent Quint (W3C Document Formats Domain leader) and Max Froumentin (Math Activity Lead and XSL Working Group Team Contact); and presentations of projects at SZTAKI (CORES, SOTF, PVX). Péter Bakonyi, Deputy State Secretary for Information Society Strategy, Hungary and Péter Inzelt, Director of SZTAKI were also among those attending the opening ceremonies at the Hungarian Academy of Sciences, in Budapest.

The Hungarian Office is the first office in Central Europe, joining an active roster which includes a number of European Offices of W3C as well as the

Opening ceremony.

W3C European host site at ERCIM. Its role is to act as a local point of contact, and to make sure that W3C and its specifications are known in the region. The mission of the Office is to promote adoption of W3C recommendations among developers, application builders, and standards setters, and to encourage inclusion of stakeholder organizations in the creation of future recommendations by joining W3C.

Hungarian economy shows the most dynamic and attractive growth in the region, especially with respect to information technology and telecommunication. SZTAKI has well-established cooperations with leading institutions and firms covering different areas of Information Technology, Computer Science and Control. The Institute maintains more than 100 contracts yearly with industrial, governmental, and other partners, including joint projects with European Union funding.

W3C looks forward to a long-term partnership with SZTAKI, leading to a stronger Hungarian voice within W3C and a greater awareness in Hungary of W3C's Activities.

### Links:

W3C Hungarian Office: http://www.w3c.hu/ W3C: http://www.w3.org/ SZTAKI, Department of Distributed Systems: http://dsd.sztaki.hu/

Please contact: László Kovács, SZTAKI Tel: +36 1 279 6212 E-mail: office@w3c.hu

Éva Megyaszai, SZTAKI Tel: +36 1 279 6204 E-mail: office@w3c.hu

### **ERCIM Fellowship Programme**

ERCIM offers 18-month fellowships in leading European information technology research centres. Fellowships are available in areas covered by the ERCIM Working Groups and other fields. This offer is available for PhD holders from all over the world.

### Deadline for application: 30 April 2003

### Conditions

- Applicants must:

- have a PhD degree (or equivalent) or be in the last year of the thesis work

- be fluent in English

- be discharged or get deferment

- from military service.

Fellowships are of 18 months duration, generally spent in two institutes. The fellow will receive a monthly allowance which may vary depending on the country. In order to encourage the mobility, a member institution will not be eligible to host a candidate of the same nationality.

### Topics

Topics include:

- Applications of Numerical Mathematics in Science

- Constraints Technology and Applications

- · Control and Systems Theory

- Digital Libraries

- · E-Learning

- · Environmental Modelling

- Formal Methods

- Health and Information Technology

- Image and Video Understanding

Matrix Computations and

- Matrix Computations and Statistics

- User Interfaces for All

Detailed information and the online application form is available at: http://www.ercim.org/fellowship/

### Human Resources Managers Task Force

by José Koster and Heather Weaver

The ERCIM Board of Directors has set up a Human Resource Management task force with the aim to share information and experience among ERCIM institutes and to co-ordinate ERCIM internal mobility of researchers and other issues related to human resources.

The ERCIM Board of Directors has emphasised the growing importance of human capital in ICT and Mathematics research. The ICT and Mathematics area as a whole is growing rapidly. The European heads of government have clearly expressed an ambition to make Europe the best performing continent in ICT, and therefore ICT is a main item on the agenda of the next Framework Programme. At the same time, ERCIM partners are experiencing a very tight labour market in ICT and Mathematics, and in view of low student numbers a significant shortage of talent is to be expected in the coming years.

Another development of interest is the increasing co-operation across Europe, thus encouraging opportunities for greater mobility of researchers in Europe. Most ERCIM institutes have seen significant increases in cooperation patterns, both nationally and internationally. Consequently, ERCIM is determined to increase its internal mobility programme. This development towards network organisations puts new demands on Human Resources management.

The ERCIM Human Resource Management task force (HR-TF) was established in September 2001 with the mission to attract and retain the best human capital at ERCIM institutes by:

- encouraging talent and enhancing skills in the area of ICT and Mathematics through promoting mobility opportunities among researchers and supporting staff

- encouraging and establishing best practice through sharing information and experience over a wide range of HRM issues.

In addition, the HR-TF has the mission to:

- develop an Internal Mobility programme

- improve fellowship programmes and recruitment outside Europe

- initiate a European portal for job opportunities.

The HR-TF will analyse the the different mobility programs within the ERCIM organisations. As a result, this should provide new ideas how to improve the mobility of researchers, administrative and supporting staff among the ERCIM member institutes.

As a next step, the HR-TF will produce a web-based template available to all ERCIM members outlining practical advice on such issues as salary, tax, national insurance, travel, accommodation, etc, to provide partners wishing to participate in the various types of mobility schemes with more information. Furthermore, the HR-TF is exploring the fundingpossibilities for mobility and management development. The upcoming VIth Framwork Programme and the EU Leonardo da Vinci scheme can be useful for this purpose.

The HR-TF invites all ERCIM member institutes to participate on a regular basis.

Please contact: José Koster, CWI HR-TF Secretary E-mail: Jose.Koster@cwi.nl

### **EURO-LEGAL**

News about legal information relating to Information Technology from European directives, and pan-European legal requirements and regulations.

#### Metatags that cause Trademark Infringement

The UK has seen a recent landmark case that contains the first judicial analysis of trademark infringement where the use of the mark was made via metatags. Website owners rely on metatags to ensure that search engines bring visitors to their sites. The search engines use spider software to create indexes of catalogued websites by reviewing the sites' metatags for keywords. In some cases these metatags could include a trademark and website owners can use this as a method of redirecting internet users to their site. In order to establish trademark infringement, it is necessary to show that the infringing name or mark has been used 'in the course of trade'. This landmark case rules that despite the fact that these metatags are invisible to the website visitor they are visible when translated into a search result on the user's browser. This case provides further protection to registered trademark owners from other websites using their brands to attract visitors to their site.

### Internet Sales —

New Rules for EU Consumers

The Brussels Regulation, which came into force on 1 March 2002, introduced new rules for determining where claims arising from civil and commercial disputes involving parties from different countries can be heard within the EU. The rules apply to claims made by consumers arising out of sales of goods or services over the Internet.

Court proceedings must be brought within the Member State where the consumer lives. This right of jurisdiction cannot be waived even if the terms of the contract imply something else. Until now the contract must have been concluded while the consumer was in his or her Member State. The new regulation, however, introduces an additional jurisdiction that deals specifically with cross-boarder sales to consumers over the internet, where the trader "directs such activities to that Member State or to several Member States including that Member State". In other words, if a consumer from the UK purchases goods on the internet whilst on holiday in another Member State (eg France) he or she can bring a claim against the trader in France providing the trader "directed his activities" to the home State of the consumer (in this case, the UK).

Although this has not yet been tested in the courts it is likely to impact more heavily on traders who offer their goods or services in a number of languages and accept payment in different currencies, including the Euro. If traders wish to avoid claims in the future, they may have to consider accepting orders only from consumers residing in their own Member State and in the currency of that Member State. This is likely to impact on the value of trading on the internet. It will be interesting to see how case law develops in this area.

**by Heather Weaver, CLRC** Tel: +44 1 235 446151 E-mail: H.Weaver@rl.ac.uk

# Andreas Rauber Winner of the 2002 Cor Baayen Award

The annual ERCIM Cor Baayen Award was presented to Andreas Rauber during a ceremony in Nice on 7 November 2002. The award is given every year to a most promising young researcher in computer science and applied mathematics having completed the PhD-thesis in one of the 'ERCIM countries'.

Andreas Rauber is a bright, young researcher at the Department of Software Technology, Vienna University of Technology. Andreas Rauber received his PhD in 2001 from Vienna University of Technology. He started his research career in the area of neural networks where he worked on improvements of the self-organizing map architecture. One of his assets, however, is his wide spread interest which made him progress into and integrate different fields of research. His current focus is on digital libraries where he investigates novel paths for semantically classifying information from heterogeneous sources, as for example text and music. His scientific curiosity paired with his sense for technical rigour is responsible for his high-quality research achievements.

Besides his core research and his more than 60 peer-reviewed publications, Andreas Rauber is also an active member of the international scientific community exemplified by his membership in various program commitees at international conferences and on the board of the IEEE Technical Commitee on Digital Libraries. See also his article on page 45: 'SOMLib – New Approaches for Information Presentation and Handling'. Andreas Rauber is currently an ERCIM Research Fellow at INRIA.

#### Link:

http://www.ercim.org/activity/cor-baayen.html

#### **Please contact:**

Lubos Brim, CRCIM Cor Baayen Award coordinator E-mail: lubos.brim@ercim.org

Andreas Rauber at the award ceremony.

### **COR BAAYEN AWARD 2003**

The Cor Baayen Award, created in 1995 to honour the first ERCIM President, is open to young researchers having completed their PhD thesis in one of the 'ERCIM countries', currently: Austria, Czech Republic, Finland, France, Germany, Greece, Hungary, Ireland, Italy, Luxembourg, Norway, Slovakia, Sweden, Switzerland, The Netherlands and the UK. The award consists of a cheque for 5000 Euro together with an award certificate. The selected young researcher will be invited to the ERCIM meetings in autumn. A short presentation of the winner together with the list of all candidates nominated for each country will be published in ERCIM News and on the ERCIM website.

### **Rules for Nomination:**

Nominations for each country are made by the corresponding ERCIM Executive Committee member (also referred to as 'national contact'). Those who wish that a particular candidate be nominated should therefore contact the ERCIM Executive Committee member for their country (see the ERCIM Executive Committee page at http://www.ercim.org/contacts/execom/execom.html).

Nominees must have carried out their work in one of the "ERCIM countries". On the date of the nomination, nominees must have been awarded their PhD (or equivalent), but this PhD shouldn't be older than 2 years. Each ERCIM institute is allowed to nominate up to two persons from its country. A person can only be nominated once for the Cor Baayen Award. The selection of the Cor Baayen award is the responsibility of the ERCIM Executive Committee.

### How to nominate:

For proposing a nomination to your national contact you should fill out the Cor Baayen Award Nomination Form. Please ensure that all the required information is provided. With your proposal please include a copy of the candidate's PhD thesis (preferably provided as a link to an electronic document) and copies of the candidate's best papers (max. 5 and preferably provided as links to electronic documents).

### Deadlines:

30 April 2003:

Submission of nominations to the national contacts.

15 May 2003:

National contacts to submit their two selected nominations to the coordinator

### Information:

Further information can be obtained from your national contact or from the Cor Baayen Award coordinator Lubos Brim, CRCIM (lubos.brim@ercim.org).

See also http://www.ercim.org/activity/cor-baayen.html

### **Articles in this Section**

#### 10 Embedded Systems - Introduction by Erwin Schoitsch

#### APPLICATIONS

- 12 An Approach to Dependable Architectures and Components for Railways by Andrea Bondavalli, Felicita Di Giandomenico and Luca Simoncini

- 13 Monitoring and Controlling Scientific Experiments: Anywhere - Anytime by Christian Wattinger, Peter Fornaro, Martin Guggisberg, Tibor Gyalog, and Helmar Burkhart

- 15 Emerging Frontiers in Miniature Computer and Embedded Systems by Angelos Bilas and Evangelos Markatos

- 16 Wearable Systems for Everyday Use by Spyros Lalis, Anthony Savidis and Constantine Stephanidis

- 18 New Solutions for In-Vehicle Embedded System Development by Françoise Simonot-Lion and Yvon Trinquet

- 20 Remote Control and Monitoring over the Internet - Wireless Construction Site by Leila Rannanjärvi

#### **NETWORKS AND EU PROJECTS**

- 21 Creating a Network for Those working with Embedded and Real-Time Systems by Barrie Ross-Dow

- 22 DECOS Dependable Embedded Components and Systems

#### by Dieter Donh offer and Erwin Schoitsch SYSTEM ARCHITECTURES, METHODS, LANGUAGES AND TOOLS

- 24 Time Triggered Architecture by Hermann Kopetz

- 26 Automatic Distribution of Synchronous Programs by Alain Girault

- 28 synERJY: a High-Level Language for Embedded Controllers by Reinhard Budde, Axel Poigné

and Karl-Heinz Sylla

- 29 STOREQ: Storage Requirement Estimation and Optimisation Tool for Data-Intensive Embedded Applications by Per Gunnar Kjeldsberg

- 31 Composing Embedded Real-Time Software Components: the PECOS Data-Centric Approach by Stéphane Ducasse, Oscar Nierstrasz and Roel Wuyts

- 32 Time Machines and Black Box Recorders for Embedded Systems Software by Henrik Thane

- 33 Design of Embedded Systems: New Challenges by Gilbert Cabillic and Isabelle Puaut

- 35 Transforming Specifications to verify Embedded Systems by María del Mar Gallardo, Jesús Martínez, Pedro Merino and Ernesto Pimentel

- 36 EUDEMES: Component-Based Development Methods for Small-Size Embedded Systems by Nicolas Guelfi, Aloyse Schoos, Gérard Sébastien and François Terrier

- 37 Model Checking of Embedded Systems by Stefania Gnesi, ISTI-CNR

- 39 Systems Validation Centre shows Benefits of Formal Methods by Henk Eertink, Wan Fokkink, Holger Hermanns and Izak van Langevelde

#### EDUCATION

- REDEST Sharing Experiences in the Field of Embedded Software Requirement Gathering by János Nacsa, SZTAKI

- 42 EmbLab A Laboratory for Teaching Embedded Systems by Amund Skavhaug, Trygve Lunheim and H. Skinnemoen. NTNU

- 43 Master Course Embedded Systems at Eindhoven University of Technology by Jan Friso Groote, Eindhoven University of Technology, The Netherlands

### **Embedded Systems - Introduction**

### by Erwin Schoitsch

Each day, our lives become more dependent on 'embedded systems', digital information technology that is embedded in our environment. This includes not only safety-critical applications such as automotive devices and controls, railways, aircraft, aerospace and medical devices, but also communications, 'mobile worlds' and 'e-worlds', the 'smart' home, clothes, factories etc. All of these have wide-ranging impacts on society, including security, privacy and modes of working and living. More than 98% of processors applied today are in embedded systems, and are no longer visible to the customer as 'computers' in the ordinary sense. New processors and methods of processing, sensors, actuators, communications and infrastructures are 'enablers' for this very pervasive computing. They are in a sense ubiquitous, that is, almost invisible to the user and almost omnipresent. As such, they form the basis for a significant economic push.

These applications are 'vision driven', as in the following examples:

- Automotive: Accident free driving

- Aerospace: A free, safe sky for all

- Medical Devices: Robotic surgeon

- Communications: Seamless connectivity

- *e-Life*: ubiquitous/pervasive computing

### The European Context

The European Commission has recognised the importance of embedded systems by creating a new unit in the IST Directorate. The visions surrounding the AMI-space (embedded systems everywhere, described in the context of human life as 'ambient intelligence') have considerably influenced the 6th Framework Programme of the IST domain. In this issue we focus on hard real-time, dependability/safety and AMI-scenario applications. There also exists a separate strategic objective on embedded systems in the work program 2003-2004, namely, to develop the next generation of technologies and tools for modelling, design, implementation and operation of hardware/software systems embedded in intelligent devices. An endto-end systems vision should allow costefficient systems to be built with optimal performance, high confidence, reduced time to market and faster deployment. The focus is on the following:

- Middleware and platforms for building networked embedded systems that aim to hide the complexity of underlying computing, communications, sensing and control, while at the same time providing efficient and effective distribution of resources at low cost. The emphasis will be placed on middleware for small wireless devices, eg mobile phones or PDAs, which make the design, programming, verification and maintenance of systems including such devices easier. Effort will also be devoted to scalable and self-organising platforms that offer services for ad-hoc networking of very small devices and for mastering complexity through perception techniques for object and event recognition and advanced computing and control.

- Concepts, methods and tools for system design and development of warrantable software components and implementation of systems, with an emphasis on the correct handling of complex real-time constraints. Work includes unification of computational models and composition methods, holistic design addressing event and time constraints, interface technologies in hard- and software addressing real-world and legacy issues, and techniques and integrated validation tools to ensure ultra-stable, dependable embedded systems.

- Advanced controls for real-time systems with an emphasis on hybrid systems theories including non-linear processes with both constraints and switching modes. Advanced controls for networked embedded systems, focussing on networked autonomous and fault-adaptive control and management, as well as on reasoning, behaviour, global performance and robustness.

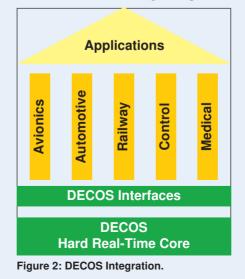

This strategic objective is covered in the second call (15 June to 15 October 2003). The recently founded ERCIM Working Group 'Dependable Software-Intensive, Embedded Systems' is involved in a large IP proposal (Integrated Project, one of the new instruments of European funded research) called DECOS, Dependable Embedded Components and Systems (see article on page 22).

### **New Research Challenges**

A new set of research challenges is presented due to the enormous dimensions of deployment and connectivity, which imply new levels of complexity and risk and new failure modes:

- context-awareness (identify, localise and interact with persons and objects, in a non-location-dependent manner)

- intelligence (the digital environment adapts to mobile objects and persons, and learns and interacts independently, thus providing fascinating new services)

- natural interaction (human language, gestures, speech synthesis)

- personalisation (user-centred, dynamic adaptation to changing situations and user profiles/preferences)

- dependability (time dynamics, timely responsiveness, security, safety, availability, maintainability, robustness etc)

- restricted resources (low power management, size, weight, memory, processing power/speed, interfaces etc)

- wireless/mobile, seamless communication

- hard real-time applications (automotive, aerospace, railways, process control, medical devices, communications etc)

- challenges of composability, COTS, (ultra-)high confidence in design and certification, security and predictability.

Important sub-areas are (rigorous) hardware/software co-design, smart new sensors/actuators, continuous connectivity issues and limited resource management. Horizontal issues include dependability, system integration, software technologies, standardisation, certification, and critical infrastructures.

### **ERCIM Working Group**

### Dependable Software-Intensive Embedded Systems

The dependability aspect of embedded systems is of the utmost importance, and ERCIM members have identified a huge potential with respect to this. Accordingly, the new ERCIM member AARIT, within which ARCS is an important driving force, has proposed and initiated an ERCIM Working Group on 'Dependable Software-Intensive Embedded Systems'. The inaugural meeting took place in Vienna during the ERCIM board meetings, and a joint workshop with the EU projects on embedded systems (real-time) such as AMSD and ARTIST was organised in Grenoble on 3 October 2002. A second meeting was held in Sophia Antipolis on 6 November. Future plans include a workshop on 'Synchronous Languages, Time- and Event-Triggered Systems' around March/April this year, and a meeting in Trondheim on 2 June 2003.

The Working Group currently includes members from Austria (ARCS/AARIT), France (INRIA), Germany (FhG), Greece (FORTH), Italy (CNR, PDCC), Luxembourg (IST), Netherlands (CWI), Norway (NTNU) and Sweden (MRTC/SICS). Others are very welcome.

At the moment, all themes relating to embedded systems are of interest to the Working Group (WG), which focuses on specific topics case by case. The work program includes:

- experience exchange

- · joint position papers on relevant issues

- information exchange with organisations, other WGs and committees in which ERCIM members are already active

- · decision building processes

- · WG meetings adjacent to other relevant meetings/conferences

- · discussion board (via ERCIM Website or a member's Website)

- · contributions to ERCIM News

- one major event per year (may be combined with some important meeting or conference)

- cooperation within the EU Framework Programs (NoE, IP); currently Dependability (1st Call) and Embedded Systems (2nd Call)

- · cooperation in standardisation and awareness-building processes.

### About this issue

This issue of ERCIM News covers all aspects of embedded systems, technical as well as broadly socio-economical, and gives an overview of the scientific and engineering challenges, and fascinating possibilities and risks offered by this enabling technology.

The contributions are grouped into:

- Applications (6): Railways, Remote Control of Scientific Experiments, a more general article on 'Emerging Frontiers in Embedded Systems', Wearable Systems for Everyday Use, Embedded Systems in Cars, and Application in Transport Logistics

- Networking and EU-Projects (2)

- System Architectures, Methods, Languages and Tools (11)

- Education (3).

These contributions clearly demonstrate that the scientific community is attracted primarily by the interesting system, design and implementation challenges of embedded systems. It is also becoming evident that our educational systems require new curricula, labs and courses, as well as networks for experiential exchange, in order to keep up with such innovation. The section on applications shows that the driving force behind this comes from critical control applications (automotives, railways etc) and the 'everyday ubiquitous computing (AMI)' community.

**Please contact:**

Erwin Schoitsch ARC Seibersdorf research (AARIT) Tel: +43 50550 3117 E-mail: erwin.schoitsch@arcs.ac.at

### An Approach to Dependable Architectures and Components for Railways

by Andrea Bondavalli, Felicita Di Giandomenico and Luca Simoncini

Scientists at ISTI-CNR study methodologies and techniques to improve the definition and development of systems for railway applications. The envisaged solutions must guarantee the dependability and real-time requirements imposed by the application field while at the same time addressing the needs both of the market and of the technology.

Automatic systems for railway applications have traditionally been developed starting from proprietary architectures, in which the processors and memories were assembled using ad hoc components whereas the electronic components have generally been developed independently. A feature of this approach is that the components are designed in function of the overall system structure; this type of approach has positive and negative aspects.

Advantages are that:

- the design and implementation of ad hoc components facilitates validation of the system

- the entire system is controlled by the designer and there are no single parts protected by third party intellectual property rights; again this facilitates validation and procuring, mandatory actions for safety critical systems

- system redesign and updating is not dependent on third parties.

On the other hand:

- components and implementation technologies change and evolve very quickly; this means that some may be obsolete by the time that the design stage is completed and the system is ready for operation

- the operational life of the system tends to be extended which means that component upgrading may be required

- the strict dependence between system and components (through the design) means that it may be difficult to adapt the system to different contexts or to interface it with other systems, ie, reconfiguration may be very difficult if not impossible

- systems with even slightly different requirements and specifications cannot reuse existing components; this means that new systems generally require a complete redesign, and experience gained when operating previous systems cannot be exploited

- any new system or major revision needs to be revalidated ex-novo.

Another major issue is the need to reduce both commissioning time and development and operational costs. This makes the use of COTS (components off-theshelf) an increasingly popular choice.

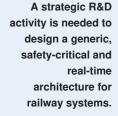

It is clear from the above scenario that a strategic R&D activity aimed at the definition, prototyping, partial verification and validation of a generic, safety-critical and real-time architecture for railway systems is needed.

Such an activity should be able:

- to reduce design and development costs

- to reduce the number of components used by the subsystems

- to simplify the product evolution process and reduce associated costs

- to simplify product validation (and certification) through an incremental approach based on reuse

- to make the design of safety-critical parts more flexible.

The resulting architecture should have the following characteristics:

- use generic components (possibly COTS) which can be replaced when necessary without the need for system redesign or revalidation

- reliability/availability and safety properties must be associated with the overall architecture rather than only with intrinsic properties of its components, so that techniques for error detection, diagnosis and error recovery are as far as possible independent from specific hardware or software components

- openness of the system, so that it can interface and communicate with other systems through different communication systems (eg GSM-R, radio, ISDN, etc.)

- adoption of a hierarchical approach for functional and non functional properties, to facilitate validation

- strict conformance with railway standards; in particular with CENELEC EN 50126, 50128, 50128, 50129, 50159-1, 50159-2.

For this reason, we are currently investigating architectures/component solutions able to satisfy the dependability and real-time requirements imposed by the high criticality of the application field while also addressing the market and technology demands.

In recent years, the Esprit Project GUARDS 'Generic Upgradable Architecture for Real-time Dependable Systems', which studied the development of methods, techniques, and tools to support the design, implementation and validation of safety-critical real-time systems, has already investigated a number of these issues. This project involved major industries from the space, nuclear and railways sectors. A careful specification of the needs of industrial end-users was used by the academic partners to identify and define suitable safety-critical mechanisms and architectures; these were then implemented with the support of the expertise and tools of the technology providers.

Within the GUARDS project, a series of R&D activities were performed, spanning from the definition of components/mechanisms for fault tolerance to the set-up of a multi-techniques validation framework and the development of architectural instances appropriate for different application fields. However, more extensive research is needed today, to properly account for current technological competitiveness and other

emerging challenges, such as integration and interoperability. The world market of railway systems has a strong growth trend, both at national and international levels, because of the need to optimise urban and suburban transport, to modernize the existing railway systems, to develop high-speed trains and to render European transport networks interoperable. In the next ten years, the European railway market plans to construct high speed lines for 12,500 km. In addition, 16,500 km of existing lines will have to be upgraded. The expected investment is in the range of 24 billion Euro

### **Please contact:**

Andrea Bondavalli, ISTI-CNR Tel: +39 050 315 3068 E-mail: a.bondavalli@cnuce.cnr.it

# Monitoring and Controlling Scientific Experiments: Anywhere - Anytime

by Christian Wattinger, Peter Fornaro, Martin Guggisberg, Tibor Gyalog, and Helmar Burkhart

Monitoring and controlling a scientific experiment from your mobile device anywhere and anytime — this is the goal of the MURCI (Mobile Universal Remote Control Interface) project at the Department of Computer Science of the University of Basel.

Mobile devices, such as mobile phones and PDAs, include always-on wireless networking, persistent memory, computational capabilities and enhanced user interfaces, and allow the uploading of small programs that exploit these abilities. This opens the concept of remote, real-time control of experiments.

As mobile devices gain more and better technical features, their role as locationindependent networking tools becomes more significant. Only a few months ago the sole use of a mobile phone was voice communication, with cumbersome procedures and slow and expensive connections making data transmission unfeasible. This situation has changed significantly with the introduction of GPRS (General Packet Radio System) networks. In the meantime, PDAs have also matured, now offering Bluetooth connectivity and the ability to be readily programmed, eg using Java. Despite these positive advancements, today's mobile devices still suffer from slow connection speed, small screen sizes and limited memory and overall performance. Both these new capabilities and restrictions make it advisable to use a 'thin client'-based model for developing mobile applications. A 'thin client' is a lightweight program running on a mobile device, which makes use of networking capabilities as well as the display and user interface. All resourceintensive program parts are run on a server computer which is accessed by the mobile device.

A project of the newly founded Mobile Technologies Group at the Department of Computer Science of the University of Basel is deploying this paradigm in the realisation of a system framework for remote experimentation. The notion of an experiment in this context has a broader meaning, which can include physical experiments, simulations, and long-term calculations in high-performance computer systems.

Our first demonstrator site, 'wireless Nano-World', implements the monitoring and control of an Atomic Force Microscope (AFM) simulator. An AFM is an instrument used in the nanosciences to explore surfaces at the nanometre scale, such that single atoms and molecules become observable and can

Figure 1: Scanned image of an atomic surface (with a change of scan range) and the parameter screen of the thin client.

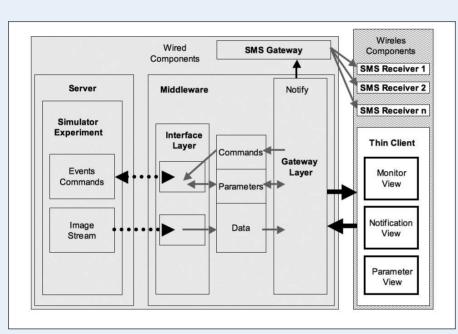

Figure 2: Architecture of the thin client model.

Figure 3:

The remote controllable Atomic Force Microscope (a) with rotating sample table (b) and the positioning axes.

even be manipulated. The simulator has been developed as part of the Virtual Campus Switzerland project 'Nano-World' and is used in teaching, learning, and training exercises. This is necessary because real AFMs are complex and expensive instruments, and very few of them are readily accessible to students. The use of simulators for training is popular with students, and being handson, is an effective and motivational learning tool.

The use of the mobile thin-client model to monitor and control a real experiment or simulation offers many advantages to the experimentalist. One advantage of having a tool to remotely observe and steer an ongoing experiment in a laboratory is the ability to control long-time measurement from the office, home or even while travelling, eg on a train. Another big advantage is the ability to easily notify collaborators or an administrator. This notification mechanism can be triggered actively or automatically by the remote-controlled system itself, eg in the case of a malfunction or after a selftest. This message can alert a human supervisor or trigger another process on a receiving machine.

Technically, the model used is a layered architecture. The experiment or simulation defines the input/output ports to which a middleware layer is linked. The middleware processes the data and translates it so as to be usable by the respective end-points. The mobile thin client presents the arriving data and accepts control commands for the experiment.

The thin client itself has three basic components:

- 1. The monitoring module presents the incoming visualized measurement data. On this screen the user can monitor the ongoing experiment at a glance. Later options for visualization and image capture will also be included (Figure 1 on left).

- 2. The command module lets the user monitor the current experimental parameters and also allows their values to be changed. Additionally it is possible to send 'start', 'stop' and 'pause' commands to the experiment (Figure 1 on right).

3. The third component is the communication module. At present, this is included in the command module, but in future will be decoupled and built as a separate component as befits its importance. It allows the user to inform other mobile users about the experiment. Standard messages for cases of alert, special interest, or help requests are available to be sent to a specified list of receivers. Messages are currently sent as SMSs (Short Message Service) because of this medium's reliability. In the future other protocols like instant messaging (IM, eg Jabber) or Multimedia Message Service (MMS) may be better solutions. Voice and video channels would also be useful, as soon as the transmission speed and cost issues are resolved.

The thin client connects to the real-world experiment or simulation via a middleware layer, which mediates between the experiment and thin client as seen in Figure 2. The middleware in the second layer must present measurement data to the wireless client in a bandwidth- and transmission-cost-saving and standardised manner, while accepting continuous data streams from an experiment. Commands from the client on the other hand must be converted by the middleware to make them understandable by the experiment/simulator. This middleware layer is advantageously implemented as a Java servlet to easily introduce scalability for many simultaneous clients, as well as optional authentication elements. At the moment the middleware is still Common-Gateway-Interface-(CGI)-based and leaves much to be desired in terms of performance and reliability.

As feedback from the research community has been very positive, we want to rewrite and extend the prototype towards an operational mobile client to be used by researchers of the nanoscience competence centre. Thus the next goal is a real remote-controlled Atomic Force Microscope with a controllable sample table (Figure 3). This microscope allows standard sample positions to be defined, which can then be remotely reselected with micrometre precision. In this way, the instrument can be shared according to a schedule or notification by a number of researchers, each of whom can independently access his or her samples.

With regular self-tests and corresponding alerts to inform users in case of problems, it will be possible to run such research instruments in an administrated mode, where human interaction is only necessary for the setup of the probe and sample and in case of a failure notification. Valuable measurement time is therefore efficiently shared between research groups.

Link:

http://www.ifi.unibas.ch/research

Please contact: Christian Wattinger University of Basel, Swizterland E-mail: christian.wattinger@unibas.ch

### Emerging Frontiers in Miniature Computer and Embedded Systems

### by Angelos Bilas and Evangelos Markatos

Although over the last several years computer systems research has focussed on building general-purpose PCs, current emerging technologies and societal needs are shifting the focus towards ambient intelligent systems that monitor, adapt, and react to humans and objects.

Over the last twenty years, computer systems and architecture research has addressed the performance of generalpurpose microprocessors and desktop computers, with impressive results. Processor performance has been doubling every eighteen months, and today's general-purpose desktop systems are used in most applications to address single-user needs or as components of much larger computing and storage platforms. However, there is now an evident need to turn the focus of systems research from the above targets to new directions, moving from generalpurpose to application-specific systems and from performance to reliability, availability, security, autonomy, scalability, and manageability.

Current research at ICS-FORTH, which is partly funded by the 'Excellence' project initiative of the General Secretariat for Research and Technology of the Greek Ministry of Development, builds on existing expertise and addresses fundamental problems. These include:

- miniaturisation of computer and embedded systems

- interconnection of such systems

- autonomy and coordination of very large numbers of such systems.

It is expected that such autonomous, networked, miniature computer and embedded systems will find application in many new areas, eg diagnosis of epidemic diseases, forest and crop protection, human safety and monitoring of fine-grain parameters in the human environment. Overall, miniature computer and embedded systems are predicted to be the most effective carrier of ambient intelligence. Such systems can both perform intelligent functions and be placed or integrated in locations where traditional systems cannot fit, due to form factor, autonomy, and cost restrictions. Moreover, they will have the ability to communicate with each other, providing a means of transferring,

monitoring and controlling information everywhere in a ubiquitous and transparent manner. These directions in computer systems research at ICS-FORTH are discussed in more detail below.

#### Going small and going in numbers

In this regard, our research is searching for ways to build very small (say, coinsize) and flexible smart devices and embedded systems. Looking at today's state-of-the-art computing systems, two of the main factors restricting miniaturisation are the requirements on versatile I/O interfaces and rich runtime systems. The first is a result of various standard interfaces that need to be supported, whereas the second is a consequence of requirements for general-purpose functionality. Our goal is to re-think both of these issues. Firstly, we are interested in designing interfaces that can be used to connect components within very small systems. Of principal interest here is connectivity to non-logic-based devices (MEMS). Second, we would like to explore architectural support for novel runtime systems. Today's runtime systems provide flexibility that is not needed in application-specific devices, leading to high requirements in compute cycles. Our goal is to investigate how such devices should be designed to best support novel runtime systems that exhibit the necessary characteristics.

### Connectivity is the only way in and the only way out

This focus area examines how such systems should be interconnected among themselves and also to the outside world. Building interconnects for large numbers of miniature devices introduces constraints that are not present when building traditional interconnects. The physical medium used is constrained not only by size and speed but also by power consumption, and may well limit the distance at which such devices can transmit and receive data. Moreover, given the requirements of future miniature embedded systems, how their protocol stack should look is unclear. Traditional protocol stacks are inadequate due to the size, complexity, and the requirements they need to fulfil. In addition, security may be jeopardised since, on the one hand, the network is the only means of gaining access to such systems, while on the other hand, a full access and management API exposed over the network makes these systems vulnerable to attacks.

### All for one and one for all

Miniature systems are unique compared to existing computers because they are able to contribute to new application domains simply by being replicated in large numbers and by collaborating on solving a specific problem. However, this aspect of collaboration, which assumes a high level of autonomy, is new territory that needs to be explored. Previous work in distributed systems has addressed issues in systems that are more closely supervised, more independent in performing various tasks, and rather loosely coupled. The runtime system is a key component that implements most of the functionality relating to achieving collaboration and providing autonomy, but also that relating to tolerating and recovering from faults, providing reconfigurability, security, power management etc. Given that these systems will be less capable than modern computers, to a large extent the runtime system needs to be redesigned.

In summary, computer systems research is shifting its focus to new and exciting directions. We believe that among the most promising new aspects of computer systems research is the miniaturisation of networked computer and embedded systems and the implications of using large numbers of such devices. Large areas of uncharted territory remain in these fields for computer architecture and systems research.

http://archvlsi.ics.forth.gr

Please contact: Angelos Bilas and Evangelos Markatos, ICS-FORTH E-mail: {bilas, markatos}@ics.forth.gr

### Wearable Systems for Everyday Use

by Spyros Lalis, Anthony Savidis and Constantine Stephanidis

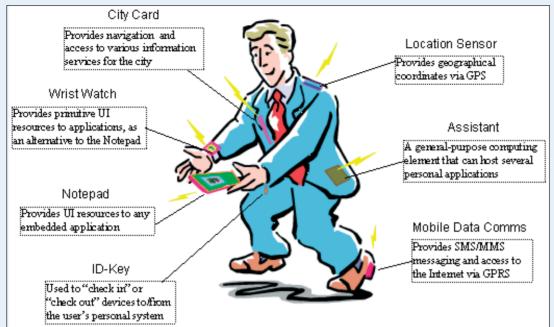

You have just landed in Heraklion. As you leave the airport you are handed a CityPass, a small gadget hosting a map application for the city, which you touch with your ID-Key and put away in your pocket. A few seconds later your wristwatch beeps with a message: "Welcome to Heraklion - the MapGuide can be controlled using your PDA or your wristwatch".

As you stroll downtown, you shoot several pictures, which are tagged with time and location information retrieved from the GPS on your wristwatch. Storage in the camera begins to run out, and the camera informs you that photos are now being stored in the Assistant in your backpack. At the same time, the Assistant silently uploads the photos to your home repository whenever you pass near a public network access point. You meet a friend at a café and together you browse through the photo collection. You decide to have dinner at an old tavern displayed in one of the pictures. You pull the Notepad out of the backpack and use the CityMap application to display the location of the tavern, using location information from the photo coordinates and your current position provided by the GPS on your wristwatch.

This brief scenario gives a flavour of the 2WEAR project and the vision shared by FORTH, ETHZ (Switzerland), MA Systems & Control (UK), and

Link:

Wearable systems.

NOKIA/NRC (Finland) of the future personal computer put together as an agglomerate of small, wearable and physically distributed devices. 2WEAR is a three-year EC-funded project that started on January 1, 2001 with the objective to build such a system, both in terms of software architecture and devices that communicate using shortrange radio technology. The main characteristic of the envisioned system is its dynamic extensibility and adaptation, which would allow users to combine devices in a flexible manner according to their current needs, and to exploit the potential of surrounding infrastructure within buildings, vehicles, etc. The 2WEAR system is exploring the following directions in parallel.

### **Core Runtime Mechanisms**

In this new paradigm, the personal computer, rather than being fixed in a box with a well-known amount of hardware resources and a given number of peripherals attached to it, is actually a system that is dynamically composed by bringing together different devices. To convert this physical versatility into tangible flexibility for the application and user, several problems must be addressed at the system level. Besides being a provider and manager of local resources, the runtime now becomes responsible for detecting and exploiting resources that become available via other devices that are added to the system. It must also take corrective actions should such resources become unavailable, due to failures or the user removing devices from the system.

The main system aspects that are being researched to achieve the desired functionality are ad-hoc discovery, flexible remote communication in the form of dialogue channels, and adaptive system services. Adaptive system services correspond to high-level resource abstractions provided to the application programmer, while dealing with lowlevel runtime issues such as resource discovery, remote resource access, resource switching and compensation in the case of resource loss.

#### **Human-Computer Interaction**

In dynamic, transient environments, the main architectural objective is to maintain high-quality interaction between users and applications. This principle of continuity emphasises the uninterrupted sequence of dialogue activities and ensures that the human-computer interaction dialogues transform gracefully from the user's perspective. To that end, the User Interaction Framework specifies: (a) how applications communicate with the user, and (b) the mechanisms allowing for the abstraction of Input Output (I/O) devices as well as for concurrently running applications to share I/O hardware resources. In practice, this means that framework services specific to the human-computer interaction dynamically allocate 'pooled'

system resources to user activities according to user preferences.

These mechanisms operate at a level between applications and the runtime, defining an infrastructure of services that take over all decisions relating to the administration of I/O resources and their allocation to active applications. As a result, application developers are able to produce user interfaces that remotely utilise multiple I/O resources (eg audio devices, different types of displays, input devices) over a wireless communication medium. In cases where loss of connection with some I/O resources or discovery of new I/O resources may occur as a result of mobility, running interfaces dynamically employ such new I/O resources and/or possibly reallocate existing ones to ensure interaction continuity. In addition, applications continuously inform the user of changes in the interactive space, such as the detection of newly available computing units and/or the loss of connection with devices. In this way, the user can engage or disengage computing units on a taskoriented basis.

### Links:

Project Web Site: http://2wear.ics.forth.gr

Please contact: Spyros Lalis, ICS-FORTH Tel: +30 2810 391746 E-mail: lalis@ics.forth.gr

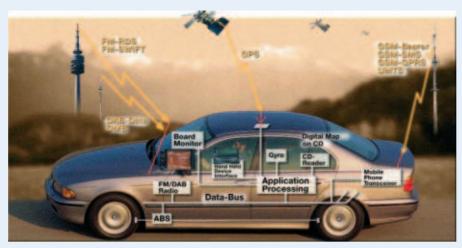

### New Solutions for In-Vehicle Embedded System Development

### by Françoise Simonot-Lion and Yvon Trinquet

While automobile production is probably to increase slowly in the coming years, the part of embedded electronics and more precisely embedded software is growing. New solutions for the development of in-vehicle embedded systems was the purpose of the French 'Embedded Electronic Architecture' cooperative research and development program 'AEE'. The results are the identification of embedded component classes, the specification of a generic embedded architecture, as well as the definition of a declarative language.

Today, functions embedded in vehicles include braking assistance, active suspension, steering functionalities, etc. They are subject to stringent timing constraints and more generally to dependability constraints. In the close future, these constraints will be more critical with the generalisation of X-by-Wire technology. Therefore the development of such systems must define an eligible system, ie, satisfying these constraints, and must provide the best one according to cost criteria. Furthermore, the development process of an embedded system is shared between several actors: carmakers and suppliers; the development of reusable components is a main way for the reduction of costs.

In this context, the French 'AEE Project (EEA in English: 'Embedded Electronic Architecture') specified new solutions for the development of in-vehicle embedded system. This program (September 1999 - December 2001) was granted by the French Under-Ministry for Industry and involved the French carmakers (PSA and Renault), OEM suppliers (SAGEM, SIEMENS, VALEO), the company EADS LV and the research centres INRIA, IRCCyN and LORIA. The European ITEA project (EAST-EEA) – currently in progress extends and generalises these results.

### **Electronic Embedded Architecture** and its Components

Most of the hard and software embedded in a car are specified and developed separately. Each one is dedicated to a particular feature and designed by a supplier with respect to carmaker requirements. On the one hand, this is a bar to the reusability of solutions in other projects and on the other hand, this leads to oversize the resources (hardware, buffers, etc). To solve this problem, the AEE project characterised formally the basic embedded components and defined the perimeter of the reusable ones. Furthermore it provided a generic archi-

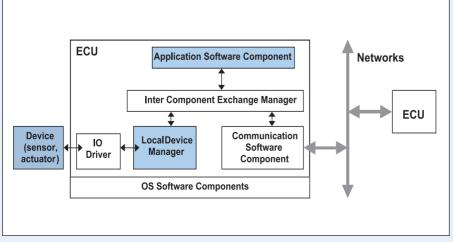

Figure 1: component classes and generic architecture.

tecture for an Electronic Control Unit (ECU), a station connected to one or several network(s) and supporting the embedded application (see Figure 1).

Some components are independent of a particular ECU; this means that they can be implemented on any ECU in a distributed architecture:

- sensors and actuators (hardware components) and software components (Local Device Manager) realising the signal processing for these devices

- software components implementing the specific embedded application (Application Software Components).

On the contrary, the Input/Output drivers, the Software Components implementing the Operating System (OS) or the Communication Services are dependent of a specific ECU.

Finally, in order to ensure an entire independence of Application Software Components, a specific component, named Inter Component Exchange Manager was specified. It plays the role of a middleware, in particular by providing transparent communication services. This component is developed specifically for each ECU with a common Application Interface.

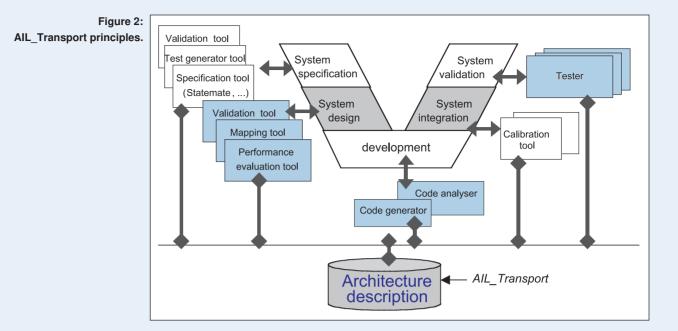

### AIL\_Transport: a Language for the Design of Embedded System

The project defined a specific development method for embedded systems to reduce costs and optimise the use of hardware elements. At the first step, functionalities are defined and validated independently of their implementation (Functional Architecture and Software

### SPECIAL THEME: EMBEDDED SYSTEMS

Architecture). Then an allocation mechanism maps the specified functions onto the ECUs of the embedded architecture and subsequently, some exchange flows communication networks onto (Hardware Architecture). Finally, local task execution and frame transmissions optimised (Operational are Architecture). With this approach, capitalisation no longer focuses on ECUs, but on the implemented functions through validated hardware and software modules.

Strong co-operation between OEM suppliers and carmakers in the design process implies the development of a specific concurrent engineering approach. In order to specify this process, synchronisation points (rendezvous) across the co-operative development model have to be identified and information exchanged at these points must be characterised. Furthermore, a unique syntax of the exchanged information has to be defined. For this, the AEE project has specified a business model specifically adapted to the architecture development conjointly by carmaker(s) and OEM supplier(s).

Performance of a vehicle embedded system may be evaluated from different points of view, according to the system analysis (wholly or partly) necessary at each development step. Usually carmakers attempt to optimise the number of ECUs, which are used to implement the vehicle functionalities. Furthermore, system designers attempt to optimise performances of communication networks. Finally, OEM suppliers have to demonstrate that their COTS are compliant with the carmaker requirements, etc. The AEE approach improves these different analyses and optimisations by enabling the use of various industrial and academic software tools. These tools are dedicated to analyse, test, simulate, validate, comment, and generate code of the electronic architecture. For that, each tool extract a specific and coherent model from the architecture description by means of a repository integrating all the pertinent data of the architecture modelling. This repository is the skeleton of the AEE development process, as shown in Figure 2. In order to build this repository, a language for the specification of any electronic architecture has been defined. It is called Architecture Implementation Language (AIL\_Transport). The AIL\_Transport language integrates the AEE design process, and thus is used by all designers as the backbone of the architecture development. Moreover, AIL\_Transport is the source language to define the reusable architecture objects.

Associated to AIL\_Transport, a development process has been specified for defining and harmonizing the exchanges of partial architectures between carmakers and OEM suppliers. The main benefit of this study is to allow the design of flexible architectures while reducing costs and increasing the quality of the development. At present, the results obtained in AEE project are one of the entry points for an ITEA European project (EAST – EEA), gathering the main actors of European automotive industry.

### Link:

AEE: http://aee.inria.fr.

#### **Please contact:**

Françoise Simonot-Lion, LORIA E-mail: Francoise.Simonot-Lion@loria.fr

Yves Sorel, INRIA E-mail: Yves.Sorel@inria.fr

Jean-Pierre Elloy, Yvon Trinquet Institut de Recherche en Communications et Cybernétique de Nantes (IRCCyN), France E-mail:

Jean-Pierre.Elloy@irccyn.ec-nantes.fr, Yvon.Trinquet@irccyn.ec-nantes.fr

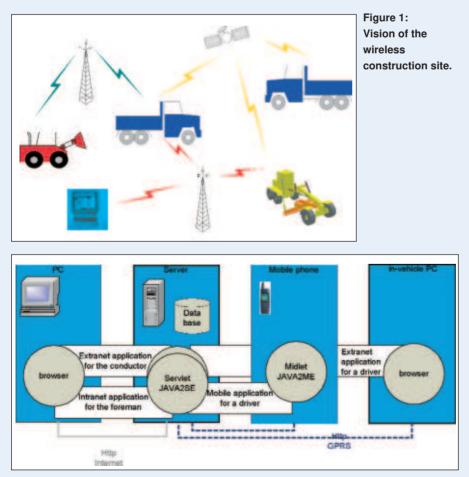

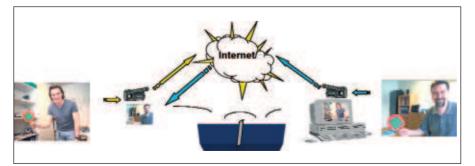

# Remote Control and Monitoring over the Internet – Wireless Construction Site

### by Leila Rannanjärvi

At the 'wireless construction site' trucks and bucket loaders complete transportation tasks cooperatively. The truck drivers send acknowledgements to the work-site server when a transportation task has been completed. The loaders send messages to the server after each loading event. This system enables the real-time management of trucks, bucket loaders, loads and even material administration. The driving force in this case is in the expected saving, since no material is lost and there is no need for extra kilometres or work hours to be charged.

This case is not a typical Internet application, because it focuses on enhanced production and not on entertainment or context sharing. The communication is more peer-to-peer and the system is a typical nomadic system. Nomadic systems are based on a core of fixed routers, switches and hosts; at the periphery of this fixed network, base stations with wireless communication capabilities control message traffic to and from dynamic configurations of mobile hosts. Nomadic distributed systems sit in between traditional fixed networks and ad-hoc networks.

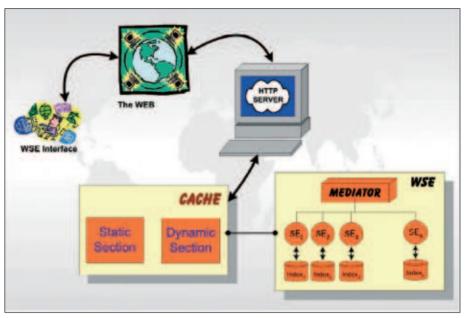

### **Wireless Construction Site**