# HCS08 Peripheral Module Quick Reference

### A Compilation of Demonstration Software for HCS08 Modules

This collection of code examples, useful tips, and quick reference material has been created to help users speed the development of their applications. Each section within this document contains an example that may be modified to work with HCS08 MCU Family members. When you're developing your application, consult your device data sheet for part-specific information, such as which versions of the peripheral modules are on your device.

This book begins with a section about device initialization, and then explores the different peripheral modules found in the HCS08 Family of MCUs. It concludes with two sections on implementing interrupt subroutines and making memory usage assignments in an embedded C environment with CodeWarrior.

Each section of this users guide contains:

- Programmer's model register figure for quick reference

- Example code

- Supplemental information supporting the code

All code is available inside a CodeWarrior project, or from Freescale's Web site in HCS08QGUGSW.zip.

In-depth material about using the HCS08 modules is also available in Freescale's application notes. See the Freescale Web site: http://freescale.com

#### **Topic Reference**

| Using the Device Initialization 3                                       |

|-------------------------------------------------------------------------|

| Using the Low Voltage Detect System 11                                  |

| Using the Internal Clock Source (ICS) 15                                |

| Using the Internal Clock Generator (ICG) 23                             |

| Programming the Low-Power Modes 29                                      |

| Using the External Interrupt Request Function (IRQ) 33                  |

| Using the Keyboard Interrupt (KBI) 37                                   |

| Using the Analog Comparator (ACMP) 41                                   |

| Using the 10-Bit Analog-to-Digital Converter (ADC) . 45                 |

| Using the Analog-to-Digital Converter (ATD) 49                          |

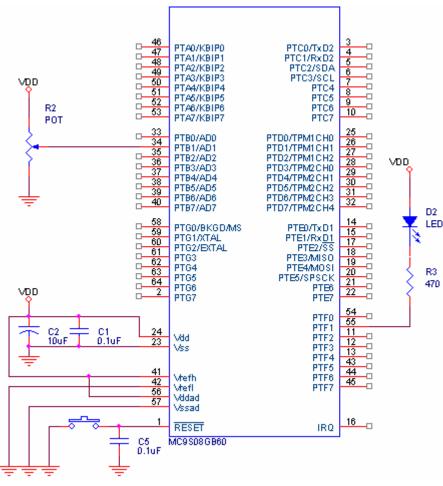

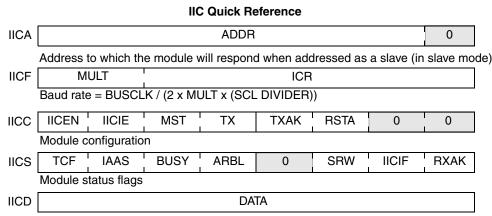

| Using the Inter-Integrated Circuit (IIC) Module 53                      |

| Using the Serial Communications Interface (SCI) 63                      |

| Using the Serial Peripheral Interface (SPI) 69                          |

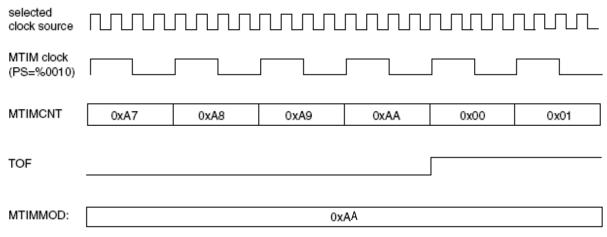

| Using the 8-Bit Modulo Timer (MTIM)73                                   |

| Using the Real-Time Interrupt (RTI) Function 77                         |

| Using the Input Capture and                                             |

| Output Compare Functions                                                |

| Generating PWM Signals<br>Using the HCS08 Timer (TPM)                   |

| Programming and Erasing Flash Memory                                    |

| Implementing Interrupt Service Routines (ISR) in C<br>Using CodeWarrior |

| Memory Mapping for HCS08 Family MCUs Using<br>CodeWarrior Software      |

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com/

### **Revision History**

| Date    | Revision<br>Level                                                                                  | Description     | Page<br>Number(s) |  |  |

|---------|----------------------------------------------------------------------------------------------------|-----------------|-------------------|--|--|

| 11/2005 | 0                                                                                                  | Initial release | N/A               |  |  |

| 2/2006  | 2/2006     1     Changing SCI1S1 line of code on page 65.<br>Replacement code page 83, 84, and 89. |                 |                   |  |  |

HCS08 Peripheral Module Quick Reference, Rev. 1

### **Freescale Semiconductor**

**Users Guide**

# Using the Device Initialization for the HCS08 Family Microcontrollers

By Gonzalo Delgado RTAC Americas México 2005

# 1 Overview

This document is a quick reference to the CodeWarrior Device Initialization tool for the HCS08 Family microcontrollers (MCUs). Basic information about the functional description and configuration are provided. The example may be modified to suit the specific needs for your application — refer to the data sheet for your device.

The Device Initialization (DI) tool is a user-friendly application integrated into the CodeWarrior version 5.0 that contains a powerful code generator used to create startup and initialization code that includes the configuration of registers to allow the use of specific modules in the MCU.

This time-saving application will help the user in the generation of code (relocatable ASM or C) to configure the registers of the MCU modules. With the DI, the user can migrate the initialization code from one family to another in an easier way.

This friendly graphical interface presents the MCU's pins, modules, and packages. When the user rolls the

#### **Table of Contents**

| 1 | Overview                         |

|---|----------------------------------|

| 2 | Device Initialization Main Menu  |

|   | (Integrated into CW Main Menu) 4 |

| 3 | Target CPU Window 6              |

| 4 | Inspector Dialog Window 7        |

| 5 | Error Window                     |

| 6 | Description of Generated Files   |

| 7 | Example Code and Explanation     |

#### Device Initialization Main Menu (Integrated into CW Main Menu)

mouse over the modules their pins are highlighted and a brief explanation of the device appears. Warnings appear when a value or configuration can't be defined. The DI has the ability to suggest or guide the user in the configuration of modules. There is a section of the registers concerned in each module and a brief description of each bit; these registers can be configured clicking bit by bit or with a predefined value.

The Device Initialization includes the following initialization modules, or beans<sup>1</sup>:

- Init\_ACMP\_HCS08

- Init\_ADC\_HC08

- Init\_ADC\_HCS08

- Init\_AnalogModule\_HC08

- Init\_CMT\_HCS08

- Init\_FLASH\_HCS08

- Init IIC HCS08

- Init RTI HCS08

- Init SCI HCS08

- Init SPI HCS08

- Init TPM HCS08

# 2 Device Initialization Main Menu (Integrated into CW Main Menu)

| File | Edit     | View     | Search    | Project | Processor  | r Expert | Device Initialization                            | Window    | Help          |   |

|------|----------|----------|-----------|---------|------------|----------|--------------------------------------------------|-----------|---------------|---|

| 'n   | <b>*</b> | <b>è</b> | ы         | 6 3<    | <b>h</b> 6 | 44       | Initialize Device<br>Backup Device Se            | ttings    |               |   |

| 05   | 50812_   | tim_in_  | _gb60 .ma | »       |            |          | Restore Device So<br>Update PE from P<br>Options |           |               |   |

|      | ) Sta    | indard   |           | -       | ] 🗈 😽      | ' 🌾 I    | Generate Code '0<br>View Report                  | 50812_tim | _in_gb60.mcp' |   |

| Fi   | les      | Link O   | rder   Ta | rgets   |            |          | wew Keport                                       | 5         |               | _ |

- Initialize Device This command opens Target CPU window.

- Backup Device Settings This command stores complete design into single configuration file. Directory and file name will be same as CW project. Previous version of the settings will be automatically stored in the same directory in the following way:

- ProjectName.iPE latest device settings

- ProjectName\_0.iPE oldest device settings

- ProjectName\_1.iPE next device settings

- ProjectName\_2.iPE next device settings

#### Using the Device Initialization for the HCS08 Family Microcontrollers

<sup>1.</sup> Not all 8-bit microcontrollers have the modules described in the list.

- ProjectName\_nnn.iPE previous device settings

- Restore Device Settings This command restores complete design from single configuration file. Directory and file name will be selectable by the user. The user can use also settings from different project see command Backup Device Settings.

- Update PE from Package Allows installing a patch or updating from the .PEUpd file.

- Options Defines the type of code that will be generated and options that will influence the code generation.

- Generate Code Generates code (Relocatable ASM or C).

- View Report Submenu:

- Project Settings Generates xml file with information about settings of all beans in the design.

- Register Settings Generates xml file with information about settings of all control registers modified by the design.

- Interrupt Usage Generates xml file with information about settings of all interrupt vectors used in the design.

- Pin Usage Generates xml file with information about settings of all pins used in the design.

#### 3 **Target CPU Window** С 🔣 Select CPU <u>P</u>ackage 📗 <u> G</u>enerate Code 📙 <u>B</u>ackup Bestore ? Help Q, ٩, Ħ ŧ# RESET PTG7 PTA1 KBI РТСО Тх PTA0 KBI PTC1 Rx PTE7 PTC2\_SD PTF6 PTA ртв PTC PTD РТСЗ ВС PTE5 PTE PTF PTG TPM1 РТС4 Vtef РТС5 TPM2 COP BTI SCI1 Vtefl РТС6 PTB7 AD SCI2 SPI1 ATD1 liC1 РТС7 PTB6 AD KBI1 IRQModule 🍘 СРО IntFLASH PTF2 PTB5 AE PTF3 PTR4 AD PTF4 PTB3 AD PTED\_TXD PTB2 AD PTE1 Rx PTB1\_AD MC9S08GB60CFU IRO РТВО АП PTF PTF (none) General purpose parallel 10 port PTF

This is the main window where the MCU modules are listed among with their pins. By clicking into the module user can access the configuration menu.

- Unused peripherals are grayed; used ones are highlighted and embossed.

- Single click to init peripheral and open inspector dialog.

- Button for code generation (see top panel of the window).

- CPU peripherals list mode view, which contains all peripherals in the list.

- Closing the window suspends Processor Expert (PE). PE asks the user to save design if it is not saved.

- Closing CW project closes the window.

- Target CPU window will be opened automatically with CW project if there is saved Device Initialization design (and was not suspended).

**Target CPU Window**

### 4 Inspector Dialog Window

|                                             | Bean Parameters  |     |           |          |           | Regist  | er Details |                          |

|---------------------------------------------|------------------|-----|-----------|----------|-----------|---------|------------|--------------------------|

| Device                                      | SCI1             | •   | SCI1      | •        | Name      | Address | Init.value | Register Map             |

| Settings                                    |                  |     |           |          | 🗄 SCI1BDH | 0x0018  | 00 H       |                          |

| Clock setting                               |                  |     |           |          | 🗄 SCI1BDL | 0x0019  | 04 H       |                          |

| 🖌 🖌 Baud rate divisor                       | 4                | D   |           |          | E SCI1C1  | 0x001A  | 00 H       |                          |

| L 🖌 Baud rate                               | 62499.984 baud   |     |           |          | E SCI1C2  | 0x001B  | 00 H       |                          |

| <ul> <li>Loop mode</li> </ul>               | Disabled         | 9   |           |          | 🗄 SCI1S1  | 0x001C  | CO H       |                          |

| <ul> <li>Receiver source</li> </ul>         | Loop mode        | •   |           |          | 🗄 SCI1S2  | 0x001D  | 00 H       |                          |

| <ul> <li>TxD1 pin direction</li> </ul>      | Input            | •   |           |          | 🗄 SCI1C3  | 0x001E  | 00 H       |                          |

| 🗸 Data Format                               | 8 bits           | -   |           |          | 🗄 SCI1D   | 0x001F  | 00 H       |                          |

| <ul> <li>Stop in Wait mode</li> </ul>       | Disabled         | 9   |           |          |           |         |            |                          |

| 🗸 Wake up                                   | Idle line wakeup | •   |           |          |           |         |            |                          |

| <ul> <li>Idle character counting</li> </ul> | After start bit  | •   |           |          |           |         |            |                          |

| Parity                                      | None             | -   |           |          |           |         |            |                          |

| <ul> <li>Send break</li> </ul>              | Disabled         | 9   |           |          |           |         |            |                          |

| <ul> <li>Receiver wakeup</li> </ul>         | Normal operation | •   |           |          |           |         |            |                          |

| Pins                                        |                  |     |           |          |           |         |            |                          |

| RxD pin allocation                          | Enabled          | 9   |           |          |           |         |            |                          |

| 🗸 🖌 🖌 🖌 🖌                                   | PTE1_RxD1        |     | PTE1_RxD1 |          |           |         |            |                          |

| TxD pin allocation                          | Enabled          | 9   |           |          |           |         |            |                          |

| 🗸 TxD pin                                   | PTE0_TxD1        |     | PTE0_TxD1 |          |           |         |            |                          |

| Interrupts                                  |                  |     |           |          |           |         |            |                          |

| Tx interrupt                                |                  |     |           |          |           |         |            |                          |

| <ul> <li>Interrupt</li> </ul>               | Vsci1tx          |     | Vsci1tx   |          |           |         |            |                          |

| <ul> <li>Transmit interrupt</li> </ul>      | Disabled         | 9   |           |          |           |         |            |                          |

| 🖌 🖌 Transmission complete i                 | Disabled         | 9   |           |          |           |         |            |                          |

| 🖌 ISB name                                  |                  |     |           |          |           |         |            |                          |

| Bx interrupt                                |                  |     |           |          |           |         |            |                          |

| 🖌 🖌 Interrupt                               | Vsci1rx          |     | Vsci1rx   |          |           |         |            |                          |

| 🖌 🖌 Receive interrupt                       | Disabled         | - Đ |           | <b>•</b> |           |         |            |                          |

| N Disable Peripheral Initiali               | 1                |     |           |          |           |         |            | <u>D</u> K <b>X</b> Canc |

This window shows all the options available for configuration with the selected module in different menus and submenus.

- Cancel restores original design settings (design state before opening the inspector)

- This windows contains corresponding values of control registers (see right side) based on bean settings. It allows modification of control register values and corresponding bean settings are updated according to the value.

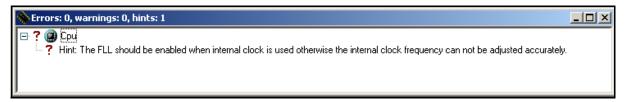

### 5 Error Window

Error window will be displayed only if an error occurs. After resolving errors the window hides automatically. An error is generated when the user misconfigures a module or parameters are missing.

Using the Device Initialization for the HCS08 Family Microcontrollers

## 6 Description of Generated Files

- Include file (\*.inc or \*.h) .\*.h for C callable option. Note: Generated file name can be selected using option "Generated file"

- Implementation file (\*.asm or \*.c) contains init function MCU\_init that initializes selected peripherals, interrupt vector table and selected interrupt service routines.

# 7 Example Code and Explanation

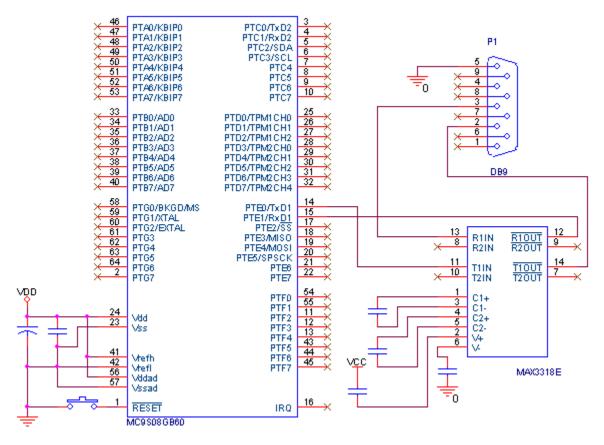

This example code shows initializing the SCI module to 19200 baud rate on the MC9S08GB60.

- 1. Open CodeWarrior version 5.0

- 2. Create a new project in C

- 3. Select MC9S08GB60 under the derivative list in the HCS08 derivative.

- 4. Under Rapid Application Development options, select Device Initialization

- 5. Select CPU package from the list

- 6. Click in the CPU module

| Inspector MC9508GB60                           | ero<br>Bean Parameters  |          |                     | 13   |                   | Dogia   | ter Details |               | ×        |

|------------------------------------------------|-------------------------|----------|---------------------|------|-------------------|---------|-------------|---------------|----------|

| 001.                                           |                         | -        |                     | _    |                   |         |             | D             | Carlot   |

| CPU type                                       | MC9S08GB60CFU           | •        |                     |      | Name              | Address | Init.value  | Register Map  | -        |

| Clock settings                                 |                         | _        | 0.01.01             | -    | PTASE             | 0x0002  | 00 <u>H</u> |               | 21       |

| <ul> <li>Source CPU clock</li> </ul>           | Internal Clock          | <b>•</b> | 8.0 MHz             |      | PTBSE             | 0x0006  | 00 <u>H</u> |               | 4        |

| Internal Clock                                 |                         |          |                     | 1000 | PTCSE             | A000x0  | 00 <u>H</u> |               | 41       |

| <ul> <li>Internal oscillator freque</li> </ul> |                         |          | 250.0 kHz; Frequeni |      | PTDSE             | 0x000E  | 00 <u>H</u> |               | 41       |

| E Initialize trim value                        | 1.1.0                   | 0        |                     |      | PTESE             | 0x0012  | 00 <u>H</u> | 0000000       | 41       |

| External Clock                                 | Enabled                 | 9        |                     |      | PTFSE             | 0x0042  | 00 <u>H</u> | 00000000      | 21       |

| - Cocillator frequency [M                      |                         |          | 4.0 MHz             |      | PTGSE             | 0x0046  | 00 <u>H</u> | 00000000      | 21       |

| <ul> <li>External Clock Source</li> </ul>      |                         | •        |                     |      | ICGC1             | 0x0048  | 44 <u>H</u> |               | <u>}</u> |

| └ ✔ Xtal range                                 | 1MHz-16MHz              | •        |                     |      | ICGC2             | 0x0049  | 00 <u>H</u> | 00000000      | 2        |

| Clock divider                                  | Auto selected prescaler | •        |                     |      | ICGS1             | 0x004A  | 00 H        |               | E.       |

| <ul> <li>Internal bus clock</li> </ul>         | 4.0                     |          | 4.0 MHz             |      | ICGS2             | 0x004B  | 00 H        |               | Þ.       |

| <ul> <li>Fixed frequency clock</li> </ul>      | 4.0                     |          | 4.0 MHz             | Ð    | ICGFLTU           | 0x004C  | 00 H        |               | Þ.       |

| FLL clock                                      | Disabled                | 0        |                     | Ð    | ICGFLTL           | 0x004D  | 00 H        | *******       | b.       |

| Low-power modes se                             |                         |          |                     | Ð    | ICGTRM            | 0x004E  | 80 H        | *******       | E.       |

| □ STOP instruction e                           | no                      | -        |                     | Ð    | SRS               | 0x1800  | ????0??0 H  | *******       | F.       |

| Maskable CPU interrupts                        | interrupts enabled      | -        | 1                   | E    | SOPT              | 0x1802  | 53 H        |               | E.       |

| Internal peripherals                           |                         |          |                     | Œ    | SDIDH             | 0x1806  | 00 H        | *******       | F.       |

| CPU interrupts                                 |                         |          |                     | Ð    | SDIDL             | 0x1807  | 02 H        | *******       | F.       |

|                                                |                         |          |                     | Ð    | SPMSC1            | 0x1809  | 10 H        |               | 5        |

|                                                |                         |          |                     | Ð    | SPMSC2            | 0x180A  | 00 H        |               | 3        |

|                                                |                         |          |                     | Ð    | <b>NVBACKKEY0</b> | 0xFFB0  | FF H        | *******       |          |

|                                                |                         |          |                     | Đ    | NVBACKKEY1        | 0xFFB1  | FF H        |               |          |

|                                                |                         |          |                     | Ð    |                   | 0xFFB2  | FF H        |               |          |

|                                                |                         |          |                     | E    |                   | 0xFFB3  | FF H        |               |          |

|                                                |                         |          |                     | E    |                   | 0xFFB4  | FF H        |               | -        |

|                                                |                         |          |                     |      | NVBACKKEY5        | 0xFFB5  | FF H        |               |          |

|                                                |                         |          |                     |      | NVBACKKEY6        | 0xFFB6  | FF H        |               | -        |

|                                                |                         |          |                     |      | NVBACKKEY7        | 0xFFB7  | FF H        |               |          |

|                                                |                         |          |                     | 100  | IT DALKKE IT      | ONT D7  |             |               | -        |

|                                                |                         |          |                     |      |                   |         | 2 .         | 🖊 🛛 K 🛛 🗶 Can | cel      |

- 1. Go to Clock settings...Internal Oscillator Frequency and establish the frequency to 250 kHz

- 2. Go to Clock settings...Source CPU Clock and select Internal Clock

- 3. Press OK

- 4. Click in the SCIx module (x stands for the number of the device)

#### Using the Device Initialization for the HCS08 Family Microcontrollers

| Inspector Init_SCI                          |                  |                   |         |           |         |            | ×            |

|---------------------------------------------|------------------|-------------------|---------|-----------|---------|------------|--------------|

|                                             | Bean Parameters  |                   |         |           | Regist  | er Details |              |

| <ul> <li>Device</li> </ul>                  | SCI1             |                   | SCI1    | Name      | Address | Init.value | Register Map |

| E Settings                                  |                  |                   |         | E SCI1BDH | 0x0018  | 00 H       |              |

| Clock setting                               |                  |                   |         | SCI1BDL   | 0x0019  | OD H       |              |

| <ul> <li>Baud rate divisor</li> </ul>       | 13               | D                 |         | SCI1C1    | 0x001A  | 00 H       | 00000000     |

| Baud rate                                   | 19230.769 baud   |                   |         | E SCI1C2  | 0x001B  | 2C H       | 0000000      |

| <ul> <li>Loop mode</li> </ul>               | Disabled         | 0                 |         | E SCI1S1  | 0x001C  | C0 H       | *******      |

| <ul> <li>Receiver source</li> </ul>         | Loop mode        | -                 |         | SCI1S2    | 0x001D  | 00 H       | *******      |

| <ul> <li>TxD1 pin direction</li> </ul>      | Input            | -                 |         | E SCI1C3  | 0x001E  | 00 H       | 00000000     |

| - 🖌 Data Format                             | 8 bits           | -                 |         | E SCI1D   | 0x001F  | 00 📕       | *******      |

| <ul> <li>Stop in Wait mode</li> </ul>       | Disabled         | 0                 |         |           |         |            |              |

| 🖌 🖌 Wake up                                 | Idle line wakeup | 0 1 1 1 0 1 1 1 0 |         |           |         |            |              |

| <ul> <li>Idle character counting</li> </ul> | After start bit  | Ŧ                 |         |           |         |            |              |

| <ul> <li>Parity</li> </ul>                  | None             | -                 |         |           |         |            |              |

| 🖌 Send break                                | Disabled         | 0                 |         |           |         |            |              |

| L Receiver wakeup                           | Normal operation | -                 |         |           |         |            |              |

| 🗉 Pins                                      |                  |                   |         |           |         |            |              |

| Interrupts                                  |                  |                   |         |           |         |            |              |

| E Tx interrupt                              |                  |                   |         |           |         |            |              |

| - 🖂 Rx interrupt                            |                  |                   |         |           |         |            |              |

| <ul> <li>Interrupt</li> </ul>               | Vsci1rx          |                   | Vsci1rx |           |         |            |              |

| <ul> <li>Receive interrupt</li> </ul>       | Enabled          | 0                 |         |           |         |            |              |

| <ul> <li>Idle line interrupt</li> </ul>     | Disabled         | 0                 |         |           |         |            |              |

| <ul> <li>ISB name</li> </ul>                | Vscilin isr      |                   |         |           |         |            |              |

| L Error interrupt                           |                  |                   |         |           |         |            |              |

| Initialization                              |                  |                   |         |           |         |            |              |

| 🚽 Transmitter                               | Enabled          | 0                 |         |           |         |            |              |

| └ ✔ Receiver                                | Enabled          | 0                 |         |           |         |            |              |

|                                             |                  |                   |         |           |         |            |              |

|                                             |                  |                   |         | l         | -       |            |              |

| S Disable Peripheral Initia                 | lization         |                   |         |           |         | ? 🗸        | DK X Cancel  |

- 1. Go to the section Settings...Clock Setting and change the baud rate divisor to 13. (This will lead to a result of a 19230.769 baud rate with a 0.16% of error)

- 2. Go to Interrupts...Rx Interrupt; enable Receive Interrupt and set a name to ISR for the Receive.

- 3. Go to Initialization and enable Transmitter and Receiver.

- 4. Press OK

- 5. Press Generate Code

- 6. Select the Generated File type, in this case C callable and Save and add files to project option.

- 7. Press Generate

- 8. This will generate two pieces of code, one has the method declaration and the other is the MCU\_Init function where all the needed on-chip peripherals are initialized.

- 9. Include the MCUInit.h in the main file using the command: #include "MCUinit.h"

- 10. Call the MCU\_Init (included in the MCUinit.c) function: MCU\_init();

#### **Example Code and Explanation**

• Place your code into the main or into the interrupt function located in the MCUInit.c under the Generated Code directory.

#### NOTE

This example was developed using the CodeWarrior Development Studio for Freescale HC(S)08 version 5.0, and was expressly made and tested for the MC9S08GB60. Changes will be required before the code can be used to initialize another MCU. Every microcontroller requires an initialization code that depends on the application and the microcontroller itself.

### Freescale Semiconductor Users Guide

# Using the Low Voltage Detect System for the HCS08 Family Microcontrollers

by: Andrés Barrilado González RTAC Americas México 2005

### 1 Overview

This is a quick reference for using the low voltage detect (LVD) system on an HCS08 microcontroller (MCU). Basic information about the functional description and configuration options is provided. The following examples may be modified to suit your application — refer to the data sheet for your device.

#### **Table of Contents**

| Overview                     | 11 |

|------------------------------|----|

| Code Example and Explanation | 12 |

| Hardware Implementation      |    |

#### LVD Quick Reference

The LVD function registers are device dependent. Please see the data sheet for your device to check availability / location for these bits. For example, on some devices, the low voltage warning bits are moved to another register (SPMSC3), and there is a PDF (power-down flag) in bit 4 of SPMSC2.

1

2 3

| SPMSC1                                                                                                                                                                                                                                                                                                                                                                          | LVDF     | LVDACK    | LVDIE      | LVDRE      | LVDSE        | LVDE   |     | BGBE |                              |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------|------------|------------|--------------|--------|-----|------|------------------------------|--|

| System power management status and control register 1                                                                                                                                                                                                                                                                                                                           |          |           |            |            |              |        |     |      |                              |  |

| LVDF — flags low-voltage detectionsLVDSE — enables/disables the LVD in s<br>modeLVDACK — clears the LVD flagLVDIE — enables/disables LVD-caused interruptions<br>LVDRE — enables/disables LVD-caused resetsLVDE — enables/disables the LVD moduLVDRE — enables/disables LVD-caused resetsBGBE — bandgap buffer enable<br>(not available on all devices — check y<br>data sheet) |          |           |            |            |              |        |     |      | s the LVD module<br>r enable |  |

| SPMSC2                                                                                                                                                                                                                                                                                                                                                                          | LVWF     | LVWACK    | LVDV       | LVWV       | PPDF         | PPDAC  | PDC | PPDC |                              |  |

|                                                                                                                                                                                                                                                                                                                                                                                 | System p | ower mana | agement st | atus and c | ontrol regis | ster 2 |     |      |                              |  |

| System power management status and control register 2<br>LVWF — flags low-voltage warnings<br>LVWACK — clears the low voltage warning flag<br>LVDV — selects between high or low low-voltage<br>detect trip point voltage<br>LVWV — selects between high or low low-voltage<br>warning trip point voltage                                                                       |          |           |            |            |              |        |     |      | er-down acknowledge<br>htrol |  |

This example code is available inside the CodeWarrior project or from the Freescale Web site in HCS08QRUGSW.zip.

The following example configures the LVD using the interrupt-based approach to turn on an LED while voltage levels are low. It also polls the low-voltage warning flag to turn on a second LED in case the low-voltage level is approaching.

The zip contains the following functions:

- main polls the low-voltage warning flag endlessly and moves the result to a MCU pin where an LED is attached

- MCU\_init Configures hardware and the LVD module to accept interrupts and sets the LVD/LVW trip voltages

- Vlvd\_isr Responds to LVD interruptions.

Using Device Initialization, the LVD configuration applied for this example is:

- LVD interrupt enabled

- High low-voltage detect trip voltage

- High low-voltage warning trip voltage

- No reset in case of low-voltage detection

- No low-voltage detection in STOP mode

Please refer to the code for specifics about the configuration.

After the LVD is configured, and if a low voltage level is detected, a service routine must clear the LVD flag by setting the acknowledge bit. In this example, a bit is also set at a MCU pin in order to turn on a warning LED.

Please refer to the source code for more details.

#### NOTE

This software was developed using the CodeWarrior Development Studio for HC(S)08 version 5.0 using Device Initialization and tested using a MC9S08GB60 running in self-clocked mode. Coding changes may be needed to initialize another MCU. Every microcontroller needs an initialization code that depends on the application and the microcontroller itself.

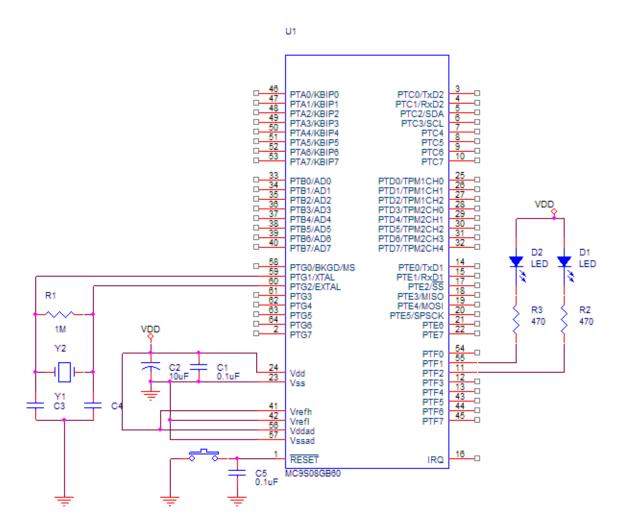

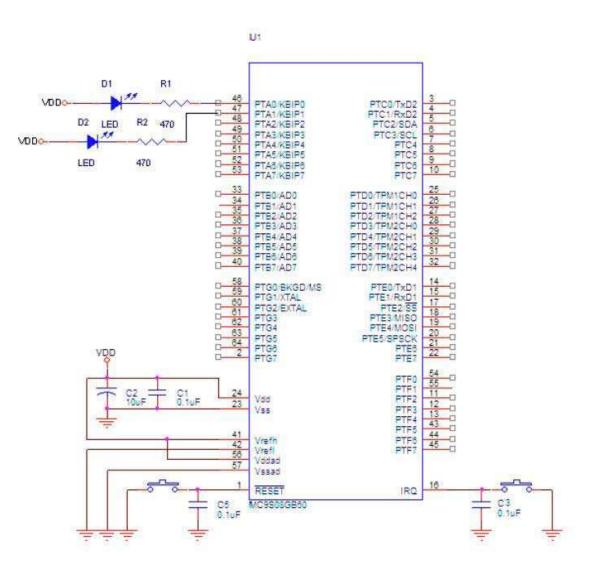

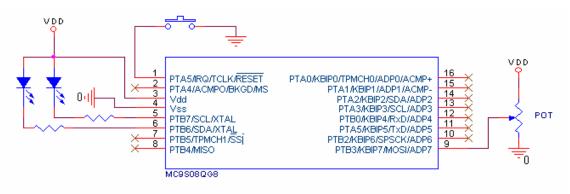

# 3 Hardware Implementation

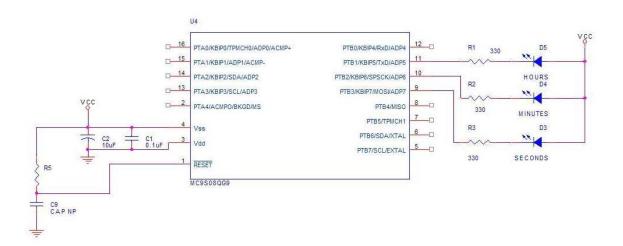

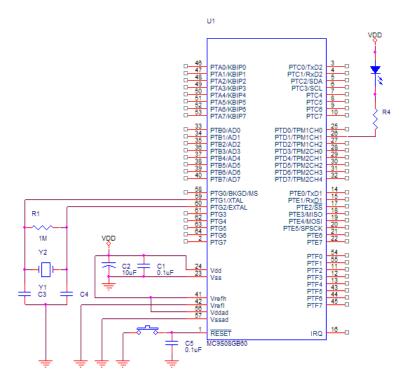

This schematic shows the hardware used to exercise the code provided.

Using the Low Voltage Detect System for the HCS08 Family Microcontrollers

#### Hardware Implementation

### **Freescale Semiconductor**

**Users Guide**

# Using the Internal Clock Source (ICS) for the HCS08 Microcontrollers

by: Sergio García de Alba Garcin RTAC Americas México 2005

# 1 Overview

This is a quick reference for using the internal clock source (ICS) module on an HCS08 microcontroller (MCU). Basic information about the functional description and configuration options is provided. The following examples may be modified to suit your application — refer to the data sheet for your device.

#### **Table of Contents**

| 1 | Ove | erview                           |

|---|-----|----------------------------------|

| 2 | Coo | de Example and Explanation 16    |

|   | 2.1 | FLL Engaged External Example 16  |

|   | 2.2 | FLL Bypassed External Example 17 |

|   | 2.3 | FLL Bypassed External Low Power  |

|   |     | Example 18                       |

|   | 2.4 | FLL Bypassed Internal Example 19 |

|   | 2.5 | FLL Bypassed Internal Low Power  |

|   |     | Example                          |

|   | 2.6 | FLL Engaged Internal Example 20  |

| 3 | Tip | s and Recommendations            |

#### **ICS Quick Reference**

| ICSC1  | CLKS                        | KS RDIV IREFS IRCLKEN |                |             |       |         |               |  |

|--------|-----------------------------|-----------------------|----------------|-------------|-------|---------|---------------|--|

|        | Module and internal osci    | illator configura     | ation          |             |       |         | <u> </u>      |  |

| ICSC2  | BDIV                        | RANGE                 | HGO            | LP          | EREFS | ERCLKEN | EREFSTEN      |  |

|        | Module and external osc     | illator configur      | ation          |             |       |         |               |  |

| ICSTRM |                             |                       | TR             | M           |       |         |               |  |

|        | Internal oscillator trim va | lue: higher val       | ue = slower fr | equency     |       |         |               |  |

| ICSSC  |                             | 1                     | 1              | CLI         | KST   | OSCINIT | FTRIM         |  |

|        |                             |                       |                | Module stat | us    | Fi      | ne trim value |  |

|        |                             |                       |                |             |       |         |               |  |

© Freescale Semiconductor, Inc., 2005, 2006. All rights reserved.

The ICS provides several options for clock sources. This offers great flexibility when having to choose between precision, cost, current consumption, and performance. The weight of each one of these factors will depend on the requirements and characteristics of the application being developed.

### 2.1 FLL Engaged External Example

Our first example will be configuring the microcontroller for FLL engaged external (FEE) mode using a 4.9152 MHz crystal as an external clock reference. Using this mode we can have a bus frequency in the range of 1 MHz <  $f_{bus}$  < 10 MHz, high clock accuracy, and medium/high cost (because a crystal, resonator, or external oscillator is required).

The bus frequency that will be generated is calculated with the following formula:

$f_{bus} = (f_{ext} \div RDIV \times 512 \div BDIV) \div 2$

Where  $f_{ext}$  is the frequency of the external reference (in this example we assume a 4.9152 MHz crystal is being used). RDIV bits must be programmed to divide  $f_{ext}$  to be within the range of 31.25 kHz to 39.0625 kHz (in this example they divide  $f_{ext}$  by 128). Then the FLL multiplies the frequency by 512, and BDIV bits divide it (in this example they are programmed to divide by 2). Finally, the clock signal is divided by 2 to give the bus clock.

In our example  $f_{bus}$  will be: 4.9152 MHz. For this example HGO was programmed to configure the external oscillator for low power operation (reduced amplitude).

| ICSC1 = 0 | ICSC1 = 0x38 |     |                                           |  |  |  |  |  |

|-----------|--------------|-----|-------------------------------------------|--|--|--|--|--|

| Bits 7:6  | CLKS         | 00  | Output of FLL is selected                 |  |  |  |  |  |

| Bits 5:3  | RDIV         | 111 | Divides reference clock by 128            |  |  |  |  |  |

| Bit 2     | IREFS        | 0   | External reference clock selected         |  |  |  |  |  |

| Bit 1     | IRCLKEN      | 0   | ICSIRCLK inactive                         |  |  |  |  |  |

| Bit 0     | IREFSTEN     | 0   | Internal reference clock disabled in stop |  |  |  |  |  |

The ICS control registers will be programmed in the following way:

| ICSC2 = 0x64 |          |    |                                                           |

|--------------|----------|----|-----------------------------------------------------------|

| Bits 7:6     | BDIV     | 01 | Set to divide selected clock by 2                         |

| Bit 5        | RANGE    | 1  | High frequency range selected for the external oscillator |

| Bit 4        | HGO      | 0  | Configures external oscillator for low power operation    |

| Bit 3        | LP       | 0  | FLL is not disabled in bypass mode                        |

| Bit 2        | EREFS    | 1  | Oscillator requested                                      |

| Bit 1        | ERCLKEN  | 0  | ICSERCLK inactive                                         |

| Bit 0        | EREFSTEN | 0  | External reference clock disabled in stop                 |

The following piece of code in C would set this configuration:

#### NOTE

The while loop is used to wait for the initialization cycles of the external crystal to complete.

### 2.2 FLL Bypassed External Example

This time, we will configure the microcontroller to work in FLL bypassed external mode (FBE) using a 4.9152 MHz crystal as a reference. This mode allows for a bus frequency in the range 2 kHz < f<sub>bus</sub> < 2.5 MHz, very high clock accuracy, low power consumption, and medium/high cost (because a crystal, resonator, or external oscillator is required).

The bus frequency that will be generated is calculated with the following formula:

$f_{bus} = (f_{ext} * 1/BDIV) / 2$

Where  $f_{ext}$  is the frequency of the external reference (in this example we assume a 4.9152 MHz crystal is being used). RDIV bits must be programmed to divide  $f_{ext}$  to be within the range of 31.25 kHz to 39.0625 kHz (in this example they divide  $f_{ext}$  by 128).

In our example,  $f_{bus}$  will be: 1.228 MHz. In this example we programmed HGO to configure the external oscillator for high gain to provide higher amplitude for improved noise immunity.

The ICS control registers will be programmed in the following way:

| ICSC1 = 02 | ICSC1 = 0xB8 |     |                                           |  |

|------------|--------------|-----|-------------------------------------------|--|

| Bits 7:6   | CLKS         | 10  | External reference clock is selected      |  |

| Bits 5:3   | RDIV         | 111 | Divides reference clock by 128            |  |

| Bit 2      | IREFS        | 0   | External reference clock selected         |  |

| Bit 1      | IRCLKEN      | 0   | ICSIRCLK inactive                         |  |

| Bit 0      | IREFSTEN     | 0   | Internal reference clock disabled in stop |  |

| ICSC2 = 0x74 |          |    |                                                           |

|--------------|----------|----|-----------------------------------------------------------|

| Bits 7:6     | BDIV     | 01 | Set to divide selected clock by 2                         |

| Bit 5        | RANGE    | 1  | High frequency range selected for the external oscillator |

| Bit 4        | HGO      | 1  | Configures external oscillator for high gain operation    |

| Bit 3        | LP       | 0  | FLL is not disabled in bypass mode                        |

| Bit 2        | EREFS    | 1  | Oscillator requested                                      |

| Bit 1        | ERCLKEN  | 0  | ICSERCLK inactive                                         |

| Bit 0        | EREFSTEN | 0  | External reference clock disabled in stop                 |

The following piece of code in C would set this configuration:

```

ICSC2= 0x74;

while(ICSSC_OSCINIT==0);

ICSC1= 0xB8; //Best practice is to enable external clock, then switch to FBE mode

```

#### NOTE

The while loop is used to wait for the initialization cycles of the external crystal to complete.

### 2.3 FLL Bypassed External Low Power Example

This mode is very similar to FLL bypassed external mode (FBE), with the difference that the FLL is turned off to reduce power consumption. For this example, we will also use a 4.9152 MHz crystal as a reference. This mode allows for a bus frequency  $f_{bus} \leq 10$  MHz, very high clock accuracy, very low power consumption, and medium/high cost (because a crystal, resonator, or external oscillator is required).

The bus frequency that will be generated is calculated with the following formula:

$f_{bus} = (f_{ext} * 1/BDIV) / 2$

Where  $f_{ext}$  is the frequency of the external reference (in this example we assume a 4.9152 MHz crystal is being used). Although this FLL will be disabled in this example, it is best practice to set the RDIV bits to divide  $f_{ext}$  to be within the range 31.25 kHz to 39.0625 kHz (in this example,  $f_{ext}$  is divided by 128).

In our example,  $f_{bus}$  will be: 2.457 MHz. For this example, HGO was programmed to configure the external oscillator for low power operation (reduced amplitude).

The ICS control registers will be programmed in the following way:

| ICSC1 = 0 | ICSC1 = 0x80 |     |                                           |  |

|-----------|--------------|-----|-------------------------------------------|--|

| Bits 7:6  | CLKS         | 10  | External reference clock is selected      |  |

| Bits 5:3  | RDIV         | 111 | Divides reference clock by 128            |  |

| Bit 2     | IREFS        | 0   | External reference clock selected         |  |

| Bit 1     | IRCLKEN      | 0   | ICSIRCLK inactive                         |  |

| Bit 0     | IREFSTEN     | 0   | Internal reference clock disabled in stop |  |

| ICSC2 = 0x2C |          |    |                                                           |

|--------------|----------|----|-----------------------------------------------------------|

| Bits 7:6     | BDIV     | 00 | Set to divide selected clock by 1                         |

| Bit 5        | RANGE    | 1  | High frequency range selected for the external oscillator |

| Bit 4        | HGO      | 0  | Configures external oscillator for low power operation    |

| Bit 3        | LP       | 1  | FLL is disabled in bypass mode (unless BDM is active)     |

| Bit 2        | EREFS    | 1  | Oscillator requested                                      |

| Bit 1        | ERCLKEN  | 0  | ICSERCLK inactive                                         |

| Bit 0        | EREFSTEN | 0  | External reference clock disabled in stop                 |

The following piece of code in C would set this configuration:

#### NOTE

The while loop is used to wait for the initialization cycles of the external crystal to complete.

### 2.4 FLL Bypassed Internal Example

In this example, the microcontroller will be configured to operate in FLL bypassed internal mode (FBI). This mode allows a bus frequency in the range 2 kHz  $\leq f_{bus} \leq 19$  kHz, low cost, and good accuracy (if trimmed).

The bus frequency that will be generated is calculated with the following formula:

$f_{bus} = (f_{irc} * 1/BDIV) / 2$

Where  $f_{irc}$  is the frequency of the internal reference clock (in this example we assume 32.768 kHz).

In our example  $f_{bus}$  will be: 8.19 kHz.

The ICS control registers will be programmed in the following way:

| ICSC1 = 0x44 |          |     |                                           |

|--------------|----------|-----|-------------------------------------------|

| Bits 7:6     | CLKS     | 01  | Internal reference clock is selected      |

| Bits 5:3     | RDIV     | 000 | Divides reference clock by 1              |

| Bit 2        | IREFS    | 1   | Internal reference clock selected         |

| Bit 1        | IRCLKEN  | 0   | ICSIRCLK inactive                         |

| Bit 0        | IREFSTEN | 0   | Internal reference clock disabled in stop |

| ICSC2 = 0 | ICSC2 = 0x40 |    |                                                        |  |

|-----------|--------------|----|--------------------------------------------------------|--|

| Bits 7:6  | BDIV         | 01 | Set to divide selected clock by 2                      |  |

| Bit 5     | RANGE        | 0  | Low frequency range for the external oscillator        |  |

| Bit 4     | HGO          | 0  | Configures external oscillator for low power operation |  |

| Bit 3     | LP           | 0  | FLL is not disabled in bypass mode                     |  |

| Bit 2     | EREFS        | 0  | External clock source requested                        |  |

| Bit 1     | ERCLKEN      | 0  | ICSERCLK inactive                                      |  |

| Bit 0     | EREFSTEN     | 0  | External reference clock disabled in stop              |  |

The following piece of code in C would set this configuration:

ICSC1= 0x44; | // If switching from FEE, FBE, or FBELP into FBI, delay for a time equal to tIRST ICSC2= 0x40;

### 2.5 FLL Bypassed Internal Low Power Example

This mode is very similar to FLL bypassed internal mode (FBI), with the difference that the FLL is turned off to reduce power consumption. This mode allows for a bus frequency in the range 2 kHz < f<sub>bus</sub> < 19 kHz, low cost, very low power consumption, and good accuracy (if trimmed).

The bus frequency that will be generated is calculated with the following formula:

$f_{bus} = (f_{irc} * 1/BDIV) / 2$

Where  $f_{irc}$  is the frequency of the internal reference clock (in this example we assume 32.768 kHz).

In our example, f<sub>bus</sub> will be: 16.38 kHz.

| ICSC1 = 0 | ICSC1 = 0x44 |     |                                           |  |

|-----------|--------------|-----|-------------------------------------------|--|

| Bits 7:6  | CLKS         | 01  | Internal reference clock is selected      |  |

| Bits 5:3  | RDIV         | 000 | Divides reference clock by 1              |  |

| Bit 2     | IREFS        | 1   | Internal reference clock selected         |  |

| Bit 1     | IRCLKEN      | 0   | ICSIRCLK inactive                         |  |

| Bit 0     | IREFSTEN     | 0   | Internal reference clock disabled in stop |  |

The ICS control registers will be programmed in the following way:

| ICSC2 = 0x08 |          |    |                                                        |

|--------------|----------|----|--------------------------------------------------------|

| Bits 7:6     | BDIV     | 00 | Set to divide selected clock by 1                      |

| Bit 5        | RANGE    | 0  | Low frequency range for the external oscillator        |

| Bit 4        | HGO      | 0  | Configures external oscillator for low power operation |

| Bit 3        | LP       | 1  | FLL is disabled in bypass mode (unless BDM is active)  |

| Bit 2        | EREFS    | 0  | External clock source requested                        |

| Bit 1        | ERCLKEN  | 0  | ICSERCLK inactive                                      |

| Bit 0        | EREFSTEN | 0  | External reference clock disabled in stop              |

The following piece of code in C would set this configuration:

ICSC1= 0x44; //If switching from FEE, FBE, or FBELP into FBILP, delay for a time equal to tIRST ICSC2= 0x08;

### 2.6 FLL Engaged Internal Example

In this example, we will use the microcontroller in FLL engaged internal mode (FEI), which is the default mode of operation for the ICS module. When this mode is entered out of reset the bus frequency will default to approximately 4.1943 MHz.

This mode allows for a bus frequency in the range 1  $MHz < f_{bus} < 10 MHz$ , low cost, quick and reliable system startup, and good accuracy (if trimmed).

In our example,  $f_{bus}$  will be around 4.1943 MHz, which is the default frequency after reset. To operate in FLL engaged internal mode (FEI) no register needs to be written if the default settings are suitable. If required, the default configuration can be changed. For instance, the internal reference clock could be

trimmed writing the ICSTRM register or the bus frequency could be reduced by changing the BDIV bits in the ICSC2 register.

The internal reference must be trimmed to less than 39.0625 kHz before BDIV is set for divide by 1.

### 3 Tips and Recommendations

- When ICS is configured for FEE or FBE mode, input clock source must be divisible using RDIV to within the range of 31.25 kHz to 39.0625 kHz.

- Check the external and internal oscillator characteristics in the data sheet for electrical and timing specifications.

- The external oscillator can be configured to provide a higher amplitude output for noise immunity. This mode of operation is selected by HGO = 1.

- When switching modes of operation, if the newly selected clock is not available, the previous clock will remain selected.

- The TRIM and FTRIM value will not be affected by a reset.

- When using an XTAL (crystal) be sure to use high quality components (XTAL, resistors, and capacitors). Use low inductance resistors such as carbon composition resistors. Capacitors must be high quality ceramic capacitors specifically designed for high frequency applications. If using a resonator, be sure to use a high-quality resonator.

- For the values of the components used with the XTAL or resonator, consult the manufacturer or the device's data sheet (typical values are: C1 and C2 in the range of 5 pF to 25 pF,  $R_F$  in the range 1–10 MQ,  $R_S$  in the range of 0–100 kQ). Take into consideration stray capacitance when sizing C1 and C2.

- Good layout practices are fundamental for correct operation and reliability of the oscillator (crystal or resonator). Have the oscillator's components very close to the XTAL and EXTAL pins to minimize the length of the routing traces. Avoid high frequency/current signals near the oscillator to prevent crosstalk and to minimize noise, etc.

- Freescale recommends an evaluation of the application board and chosen resonator or crystal by the resonator or crystal manufacturer.

#### NOTE

- This software was developed using the CodeWarrior Development Studio for HC(S)08 version 5.0 using Device Initialization.

- A small project is included that was tested in the MC9S08QG8 that configures the microcontroller as described in the previous examples depending on which define# is not commented. An LED blinks at a frequency which depends on the ICS mode of operation selected.

#### **Tips and Recommendations**

### **Freescale Semiconductor Users** Guide

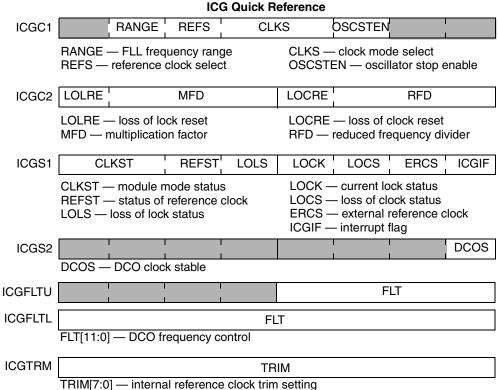

Using the Internal Clock Generator (ICG) for the HCS08 Family Microcontrollers

by: Sergio García de Alba Garcin **RTAC Americas** México 2005

### Overview

This is a quick reference for using the internal clock generator (ICG) module on an HCS08 microcontroller (MCU). Basic information about the functional description and configuration options is provided. The following examples may be modified to suit your application — refer to the data sheet for your device.

#### Table of Contents

| 1 | Ove                             | Overview                        |  |  |  |  |  |  |

|---|---------------------------------|---------------------------------|--|--|--|--|--|--|

| 2 | Code Example and Explanation 24 |                                 |  |  |  |  |  |  |

|   | 2.1                             | FLL Engaged External Example 24 |  |  |  |  |  |  |

|   | 2.2                             | FLL Engaged Internal Example 25 |  |  |  |  |  |  |

|   | 2.3                             | FLL Bypassed External Example   |  |  |  |  |  |  |

|   | 2.4                             | Self-Clocked Mode Example       |  |  |  |  |  |  |

| 3 | Tips and Recommendations        |                                 |  |  |  |  |  |  |

© Freescale Semiconductor, Inc., 2005, 2006. All rights reserved.

This example code is available inside the CodeWarrior project or from the Freescale Web site in HCS08QRUGSW.zip.

The ICG provides several options for clock sources. This offers great flexibility when having to choose between precision, cost, current consumption, and performance. The weight of each one of these factors will depend on the requirements and characteristics of the application being developed.

### 2.1 FLL Engaged External Example

Our first example will be configuring the microcontroller for FLL engaged external (FEE) mode using a 32 kHz crystal as an external clock reference. Using this mode we can have a bus frequency in the range of 0.03 MHz <  $f_{bus}$  < 20 MHz, good clock accuracy, and medium/high cost (because a crystal, resonator, or external clock is required).

The bus frequency that will be generated is calculated with the following formula:

$f_{bus} = (f_{ext} \times P \times N \div R) \div 2$

Where  $f_{ext}$  is the frequency of the external reference (in this example we assume a 32.768 kHz crystal is being used). P depends on the value of the RANGE bit, because we are using a crystal in the low-frequency range P = 64 (if RANGE = 1 then P = 1). N and R are the multiplication and division factors determined by bits MFD and RFD in ICGC2.

In our example, we will program N/R = 4, therefore  $f_{bus}$  will be: 4.19 MHz. The ICG control registers will be programmed in the following way:

| ICGC1    | ICGC1   |    |                                                                            |  |  |

|----------|---------|----|----------------------------------------------------------------------------|--|--|

| Bit 7    | HGO*    | 0  | Configures oscillator for low power operation                              |  |  |

| Bit 6    | RANGE   | 0  | Configures oscillator for low frequency range (FLL prescale factor P = 64) |  |  |

| Bit 5    | REFS    | 1  | Oscillator using crystal or resonator is requested                         |  |  |

| Bits 4:3 | CLKS    | 11 | FLL Engaged External mode requested                                        |  |  |

| Bit 2    | OSCSTEN | 0  | Oscillator disabled in STOP mode                                           |  |  |

| Bit 1    | LOCD*   | 0  | Loss of clock detection enabled                                            |  |  |

| Bit 0    |         | 0  | Unimplemented or reserved                                                  |  |  |

#### Table 1. ICG Control Register Settings for FEE Mode

\*Only available in MC9S08AW, for MC9S08GB/GT always write zero

| ICGC2    | ICGC2 |     |                                                 |  |  |

|----------|-------|-----|-------------------------------------------------|--|--|

| Bit 7    | LOLRE | 0   | Generates an interrupt request on loss of lock  |  |  |

| Bits 6:4 | MFD   | 000 | Sets the MFD multiplication factor to 4 (N)     |  |  |

| Bit 3    | LOCRE | 0   | Generates an interrupt request on loss of clock |  |  |

| Bits 2:0 | RFD   | 000 | Sets the RFD division factor to 1 (R)           |  |  |

The following piece of code in C would set this configuration:

#### NOTE

The while loop is used to pause execution until the FLL has locked. For time critical tasks an additional while loop could be included to wait for DCOS = 1.

### 2.2 FLL Engaged Internal Example

This time, we will configure the microcontroller to work in FLL engaged internal (FEI) mode. The reference used will be the internal 243 kHz reference clock. This mode allows for a bus frequency in the range 0.03 MHz <  $f_{bus}$  < 20 MHz, medium clock accuracy (if IRG has been trimmed), and the lowest cost (because it requires no external components).

The bus frequency that will be generated is calculated with the following formula:

$f_{bus} = ((f_{IRG} \div 7) \times P \times N/R) \div 2$

Where  $f_{IRG}$  is the frequency of the internal reference generator (approximately 243 kHz). In this mode the FLL prescale factor P is always 64. N and R are the multiplication and division factors determined by bits MFD and RFD in register ICGC2.

We will program N/R = 2, therefore  $f_{bus}$  will be: 2.221 MHz.

The ICG control registers will be programmed in the following way:

| ICGC1    |         |    |                                                                  |

|----------|---------|----|------------------------------------------------------------------|

| Bit 7    | HGO*    | 0  | Configures oscillator for low power operation; (don't care)      |

| Bit 6    | RANGE   | 0  | Configures oscillator for low frequency range; (don't care)      |

| Bit 5    | REFS    | 1  | Oscillator using crystal or resonator is requested; (don't care) |

| Bits 4:3 | CLKS    | 01 | FLL engaged internal mode requested                              |

| Bit 2    | OSCSTEN | 0  | Oscillator disabled in stop mode                                 |

| Bit 1    | LOCD*   | 0  | Loss of clock detection enabled                                  |

| Bit 0    |         | 0  | Unimplemented or reserved                                        |

#### Table 2. ICG Control Register Settings for FEI Mode

\*Only available in some MCUs, for other devices, always write zero (see the data sheet for your device)

| ICGC2    |       |     |                                                 |

|----------|-------|-----|-------------------------------------------------|

| Bit 7    | LOLRE | 0   | Generates an interrupt request on loss of lock  |

| Bits 6:4 | MFD   | 000 | Sets the MFD multiplication factor to 4 (N)     |

| Bit 3    | LOCRE | 0   | Generates an interrupt request on loss of clock |

| Bits 2:0 | RFD   | 001 | Sets the RFD division factor to 2 (R)           |

The following piece of code in C would set this configuration:

#### NOTE

The while loop is used to pause execution until the FLL has locked. For time critical tasks an additional while loop could be included to wait for DCOS = 1.

### 2.3 FLL Bypassed External Example

Now we will configure the microcontroller to work in FLL bypassed external (FBE) mode using a 32 kHz crystal as a reference. This mode allows for a bus frequency <= 8 MHz (up to 20 MHz if using external oscillator), highest clock accuracy, lowest power consumption, and medium/high cost (because crystal, resonator, or external clock is required).

The bus frequency that will be generated is calculated with the following formula:

$f_{bus} = (f_{ext} \times 1/R) \div 2$

Where  $f_{ext}$  is the frequency of the external reference (in this example we assume a 32,768 kHz crystal is being used).

In our example f<sub>bus</sub> will be: 16.384 kHz.

The ICG control registers will be programmed in the following way:

| ICGC1    |         |    |                                                                               |

|----------|---------|----|-------------------------------------------------------------------------------|

| Bit 7    | HGO*    | 0  | Configures oscillator for low power operation                                 |

| Bit 6    | RANGE   | 0  | Configures oscillator for low frequency range (FLL prescale factor $P = 64$ ) |

| Bit 5    | REFS    | 1  | Oscillator using crystal or resonator is requested                            |

| Bits 4:3 | CLKS    | 10 | FLL Bypass External mode requested                                            |

| Bit 2    | OSCSTEN | 0  | Oscillator disabled in STOP mode                                              |

| Bit 1    | LOCD*   | 0  | Loss of clock detection enabled                                               |

| Bit 0    |         | 0  | Unimplemented or reserved                                                     |

#### Table 3. ICG Control Register Settings for FBE Mode

\*Only available in some MCUs; for others, always write zero (refer to the data sheet for your device).

| ICGC2    |       |     |                                                             |

|----------|-------|-----|-------------------------------------------------------------|

| Bit 7    | LOLRE | 0   | Generates an interrupt request on loss of lock (don't care) |

| Bits 6:4 | MFD   | 000 | Sets the MFD multiplication factor to 4 (N); (don't cares)  |

| Bit 3    | LOCRE | 0   | Generates an interrupt request on loss of clock             |

| Bits 2:0 | RFD   | 000 | Sets the RFD division factor to 1 (R)                       |

The following piece of code in C would set this configuration:

ICGC2=0x00; ICGC1=0x30; while (ICGS1\_ERCS==0);

#### NOTE

The while loop is used to pause execution until the external reference clock is stable and meets the minimum frequency requirement.

### 2.4 Self-Clocked Mode Example

In this example we will use the microcontroller in self-clocked mode (SCM). This is the default mode of operation for the ICG module. When this mode is entered out of reset, the bus frequency will default to approximately 4 MHz.

This is the only mode in which the filter registers (ICGFLT) can be written. The default value of the ICGFLT registers is 0x0C0. Writing a higher value will increase the bus frequency, while a lower value will decrease the bus frequency.

This mode allows for a bus frequency in the range 3  $MHz < f_{bus} < 20 MHz$  (via filter bits), quick and reliable system startup, and poor accuracy.

In our example  $f_{bus}$  will be around 20 MHz.

To operate in SCM no register needs to be written, however in this example we will write ICGFLTU and ICGFLTL to increase the bus frequency (by writing ICGFLT we modify ICGFLTL and the four least significant bits of ICGFLTU. The other four bits are unimplemented).

The following piece of code in C would modify the FLT registers:

ICGFLT=0x0800;

The bus frequency could be reduced by changing the RFD division factor in the ICGC2 register.

### 3 Tips and Recommendations

- Be careful when writing to the ICGC1 register because bits RANGE and REFS are write-once after reset. Also, if the first write after reset sets CLKS = 0x (SCM, FEI) the CLKS bits cannot be written to 1x (FEE, FBE) until after the next reset (because the EXTAL pin was not reserved).

- For minimum power consumption and minimum jitter, choose N and R to be as small as possible when operating in FEE or FEI modes.

- When operating in FEE mode and using a crystal or resonator, make sure its frequency is in the specified range of 32 kHz 100 kHz for RANGE = 0, or 2 MHz 10 MHz for RANGE = 1.

- When operating in FBE mode and using a crystal or resonator, make sure its frequency is in the specified range of 32 kHz 100 kHz for RANGE = 0, or 1 MHz 16 MHz for RANGE = 1.

- The oscillator can be configured to provide a higher amplitude output for noise immunity. This mode of operation is selected by HGO = 1 (only available on some MCUs see the data sheet for your device).

#### **Tips and Recommendations**

- To avoid long oscillator startup times when exiting stop mode, you can program OSCSTEN = 1, this way the oscillator will remain enabled in stop mode (ICG in off mode). The disadvantage is higher current consumption in STOP mode.

- When operating in FEI, trim the internal reference generator. Increasing the value in the ICGTRM register will increase the period and decreasing the value will decrease the period. For a detailed explanation of the trim procedure, please refer to application note AN2496.

- Two very useful bits are LOLRE and LOCRE. They configure whether a reset or an interrupt will be generated in the events of a loss of lock (LOLRE) and of a loss of clock (LOCRE).

- When using an XTAL (crystal) be sure to use high-quality components (XTAL, resistors, and capacitors). Use low inductance resistors such as carbon-composition resistors. Capacitors should be high-quality ceramic capacitors specifically designed for high-frequency applications. If using a resonator, be sure to use a high quality resonator.

- For the values of the components used with the XTAL or resonator, consult the manufacturer or the device's data sheet (typical values are: C1 and C2 in the range of 5 pF to 25 pF,  $R_F$  in the range 1 10 MQ,  $R_S$  in the range of 0 10 kQ). Take into consideration stray capacitance when sizing C1 and C2.

- Good layout practices are fundamental for correct operation and reliability of the oscillator (crystal or resonator). Try to have the oscillator's components very near to the XTAL and EXTAL pins to minimize the length of the routing traces. Avoid high-frequency/current signals near the oscillator to prevent crosstalk and to minimize noise, etc.

- Freescale recommends an evaluation of the application board and chosen resonator or crystal by the resonator or crystal manufacturer.

- We recommend writing to ICGC2 before ICGC1. This sets the multiplier before enabling the FLL.

#### NOTE

This code was developed using the CodeWarrior Development Studio for HC(S)08 version 5.0 using Device Initialization.

### **Freescale Semiconductor**

**Users Guide**

# Programming the Low-Power Modes on HCS08 Microcontrollers

by: Gabriel Sanchez Barba Gonzalo Delgado RTAC Americas México 2005

# 1 Overview

This is a quick reference for using the low-power modes on an HCS08 microcontroller (MCU). Basic information about the functional description and configuration options is provided. The following examples may be modified to suit your application — refer to the data sheet for your device.

Freescale's HCS08 microcontrollers include several stop modes that permit the user to achieve low power consumption. This provides great flexibility and may be used to provide ideal conditions for many different types of applications. The HCS08 MCUs support three<sup>1</sup> different stop modes that may be entered when a stop instruction is executed if the STOPE bit in the system option register is set. If the STOPE bit is not set, then an illegal opcode reset will be forced.

#### **Table of Contents**

| 1 | Ove  | erview                                      |

|---|------|---------------------------------------------|

| 2 | Coo  | de Example and Explanation                  |

|   | 2.1  | Important I/O Configuration Information 30  |

| 3 | In-E | Depth Reference Material                    |

|   | 3.1  | Stop3 Overview (PDC = 0, PPDC = 1 or 0). 31 |

|   | 3.2  | Stop2 Overview (PDC = 1, PPDC = 1) 31       |

|   | 3.3  | Stop1 Overview (PDC = 1, PPDC = 0) 31       |

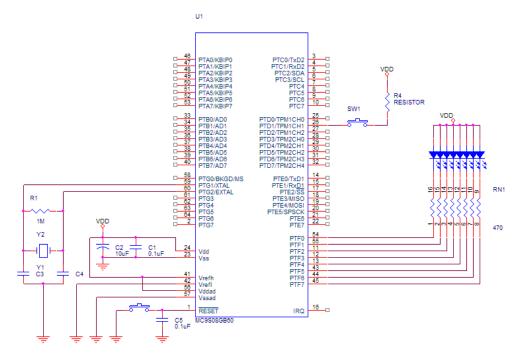

| 4 | Hai  | dware Implementation                        |

semiconductor

1. Not all stop modes are available on all devices. Refer to the data sheet for your device.

#### Low Power Modes Quick Reference

The stop modes function uses device dependent registers. Please see the data sheet for your device to check availability / location for these bits. For example, on some devices, the low voltage warning bits are moved to another register (SPMSC3), and there is a PDF (power-down flag) in bit 4 of SPMSC2.

| SOPT                                           | COPE            | COPT                                                      | STOPE      |             |              | 1                                                                                                                                          |     | 1    |   |

|------------------------------------------------|-----------------|-----------------------------------------------------------|------------|-------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|------|---|

|                                                | STOPE -         | - enables                                                 | the stop m | odes        |              |                                                                                                                                            |     |      | • |

| SPMSC2                                         | LVWF            | LVWACK                                                    | LVDV       | LVWV        | PPDF         | PPDACK                                                                                                                                     | PDC | PPDC |   |

|                                                | System p        | ower mana                                                 | agement st | atus and co | ontrol regis | ster 2                                                                                                                                     |     |      |   |

|                                                | LVWAC<br>LVDV — | – flags low<br>K — clears<br>-selects be<br>ct trip point | the low vo | ltage warn  | PPD/<br>PDC  | PPDF — partial power-down flag<br>PPDACK — partial power-down acknowledge<br>PDC — power-down control<br>PPDC — partial power-down control |     |      |   |

| LVWV — selects between high or low low-voltage |                 |                                                           |            |             |              |                                                                                                                                            |     |      |   |

|                                                |                 |                                                           |            |             |              |                                                                                                                                            |     |      |   |

This example code is available inside the CodeWarrior project or from the Freescale Web site in HCS08QRUGSW.zip.

It contains the following functions:

- main Checks for a stop2 recovery, and if so, enters stop1, otherwise, it enters stop3 and waits for an external interrupt. After it receives an external interrupt, it services the interrupt routine, and returns to the main loop where it enters stop2 and waits for another external interrupt. When this interrupt occurs, the MCU will go through reset and see that it came out of stop2 and so configures and enters itself into stop1.

- MCU\_init Configures MCU hardware, as well as the external interrupt.

- Delay This is a simple loop routine.

- Virq\_isr Services the IRQ pin interrupt.

Following these four simple steps, the user can enter any of the stop modes available on the device:

1. Set the STOPE bit in SOPT to enable stop modes:

This will enable stop instructions, otherwise, an illegal opcode reset will be forced.

- Set up the SPMSC1 register: This register sets up low-voltage detect. Low-voltage detect must be disabled to be able to enter stop2 and stop1.

- 3. Set up all interrupts that will exit the MCU from stop mode.

This is needed so that the MCU may successfully exit stop modes by other means than just reset.

Check and set up SPMSC2 register. There are two main purposes to this: (a) check partial power down flag, and (b) set up stop mode to be used.

After these steps have been done, you may enter the stop modes in the MCU by executing a stop instruction.

### 2.1 Important I/O Configuration Information

When the HCS08 goes into stop2 or stop3 mode, the content of its registers remain unchanged. In particular, the ports keep their configuration. So, it is important to set the ports in a state that may not lead to a current consumption increase at the application level. Software and hardware engineers should follow these guidelines in order to avoid additional current consumption:

- Do not leave any I/O configured as an unconnected inputs instead, tie them to  $V_{DD}$  or  $V_{SS}$ . Or, you can set unconnected I/O as output, thus forcing a steady level.

- The same recommendation applies to unbonded I/O on small packages (on the package QFP44 vs. LQFP64 for instance). In this case, set the unbonded I/O as output.

- For inputs whose logic state is uncertain (for a Hall-effect sensor signal, for instance), use external pullup or pulldown resistors instead of the internal ones that are weak (typically between 20 k $\Omega$  and 50 k $\Omega$ ). This way, the power consumption is minimized in case the level of these inputs changes during the low-power mode.

#### Programming the Low-Power Modes on HCS08 Microcontrollers

In-Depth Reference Material

## 3 In-Depth Reference Material