#### M68MPFB1632/D

June 1994

# M68MPFB1632 MODULAR PLATFORM BOARD

# **USER'S MANUAL**

© MOTOROLA, INC., 1993, 1994; All Rights Reserved

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death alleges that Motorola was negligent regarding the design or manufacture of the part.

The M68ICD16 In-Circuit Debugger with IASM16 development software and M68ICD32 In-Circuit Debugger with IASM32 development software are © P & E Microcomputer Systems, Inc.\*, 1990, 1992; All Rights Reserved. Portions of the software are © Borland International, 1987, 1993. Portions of the software are © TurboPower Software, 1988, 1993.

\* P & E Microcomputer Systems, Inc., PO Box 2044

Woburn, MA 01888-2044

(617)-353-9206

# **TABLE OF CONTENTS**

#### **CHAPTER 1 GENERAL INFORMATION**

| 1.1 | Introduction        | 1-1 |

|-----|---------------------|-----|

| 1.2 | Features            | 1-1 |

| 1.3 | Specifications      | 1-2 |

|     | General Description |     |

|     | Equipment Required  |     |

#### **CHAPTER 2 HARDWARE PREPARATION AND INSTALLATION**

| 2.1 Introduction                              | 1 |

|-----------------------------------------------|---|

| 2.2 Hardware Preparation                      | 1 |

| 2.2.1 J10, J11 +5 Volt Select Header (W9) 2-7 | 7 |

| 2.2.2 Voltage Standby Select Header (W15)2-7  | 7 |

| 2.2.3 MODCLK Select Header (W16)              | 3 |

| 2.2.4 BERR Select Header (W17)                | 3 |

| 2.2.5 J13 +5 Volt Select Header (W21)         | 9 |

| 2.2.6 MCU Type Select Header (W22)            | 9 |

| 2.2.7 MPFB LED Descriptions                   | ) |

| 2.2.8 DS2 Control Insertion Point (E1)        | ) |

| 2.3 Installation Instructions                 | ) |

| 2.3.1 Power Supply – MPFB Connection          | ) |

| 2.3.2 Personal Computer – BDM Connection (J6) | 2 |

| 2.3.3 RESET Switch (S2)                       | 3 |

| 2.3.4 Logic Analyzer Connections (J7 – J20)   | 3 |

| 2.4 Starting Evaluation Activities            |   |

#### **CHAPTER 3 MEMORY CONFIGURATION**

| 3.1 | Introducti  | on                                         |      |

|-----|-------------|--------------------------------------------|------|

| 3.2 | Memory (    | Configuration                              |      |

|     | 3.2.1 Data  | RAM Configuration (U1 and U3)              |      |

|     | 3.2.1.1     | Data RAM Memory Size Select Header (W1)    |      |

|     | 3.2.1.2     | Data RAM Write Enable Select Header (W7)   |      |

|     | 3.2.1.3     | Data RAM Output Enable Select Header (W8)  |      |

|     | 3.2.1.4     | Data RAM Write Enable Select Header (W11)  |      |

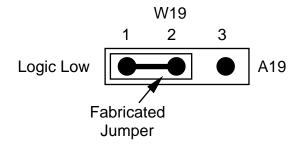

|     | 3.2.1.5     | A19 Disconnect Select Header (W19)         |      |

|     | 3.2.2 Pseud | lo ROM Configuration (U2 and U4)           |      |

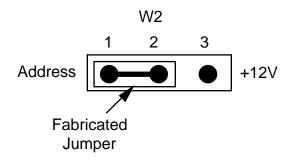

|     | 3.2.2.1     | Pseudo ROM Pin 1 Select Header (W2)        |      |

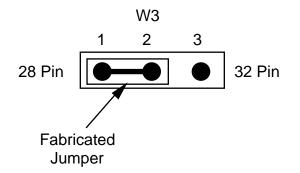

|     | 3.2.2.2     | Pseudo ROM Package Size Select Header (W3) | 3-13 |

|     |             |                                            |      |

#### CHAPTER 3 MEMORY CONFIGURATION (continued)

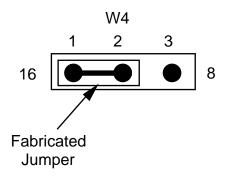

| 3.2.2.3      | Pseudo ROM Port Size Select Header (W4)         | 3-14 |

|--------------|-------------------------------------------------|------|

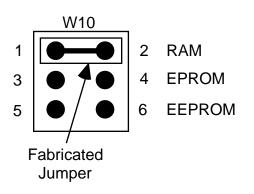

| 3.2.2.4      | Pseudo ROM Memory Type Select Header (W10)      | 3-14 |

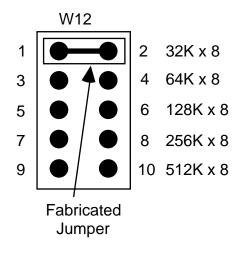

| 3.2.2.5      | Pseudo ROM Memory Size Select Header (W12)      | 3-15 |

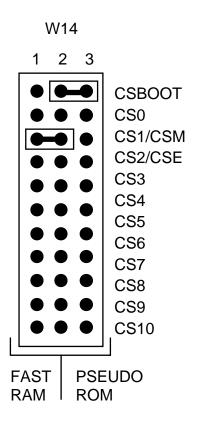

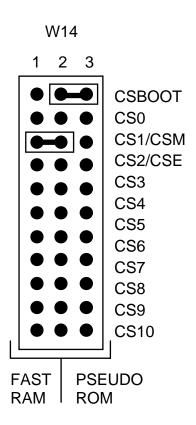

| 3.2.2.6      | Pseudo ROM Chip Select Header (W14)             | 3-16 |

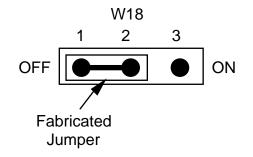

| 3.2.2.7      | Pseudo ROM Write Protection Select Header (W18) | 3-17 |

| 3.2.2.8      | A19 Disconnect Select Header (W19)              | 3-18 |

| 3.2.3 Fast F | RAM Configuration (U9 and U10)                  | 3-19 |

| 3.2.3.1      | Fast RAM Chip Select Header (W14)               | 3-21 |

| 3.2.4 MPFF   | 3 Memory Devices                                | 3-22 |

|              |                                                 |      |

#### CHAPTER 4 RS-232 I/O PORT CONFIGURATION

| 4.1 Introduction                                 | 4-1  |

|--------------------------------------------------|------|

| 4.2 Jumper Header and I/O Port Configuration     |      |

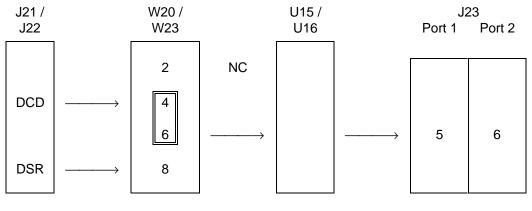

| 4.2.1 RS-232 Port 1 Protocol Select Header (W20) |      |

| 4.2.2 RS-232 Port 2 Protocol Select Header (W23) |      |

| 4.2.3 RS-232 Port Connections (J21, J22)         |      |

| 4.2.4 Serial Data Wire-Wrap Connection (J23)     |      |

| 4.3 Advanced RS-232 Configuration                | 4-10 |

#### **CHAPTER 5 EEPROM PROGRAMMING**

| 5.1 | Introduction                                  | 5-1 |

|-----|-----------------------------------------------|-----|

| 5.2 | MPFB Power Circuit Overview                   | 5-1 |

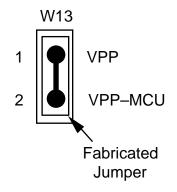

| 5   | .2.1 VPP-MCU Select Header (W13)              | 5-2 |

|     | .2.2 Flash EEPROM Voltage Control Switch (S1) |     |

| 5   | .2.3 VPP Insertion Point (E2)                 | 5-3 |

#### **CHAPTER 6 PORT REPLACEMENT UNIT OPERATION**

| 6.1 | Introduction                             | 6-1 |

|-----|------------------------------------------|-----|

| 6.2 | Using an MCU with SIM                    | 6-1 |

| 6.3 | Using an MCU with SCIM                   | 6-1 |

| 6.4 | Jumper Header Configuration              | 6-2 |

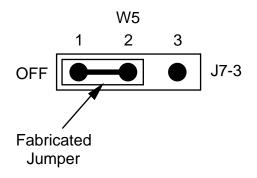

| 6   | 5.4.1 PRU OEALL Select Header (W5)       | 6-2 |

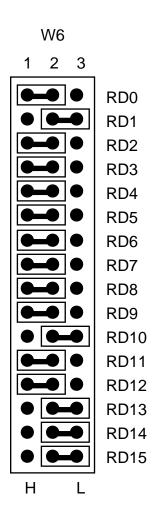

| 6   | 5.4.2 PRU Reset Data Control Header (W6) | 6-3 |

|     |                                          |     |

#### **CHAPTER 7 SUPPORT INFORMATION**

| 7.1 | Introduction                  | 7- | 1 |

|-----|-------------------------------|----|---|

| 7.2 | Connector Signal Descriptions | 7- | 1 |

# LIST OF FIGURES

| <b>T</b> 2: | ~  |    |

|-------------|----|----|

| <b>C</b> 1  | УH | ге |

|             | ວຕ |    |

| 2-1 | MPFB Jumper Header, Connector, and Switch Location Diagram |     |

|-----|------------------------------------------------------------|-----|

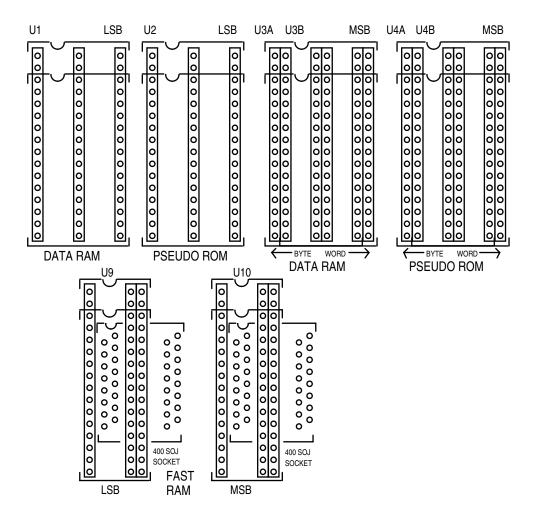

| 3-1 | Memory Socket Diagram                                      |     |

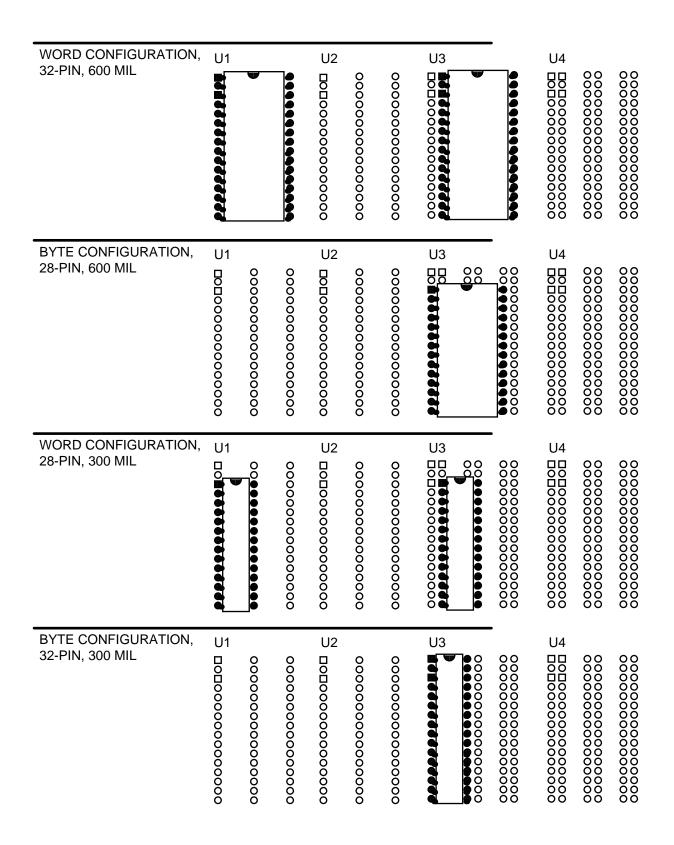

| 3-2 | Data RAM Device Configuration                              |     |

| 3-3 | Pseudo ROM Device Configuration                            |     |

| 3-4 | Fast RAM Device Configuration                              |     |

| 3-5 | MPFB Supported RAM Devices                                 |     |

| 3-6 | MPFB Supported EPROM Devices                               |     |

| 3-7 | MPFB Supported EEPROM Devices                              |     |

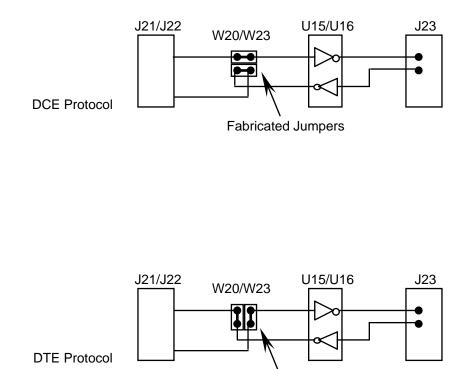

| 4-1 | DCE/DTE Protocol Wiring Diagrams                           |     |

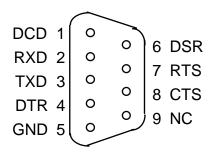

| 4-2 | RS-232 Port Connector J21 (Port 1)                         |     |

| 4-3 | RS-232 Port Connector J22 (Port 2)                         |     |

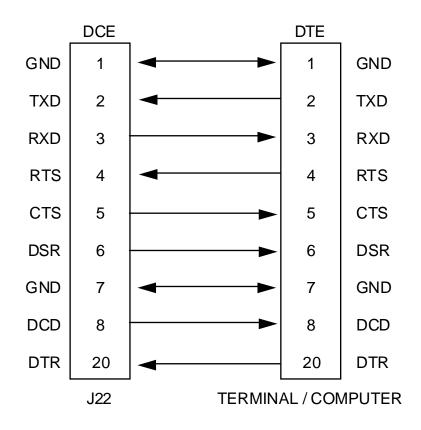

| 4-4 | RS-232 Cable Assembly (Optional)                           | 4-7 |

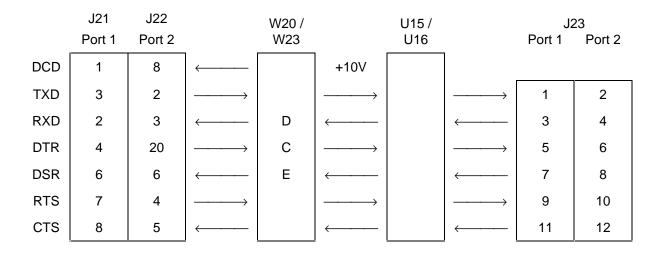

| 4-5 | J23 Port Connections for DCE Operation                     |     |

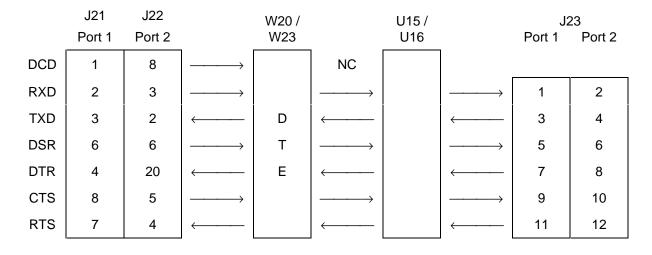

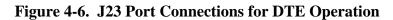

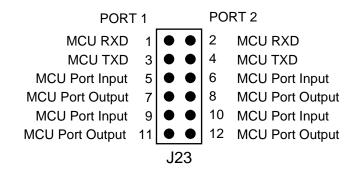

| 4-6 | J23 Port Connections for DTE Operation                     | 4-9 |

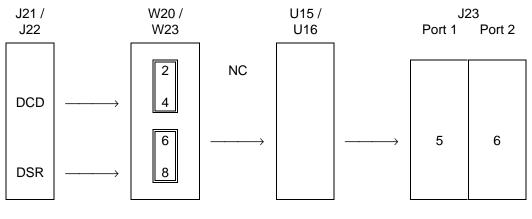

| 4-7 | DCD/DSR Selection Using a DTE Port                         |     |

|     |                                                            |     |

# LIST OF TABLES

# Table

| 1-1  | MEVB Specifications                          | 1-2  |

|------|----------------------------------------------|------|

| 2-1  | Jumper Header Types                          | 2-3  |

| 2-2  | MPFB Jumper Header Descriptions              | 2-3  |

| 3-1  | Valid MPFB U1, U3 Memory Configurations      | 3-6  |

| 3-2  | W4 Pseudo ROM Port Size Configuration        | 3-10 |

| 7-1  | Input Power Connector J5 Pin Assignments     | 7-2  |

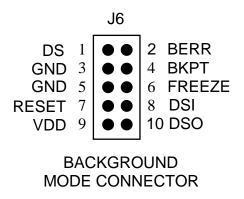

| 7-2  | Computer – BDM Connector J6 Pin Assignments  |      |

| 7-3  | Logic Analyzer Connector J7 Pin Assignments  | 7-3  |

| 7-4  | Logic Analyzer Connector J8 Pin Assignments  | 7-3  |

| 7-5  | Logic Analyzer Connector J9 Pin Assignments  | 7-3  |

| 7-6  | Logic Analyzer Connector J10 Pin Assignments | 7-4  |

| 7-7  | Logic Analyzer Connector J11 Pin Assignments | 7-4  |

| 7-8  | Logic Analyzer Connector J12 Pin Assignments | 7-5  |

| 7-9  | Logic Analyzer Connector J13 Pin Assignments | 7-7  |

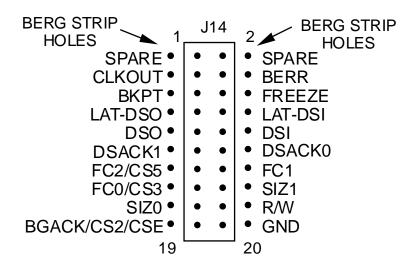

| 7-10 | Logic Analyzer Connector J14 Pin Assignments | 7-8  |

| 7-11 | Logic Analyzer Connector J15 Pin Assignments | 7-9  |

|      | Logic Analyzer Connector J16 Pin Assignments |      |

| 7-13 | Logic Analyzer Connector J17 Pin Assignments | 7-9  |

|      |                                              |      |

Page

# LIST OF TABLES (continued)

| Table                                                     | Page |

|-----------------------------------------------------------|------|

| 7-14 Logic Analyzer Connector J18 Pin Assignments7        | 7-10 |

| 7-15 Logic Analyzer Connector J19 Pin Assignments7        | 7-10 |

| 7-16 Logic Analyzer Connector J20 Pin Assignments7        | 7-10 |

| 7-17 RS-232 Evaluation Port Connector J21 Pin Assignments | 7-11 |

| 7-18 RS-232 Evaluation Port Connector J22 Pin Assignments | 7-11 |

| 7-19 Serial Data Wire-Wrap Connector J23 Pin Assignments7 | 7-12 |

# **CHAPTER 1**

## **GENERAL INFORMATION**

# **1.1 INTRODUCTION**

This manual provides general information, hardware preparation, installation instructions, and support information for the M68MPFB1632 Modular Platform Board (MPFB). The MPFB is part of Motorola's modular approach to microcontroller unit-based product development. This modular approach lets you easily configure our development systems to fit your requirements.

The MPFB is one component of the M68MEVB1632 Modular Evaluation Board (MEVB). The MEVB consists of the M68MPFB1632 Platform Board, a microcontroller unit personality board (MPB), and either the In-Circuit Debugger 16 (ICD16) or In-Circuit Debugger 32 (ICD32) hardware assembly and development software. The development software is from P&E Microcomputer Systems. For MEVB operating instructions when evaluating an M68HC16 MCU device, see the ICD16 In-Circuit Debugger User's Manual, M68ICD16/D. For MEVB operating instructions when evaluating an M68300 MCU device, see the ICD32 In-Circuit Debugger User's Manual, M68ICD32/D.

The MPFB only operates with MPBs that support system integration module (SIM) or single-chip integration module (SCIM) MCUs.

# **1.2 FEATURES**

MPFB features include:

- A platform which provides interface and power connections for the MPB.

- On-board support for multiple memory devices, types (RAM, EPROM, and flash EEPROM), and sizes (32 kilobytes to 512 kilobytes).

- Two RS-232C terminal input/output (I/O) ports for user evaluation of the serial communication interface (SCI).

- Logic analyzer pod connectors (for all MCU pins).

- Port replacement unit (PRU) to rebuild I/O ports lost to address/data/control.

- On-board VPP (+12Vdc) generation for MCU and flash EEPROM programming.

- On-board wire-wrap area.

- Development software:

- ICD16/ICD32 user interface for the MEVB debugger

- PROG16/PROG32 programmer for M68HC16 and M68300 family MCUs

- IASM integrated assembler/editor

# **1.3 SPECIFICATIONS**

Table 1-1 lists MPFB specifications.

| CHARACTERISTIC                                  | SPECIFICATIONS                                                                                             |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Data RAM maximum memory<br>(locations U1, U3)   | RAM:<br>32 K, 128 K, or 512 K x 16 (word mode)<br>32 K, 128 K, or 512 K x 8 (byte mode)                    |

| Pseudo ROM maximum memory<br>(locations U2, U4) | RAM:<br>32 K, 128 K, or 512 K x 16 (word mode)<br>32 K, 128 K, or 512 K x 8 (byte mode)<br>EPROM & EEPROM: |

|                                                 | 32 K, 64 K, 128 K, 256 K, or 512 K x 16 (word mode)<br>32 K, 64 K, 128 K, 256 K, or 512 K x 8 (byte mode)  |

| Fast RAM maximum memory<br>(locations U9, U10)  | RAM:<br>32 K or 128 K x 16 (word mode only)                                                                |

| MCU I/O ports                                   | HCMOS compatible                                                                                           |

| Monitor interface                               | PC parallel (printer) port to BDM connector (J6) via ICD16/32. Refer to the ICD16/32 User's Manual.        |

| Optional development interface                  | RS-232C compatible (two connectors)                                                                        |

| Temperature<br>Operating<br>Storage             | -10° to +50° C<br>-40° to +85° C                                                                           |

| Relative humidity                               | 0 to 90% (non-condensing)                                                                                  |

| Power requirements                              | +5Vdc (±10%) @ 1.0 A (max.) – fuse protected @ 1.5<br>Amps                                                 |

| VPP                                             | +12Vdc (±5%) @ 0.50 mA (max.) – current limiting circuit                                                   |

| Dimensions<br>Modular Platform Board            | 8.5 x 11 in. (216 x 279 mm)                                                                                |

### **Table 1-1. MEVB Specifications**

# **1.4 GENERAL DESCRIPTION**

The MPFB and MPB together form the MEVB. The MEVB is an economical tool for designing, debugging, and evaluating MCU operation of the MC68HC16 and MC68300 MCU Families. By providing the essential MCU timing and I/O circuitry, the MEVB simplifies user evaluation of prototype hardware/software products. The MEVB requires a user-supplied power supply and host computer.

For communication with the MEVB, you need a personal computer with a parallel port; MEVB development software uses the parallel port for communications. The MEVB also has two RS-232 serial ports, which let you evaluate the on-chip serial communication interface (SCI). (These serial ports are available to you at all times; the ICD16 and ICD32 development system monitor interface does not require these ports.)

The MEVB debugger (ICD) operates in background mode (BDM); a backdoor method of talking to the CPU core. You may also use any debugger which interfaces via the standard 10-pin BDM.

There are two methods of generating MCU code:

- 1. Using the MEVB one-line assembler/disassembler.

- 2. Assembly code with IASM and download assembled code from an external source to MEVB RAM or MCU RAM via ICD16 or ICD32 through the background mode port.

#### NOTE

You may use any assembler that has S-record or MAP file capabilities.

The MPFB includes jumper-selectable options such as chip select usage, memory type selection and memory size selection for the pseudo ROM sockets, and reset data control. The MPFB offers various operating configurations for byte-wide or word-wide memory sizing. The MEVB allows programming of internal-MCU flash EEPROM as well as external EEPROM devices. To reset MEVB circuitry, you may use the on-board reset switch or the software RESET command.

#### NOTE

The MPFB must be configured for the specific MPB. For a detailed description of the MPB jumper header selections refer to the specific MPB user's manual.

# **1.5 EQUIPMENT REQUIRED**

The external requirements for MPFB operation are a +5Vdc ( $\pm 10\%$ ) power supply. When using the supplied ICD16 or ICD32 development software, an MS-DOS compatible computer and interface cable are required. For ICD16 or ICD32 computer and interface cable requirements refer to the ICD16 In-Circuit Debugger User's Manual, M68ICD16/D or the ICD32 In-Circuit Debugger User's Manual, M68ICD32/D.

# CHAPTER 2

# HARDWARE PREPARATION AND INSTALLATION

# 2.1 INTRODUCTION

This chapter provides unpacking instructions, hardware preparation information, and installation instructions for the MPFB.

When you unpack the MPFB from its shipping carton, verify that all items are in good condition. Save packing material for storing and shipping the MPFB.

#### NOTE

Should the product arrive damaged, save all packing material, and contact the carrier's agent.

# 2.2 HARDWARE PREPARATION

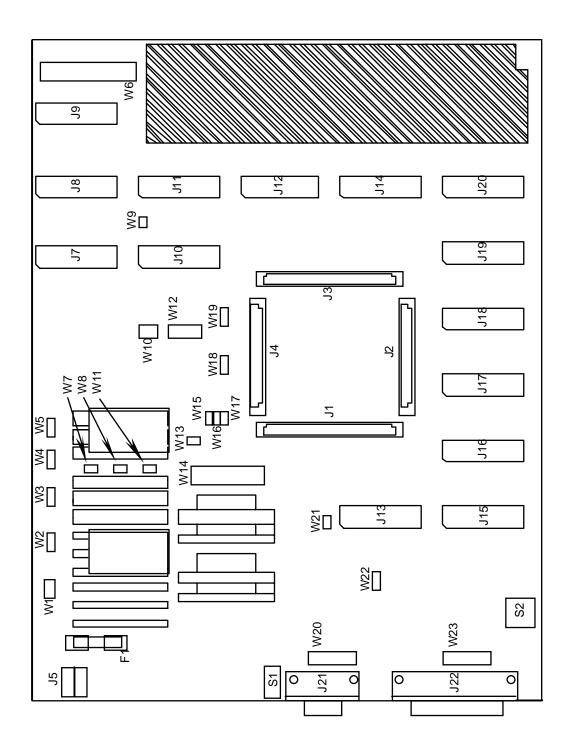

This portion of the manual explains how to prepare the MPFB before use, as well as how to configure the MPFB for system operation. Consult either the ICD16 or ICD32 manual as part of your system hookup. Refer to Chapter 3 for installing or configuring memory in the on-board sockets at locations U1 through U4, U9, and U10. Refer to Chapter 4 for RS-232 I/O port configuration. Refer to Chapter 5 for EEPROM programming. Refer to Chapter 6 for PRU operation. Refer to Chapter 7 for support information. Figure 2-1 shows the locations of memory sockets, jumper headers, connectors, light emitting diodes (LEDs), and switches.

Table 2-1 is a general explanation of the jumper header types found on the MPFB. Table 2-2 lists the MPFB jumper headers and a description of the function in each position. Refer to paragraphs 2.2.1 through 2.2.6 for a more complete definition of the jumper headers for general MPFB configuration. Refer to the specific chapter for details on other MPFB jumper headers.

Figure 2-1. MPFB Jumper Header, Connector, and Switch Location Diagram

| Jumper Header<br>Type | Symbol                    | Description                                                                                                                                                                          |  |

|-----------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| two-pin               | •                         | Two-pin jumper header and designated as WX (X = the jumper header number). Use a fabricated jumper to create a short between the two pins of the jumper header.                      |  |

| two-pin with jumper   |                           | Two-pin jumper header with jumper, designated as WX (X = the jumper header number).                                                                                                  |  |

| three-pin             | $\bullet \bullet \bullet$ | Three-pin jumper header, designated as WX (X = the jumper header number). Use a fabricated jumper to create a short between two of the three pins of the jumper header.              |  |

| three-pin with jumper |                           | Three-pin jumper header with jumper and designated as WX (X = the jumper header number). To change the factory jumper header configuration, move the jumper to the two desired pins. |  |

Table 2-1. Jumper Header Types

| Jumper<br>Header          | Туре       | Description                                                                                                                                                |

|---------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

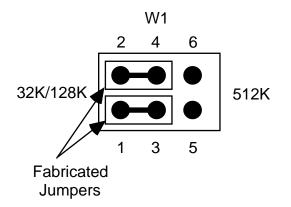

| W1<br>Data RAM            | 246        | Jumper between pins 1 and 3 and 2 and 4 (factory default); 32K x 8 or 128Kx 8 RAMs installed in the data RAM sockets (U1 & U3).                            |

| Size                      | 135        | Jumper between pins 3 and 5 and 4 and 6; $512K \times 8$ RAMs installed in the data RAM sockets (U1 & U3).                                                 |

| W2<br>Pseudo ROM<br>Pin 1 | 123<br>••• | Jumper installed on pins 1 and 2 (factory default); configures pin 1 of the memory devices in the pseudo ROM sockets (U2 & U4) as a standard address line. |

| Selection                 |            | Jumper installed on pins 2 and 3; connects +12Vdc (VPP) to pin 1 of the pseudo ROM sockets and lets you program flash EEPROM memory devices.               |

| W3<br>Pseudo ROM          | 123<br>••• | Jumper installed on pins 1 and 2 (factory default); 28-pin memory devices in the pseudo ROM sockets (U2 & U4).                                             |

| Package Size              |            | Jumper installed on pins 2 and 3; 32-pin memory devices in the pseudo ROM sockets.                                                                         |

| W4<br>Pseudo ROM          | 123<br>••• | Jumper installed on pins 1 and 2 (factory default); pseudo ROM port size (memory data width) is word.                                                      |

| Port Size                 |            | Jumper installed on pins 2 and 3; pseudo ROM port size is byte.                                                                                            |

| W5                        | 123        | Jumper installed on pins 1 and 2 (factory default); disables the PRU.                                                                                      |

| PRU OE(ALL)<br>Selection  |            | Jumper installed on pins 2 and 3; user enables/disables the PRU by controlling OE(ALL) from logic analyzer connector J7.                                   |

| Jumper<br>Header                | Туре                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|---------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| W6<br>PRU Reset<br>Data Control | 123<br>••••<br>••••<br>••••<br>••••<br>••••<br>•••<br>• | W6 selects the MCU operation mode. Each 3-pin jumper header set<br>corresponds to an MCU data line. While the reset pin is low, the reset dat<br>values are driven on the data bus (D0 – D15). (The MEVB reset data<br>circuit is open drain; a high state is provided via a pull-up resistor.) Each<br>reset data line may be set high (H) or low (L). Consult the appropriate<br>MCU user's manual, data book, or technical summary for reset data<br>information. |  |

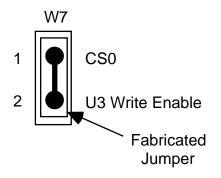

| W7<br>U3 Data RAM               | 1<br>2                                                  | Jumper installed (factory default); CS0 is used as the write enable for the device in the data RAM socket U3.                                                                                                                                                                                                                                                                                                                                                        |  |

| Write Enable                    |                                                         | No jumper; CS0 is not used as the write enable for the device in socket U3.<br>You must connect an alternate signal to pin 2 of jumper header W7 or you<br>can not write to the device in the data RAM socket U3.                                                                                                                                                                                                                                                    |  |

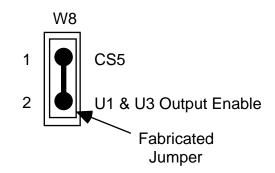

| W8<br>Data RAM                  | 1<br>2                                                  | Jumper installed (factory default); CS5 is used as the output enable for the devices in the data RAM sockets (U1 & U3).                                                                                                                                                                                                                                                                                                                                              |  |

| Output Enable                   |                                                         | No jumper; CS5 is not used as the output enable for the device in sockets U1 and U3. You must connect an alternate signal to pin 2 of jumper header W8 or you can not read the devices in the data RAM sockets.                                                                                                                                                                                                                                                      |  |

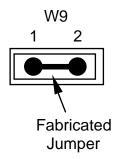

| W9<br>J10, J11                  | 12                                                      | Jumper installed (factory default); +5-volt power appears on pin 1 of logic analyzer connectors J10 and J11.                                                                                                                                                                                                                                                                                                                                                         |  |

| +5Vdc<br>Selection              |                                                         | No jumper; no signal on pin 1 of logic analyzer connectors J10 and J11.                                                                                                                                                                                                                                                                                                                                                                                              |  |

| W10<br>Pseudo ROM               | 1 <b>●●</b> 2<br>3 <b>●●</b> 4                          | Jumper installed on pins 1 and 2 (factory default); RAM is installed in the pseudo ROM sockets (U2 & U4).                                                                                                                                                                                                                                                                                                                                                            |  |

| Memory Type                     | 5 6                                                     | Jumper installed on pins 3 and 4; EPROM is installed in the pseudo ROM sockets.                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                                 |                                                         | Jumper installed on pins 5 and 6; flash EEPROM is installed in the pseudo ROM sockets.                                                                                                                                                                                                                                                                                                                                                                               |  |

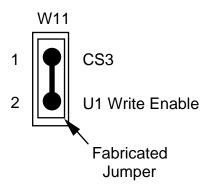

| W11<br>U1 Data RAM              | 1<br>2                                                  | Jumper installed (factory default); CS3 is used as the write enable for the device in the data RAM socket U1.                                                                                                                                                                                                                                                                                                                                                        |  |

| Write Enable                    |                                                         | No jumper; CS3 is not used as the write enable for the device in socket U1.<br>You must connect an alternate signal to pin 2 of jumper header W11 or you<br>can not write to the device in the data RAM socket U1.                                                                                                                                                                                                                                                   |  |

Table 2-2. MPFB Jumper Header Descriptions (continued)

| Jumper<br>Header                              | Туре                                                                                                                                          | Description                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| W12<br>Pseudo ROM                             | $\begin{array}{c}1\\3\\5\end{array} \bigoplus \begin{array}{c}\bullet\bullet\\\bullet\bullet\end{array} = \begin{array}{c}2\\4\\6\end{array}$ | Jumper installed on pins 1 and 2 (factory default); 32K x 8 devices are installed in the pseudo ROM sockets (U2 & U4).                                                                                                                                                                                                                        |

| Memory Size                                   | 7 ●● 8<br>9 ●● 10                                                                                                                             | Jumper installed on pins 3 and 4; 64K x 8 devices are installed in the pseudo ROM sockets.                                                                                                                                                                                                                                                    |

|                                               |                                                                                                                                               | Jumper installed on pins 5 and 6; 128K x 8 devices are installed in the pseudo ROM sockets.                                                                                                                                                                                                                                                   |

|                                               |                                                                                                                                               | Jumper installed on pins 7 and 8; 256K x 8 devices are installed in the pseudo ROM sockets.                                                                                                                                                                                                                                                   |

|                                               |                                                                                                                                               | Jumper installed on pins 9 and 10; 512K x 8 devices are installed in the pseudo ROM sockets.                                                                                                                                                                                                                                                  |

| W13<br>VPP to MCU                             | 1<br>2                                                                                                                                        | Jumper installed (factory default); connects +12Vdc power (as controlled by S1) to the MCU programming voltage pin(s).                                                                                                                                                                                                                        |

| Selection                                     |                                                                                                                                               | No jumper; +5Vdc power is applied to the MCU programming voltage pin(s) and the +12Vdc power is disconnected.                                                                                                                                                                                                                                 |

| W14<br>Pseudo ROM/<br>Fast RAM<br>Chip Select | 123<br>••••<br>•••                                                                                                                            | Jumper header W14 selects the MCU signal for the memory devices in the fast RAM sockets (U9 & U10) and pseudo ROM sockets (U2 & U4). Pins 1 and 2 select the MCU chip select for the memory devices in the fast RAM sockets. While pins 2 and 3 of jumper header W14 select the chip select for the memory devices in the pseudo ROM sockets. |

|                                               |                                                                                                                                               | Jumper installed on CSBOOT pins 2 and 3 (factory default); use CSBOOT as the memory device chip enable for memory devices in the pseudo ROM sockets.                                                                                                                                                                                          |

|                                               |                                                                                                                                               | Jumper installed on CS1/CSM pins 1 and 2 (factory default); use CS1/CSM as the memory device chip select for the fast RAM sockets.                                                                                                                                                                                                            |

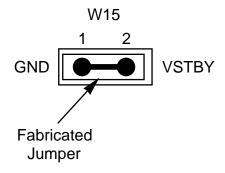

| W15<br>VSTBY                                  | 12                                                                                                                                            | Jumper installed (factory default); voltage standby (VSTBY) is connected to ground. No battery backup for the MCU internal RAM.                                                                                                                                                                                                               |

| Selection                                     |                                                                                                                                               | No jumper installed and an external power source connect to pin 2; battery backup for the internal RAM in the MPB on-board MCU device.                                                                                                                                                                                                        |

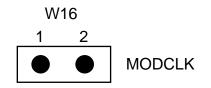

| W16<br>MODCLK                                 | 12<br>••                                                                                                                                      | No jumper installed (factory default); the MCU MODCLK signal is pulled high (logic 1) via a resistor during reset.                                                                                                                                                                                                                            |

| Selection                                     |                                                                                                                                               | Jumper installed; the MCU MODCLK signal is driven low (logic 0) during reset.                                                                                                                                                                                                                                                                 |

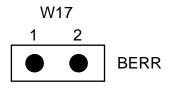

| W17<br>BERR                                   | 12<br>••                                                                                                                                      | No jumper installed (factory default); the BERR signal is pulled high (logic 1) via a resistor during reset.                                                                                                                                                                                                                                  |

| Selection                                     |                                                                                                                                               | Jumper installed; the BERR signal is driven low (logic 0) during reset.                                                                                                                                                                                                                                                                       |

| Jumper<br>Header                 | Туре                                                                          | Description                                                                                                                                                                                                                    |

|----------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| W18<br>Pseudo ROM                | 123<br>•••                                                                    | Jumper installed on pins 1 and 2 (factory default); unrestricted writes to the memory devices in the pseudo ROM sockets (U2 & U4).                                                                                             |

| Write<br>Protection              |                                                                               | Jumper installed on pins 2 and 3; allows writing to the memory devices in the pseudo ROM sockets only in background debug mode.                                                                                                |

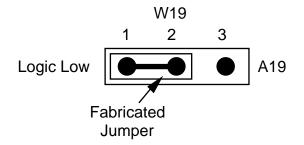

| W19<br>A19<br>Disconnect         | 123<br>•••                                                                    | Jumper installed on pins 1 and 2 (factory default); disconnects the MCU A19 pin from the MPFB memory array, pseudo ROM sockets (U2 & U4), and data RAM sockets (U1 & U3) and drives the memory array's A19 pin to a logic low. |

|                                  |                                                                               | Jumper installed on pins 2 and 3; connects the A19 signal to the MPFB memory arrays.                                                                                                                                           |

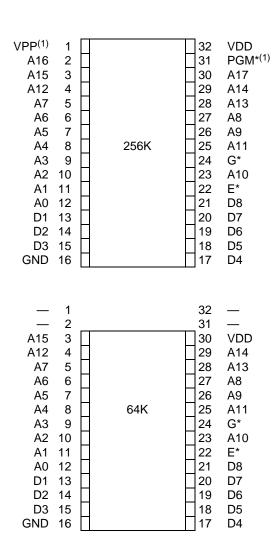

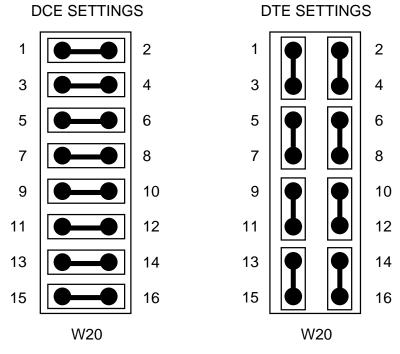

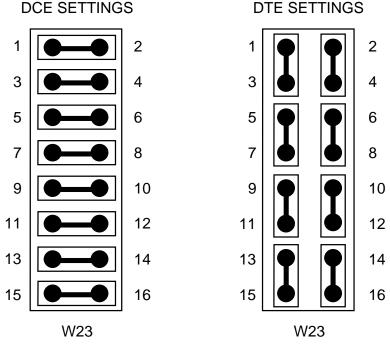

| W20<br>RS-232 Port 1<br>Protocol | 1 2 4<br>3 4 6<br>7 8 8<br>9 0 0 12<br>13 0 0 12<br>14 16                     | Jumper header W20 configures RS-232 port 1 (J21) protocol as DTE or DCE. The factory configuration (shown) is the fabricated jumpers positioned for DCE protocol.                                                              |

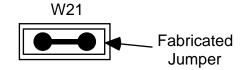

| W21<br>J13 +5Vdc                 | 12                                                                            | Jumper installed (factory default); +5-volt power appears on pin 1 of logic analyzer connector J13.                                                                                                                            |

| Selection                        |                                                                               | No jumper; no signal on pin 1 of logic analyzer connector J13.                                                                                                                                                                 |

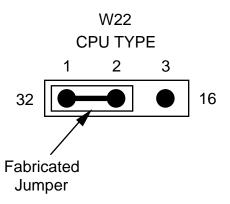

| W22<br>MCU Type                  | 123<br>••••                                                                   | Jumper installed on pins 1 and 2 (factory default); selects the emulation MCU (on the MPB) as an M68300 MCU device.                                                                                                            |

| Selection                        |                                                                               | Jumper installed on pins 2 and 3; selects the emulation MCU (on the MPB) as an M68HC16 MCU device.                                                                                                                             |

| W23<br>RS-232 Port 2<br>Protocol | Port 2 3 6 6 DCE. The factory configuration (shown) is the fabricated jumpers |                                                                                                                                                                                                                                |

#### 2.2.1 J10, J11 +5 Volt Select Header (W9)

Jumper header W9 selects or de-selects +5Vdc power to pin 1 of logic analyzer connectors J10 and J11. The drawing below shows the factory configuration: the fabricated jumper connecting +5Vdc power to pin 1 of J10 and J11. If you do not want this functionality, remove the fabricated jumper.

#### 2.2.2 Voltage Standby Select Header (W15)

Jumper header W15 connects voltage standby (VSTBY) to ground when battery backup for RAM in the MCU device is not available. The drawing below shows the factory configuration: the fabricated jumper grounds the voltage standby pin on the MCU. To apply backup power to VSTBY, remove the fabricated jumper and connect the external power source to pin 2 and external power ground to pin 1.

#### 2.2.3 MODCLK Select Header (W16)

Jumper header W16 lets the MPFB pull down the MCU's MODCLK pin during reset. This is an MCU configuration option and specific to each MCU. Because MCU MODCLK usage varies with each device, refer to the MCU user's manual for a description of the MODCLK signal. The factory configuration (shown below) is no fabricated jumper in W16. When no fabricated jumper is installed the MODCLK pin is pulled high by a resistor on the MPFB.

#### CAUTION

When allowing the MPFB to drive MODCLK low during reset (W16 installed), make sure your circuits in the wire-wrap area are not driving the MODCLK pin at J14 pin 4. This may damage the MPFB or your circuit.

#### 2.2.4 BERR Select Header (W17)

Jumper header W17 lets the MPFB pull down the MCU's BERR pin during reset. This is an MCU configuration option. The factory configuration (shown below) is no fabricated jumper in W17. When no fabricated jumper is installed the BERR pin is pulled high by a resistor on the MPFB.

#### CAUTION

The MPFB must have all memory devices removed from their sockets and the PRU set to OFF (a jumper on W5 pins 1 and 2). This function is for final evaluation of an MCU with internal ROM/EEPROM.

#### 2.2.5 J13 +5 Volt Select Header (W21)

Jumper header W21 selects or de-selects +5Vdc power to pin 1 of logic analyzer connector J13. The drawing below shows the factory configuration: the fabricated jumper connecting +5Vdc power to pin 1 of J13. If you do not want this functionality, remove the fabricated jumper.

#### 2.2.6 MCU Type Select Header (W22)

Jumper header W22 configures the MPFB for the MPB type installed on the MPFB. The factory setting, a jumper on pins 1 and 2, indicates that an M68300 MPB is installed on the MPFB. If your MPB has an M68HC16 MCU move the jumper to pins 2 and 3.

#### NOTE

Jumper header W22 does not inhibit MEVB operation, it tells the pipe de-muxing programmable array logic (PAL) chip which CPU type is installed. The PAL creates the latched DSO and DSI (LAT-DSO and LAT-DSI) signals on J12. The LAT-DSO and LAT-DSI signals are used by the logic analyzer to perform disassembly. If you are not using a logic analyzer, W22 setting is inconsequential.

#### 2.2.7 MPFB LED Descriptions

There are four LEDs on the MPFB. Their functions are:

- DS1 POWER: ON = power is applied to the MPFB.

- DS2 ERROR: ON = an error has occurred in the memory configuration jumper settings or E1 is low. Check jumper headers W10 and W12 against memory in the pseudo ROM sockets (U2 & U4). Refer to paragraph 2.2.8 and for information on configuring memory refer to Chapter 3.

- DS3 VPP: ON = program voltage is available for programming MCU flash EEPROM or memory devices in the pseudo ROM sockets (U2 & U4).

- DS4 RUN: ON = MEVB is running user code (in foreground); OFF = MEVB is running in background debug mode or reset is low.

#### 2.2.8 DS2 Control Insertion Point (E1)

The LED at location DS2 is controlled by the output of the PAL (location U7). DS2 turns ON if the memory configuration jumpers are set incorrectly. You may also wire an external circuit to E1 and use DS2 as a visual indicator for your program. DS2 turns on when E1 is driven low. Connect E1 to any output signal. Driving insertion point E1 low does not effect the MCU RESET signal.

# 2.3 INSTALLATION INSTRUCTIONS

The MEVB is designed for table-top operation. A user-supplied power supply and host computer are required. The host computer must have a parallel port and must run MS-DOS, as required by ICD16 or ICD32. The following paragraphs explain MPFB connections.

#### **2.3.1 Power Supply – MPFB Connection**

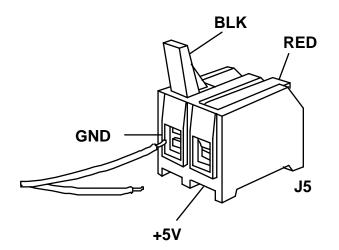

Use MPFB connector J5 to connect a user-supplied power supply to the MEVB. Contact 1 is ground; black lever. Contact 2 is VDD (+5 volts); red lever. Use 20 or 22 AWG wire for power connections. For each wire, trim back the insulation 1/4 in. (.635 cm), lift the appropriate lever of J5 to release tension on the contacts, then insert the bare wire into J5 and close the lever. The MEVB requires a +5Vdc @ 1.0 amp power supply for operation. A 1.5 amp fuse is installed on the MPFB +5Vdc power supply input line.

#### CAUTIONS

Do not use wire larger than 20 AWG in connector J5. Such wire could damage the connector.

Turn off MEVB power when installing or removing the MPB from the MPFB. Sudden power surges could damage MEVB integrated circuits.

#### **2.3.2 Personal Computer – BDM Connection (J6)**

As the MEVB does not have on-board debug firmware, debugging does not consume MCU resources. Motorola ships the MEVB with the ICD16 or ICD32 debug monitor, which easily connects to the MPFB's standard background-mode header (connector J6). For additional information about the ICD software, including debugging and assembly information, see either the ICD16 or ICD32 user's manual. Alternately, any debugger which uses the 10-pin BDM interface may be used with the MEVB.

#### CAUTIONS

Turn off MEVB power when connecting or disconnecting the BDM cable. Sudden power surges could damage MEVB integrated circuits.

Connect the ICD16 or ICD32 debugger to the MEVB by connecting the integral 10-pin cable assembly of the debugger to MPFB connector J6. **Make sure that the red wire of the cable connects to pin 1 of connector J6.** Connect the DB-25 parallel port of the ICD16 or ICD32 to the parallel port of your computer. The drawing below shows signal assignments for connector J6; for pin assignments and signal descriptions, refer to Chapter 7.

For a complete description of PC to MPFB interconnection (via the BDM connector), refer to the ICD16 or ICD32 user manual.

#### 2.3.3 RESET Switch (S2)

Push-button switch (S2) resets the MEVB. A reset initializes the MEVB to its startup point. The reset switch is located in the lower left-hand corner of the MPFB. To manually reset your system press S2 to trip the switch.

The MPFB provides a single reset signal. Thus the system, MPFB and MCU, can be reset from the following sources:

- S2, manual reset switch, as described above

- Low voltage detection IC, U12B or U12A (SMT footprint)

- ICD16 or ICD32 software command via the BDM connector (J6)

- Logic analyzer connector J14 pin 6

- Incorrect memory configuration on W10 or W12

- MCU, i.e., watchdog ...etc.

#### 2.3.4 Logic Analyzer Connections (J7 – J20)

Use connectors J7 through J20 to connect the logic analyzer to the circuit being evaluated. For signal descriptions, refer to Chapter 7 and to the appropriate MPB user's manual.

The MPFB has extra holes next to connectors J7 through J20 that give you space for 10-pin Berg-type strips (shown below). To use such strips, install them on the *bottom* of the board, and solder the pins on the top. Wire wrap from the bottom of the MPFB to the user-wire-wrap area. Be sure to put standoffs in the corner mounting holes to protect the wire wrapping on the bottom of the MPFB.

# 2.4 STARTING EVALUATION ACTIVITIES

When you have configured MPFB and MPB jumpers (refer to the MPB user's manual for MPB configuration instructions), and made cable connections, your MEVB is ready to use. To start assembly or debugging activities, follow the instructions of the ICD16 or ICD32 user's manual.

A typical startup is:

- 1. Install MPB on the MPFB as per instructions in the MPB user's manual.

- 2. Install MCU overlay over the logic analyzer connectors (J12 through J20).

- 3. Install ICD ribbon cable to J6 of the MPFB.

- 4. Connect parallel port cable to ICD DB-25 connector.

- 5. Connect +5Vdc power supply to connector J5.

- 6. Install ICD software on your personal computer (follow the instructions in the ICD user's manual).

- 7. Turn on the +5Vdc power supply

- 8. Check that the DS1 LED is on (marked PWR). If LED does not illuminate then:

- +5 volt power is not connected or supply is not on

- Input power is reversed (+5Vdc on GND and GND on +5V).

- Fuse is blown.

Execute ICD software

|    | ICD16 Software                                             |  |  |  |

|----|------------------------------------------------------------|--|--|--|

| 1. | Enter: ICD16 and a carriage return ( <cr>)</cr>            |  |  |  |

| 2. | Enter: <cr> to bring up debugger screen</cr>               |  |  |  |

| 3. | Wait for debugger prompt then                              |  |  |  |

| 4. | Enter: A=55 <cr></cr>                                      |  |  |  |

| 5. | Check window for Register A<br>Register A should equal 55. |  |  |  |

|    | ICD32 Software                                               |

|----|--------------------------------------------------------------|

| 1. | Enter: ICD32 <cr></cr>                                       |

| 2. | Enter: <cr> to bring up debugger screen</cr>                 |

| 3. | Wait for debugger prompt then                                |

| 4. | Enter: D0=55 <cr></cr>                                       |

| 5. | Check window for Register D0<br>Register D0 should equal 55. |

|    |                                                              |

If register does not change:

- 1. Check parallel port connections good cable connections and proper cable type. and that the correct PC parallel port selected, i.e., LPT1, LPT2 or LPT3.

- 2. MPB is not seated on the MPFB MAPI connectors (J1, J2, J3, and J4).

- 3. MPB Clock Select Header installed incorrectly or no oscillator in socket. Verify MPB input clock by measuring CLOCKOUT wave form on logic analyzer connector J12 or J13.

- 4. If the reset signal at J14 remains low:

- Wrong crystal frequency, and the VCO can not lock.

- Power at J5 is less than or equal to 4.5 volts and has tripped the low voltage detection IC.

- Your circuit may be holding reset low.

- Incorrect memory configuration on W10 or W12 (DS2 is ON).

- 5. MCU device is not seated properly in the socket on the MPB.

# CHAPTER 3

## **MEMORY CONFIGURATION**

# 3.1 INTRODUCTION

This chapter provides information for configuring memory in the expansion sockets U1, U2, U3, U4, U9, and U10.

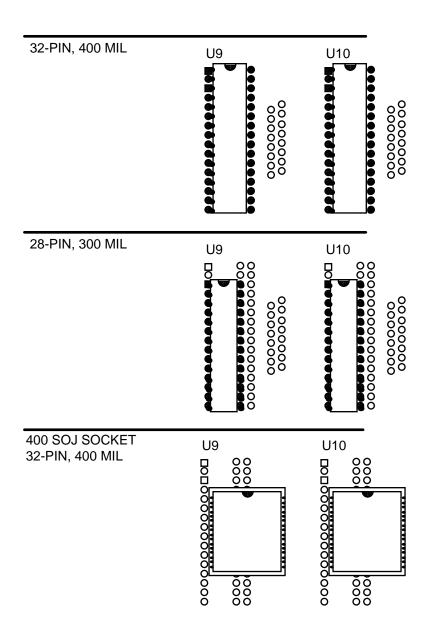

There are six memory device sockets on the MPFB; two data RAM sockets (U1 & U3), two pseudo ROM sockets (U2 & U4), and two fast RAM sockets (U9 & U10). Figure 3-1 is a diagram of the MPFB memory sockets. The open design structure of the MPFB lets you configure and use each memory socket to fit your system requirements. A brief overview of each memory type (data RAM, pseudo ROM, and fast RAM) is given below. For more detailed information refer to the appropriate paragraph within this chapter.

The data RAM sockets accept either 32K x 8, 128K x 8, or 512K x 8 static RAM devices. The data RAM sockets allow evaluation of MCU chip select functions. Each data RAM device is connected to a unique MCU chip select for write enable generation. While the output enable (read enable) of each data RAM device is connected to a common MCU chip select. This memory is connected directly to the MCU without any MPFB device delays. This is ideal for fast termination (2 clock cycle) memory cycle evaluations.

The pseudo ROM sockets provide a generic memory socket, and accepts a variety of RAM, EPROM, or EEPROM devices. The size of these devices range from 32K x 8 to 512K x 8 bytes. A programmable array logic (PAL) chip on the MPFB controls the signal configuration to the pseudo ROM sockets. This PAL creates a delay on some memory signals and may require faster memory or a wait state to the memory cycle. These full featured sockets allow easy evaluation of many memory types with the use of a single MCU chip select.

The fast RAM sockets provide emulation for internal ROM memory operating at the maximum speed. Most MCU-internal ROM can be accessed with fast termination. The signal delay created by the PAL may inhibit the usage of the pseudo ROM sockets for ROM code emulation. Therefore the fast RAM sockets are directly connected to the MCU to provide the fastest possible access times. RAM accesses are controlled with a single chip select. If you choose to use the fast RAM sockets as general purpose RAM, please read the caution in paragraph 3.2.3. The fast RAM sockets accept either 32K x 8 or 128K x 8 fast static RAM devices. This provides emulation for ROM modules as large as 512K bytes.

The MPFB also provides a physical bus structure for implementing both byte memory ports (8bits at a time on the data bus) or word memory ports (16-bits at a time on the data bus) for the data RAM or pseudo ROM. The fast RAM sockets only provide a word memory port. The factory supplies 64K bytes of RAM in the pseudo ROM sockets.

# 3.2 MEMORY CONFIGURATION

Before modifying MPFB memory setup, it is important to understand the port concepts. Since all memory sockets are designed for MCU chip select usage, you should be familiar with the operation and setup of each MCU chip select you intend to connect to the memories.

The following port discussion relates only to the data RAM and pseudo ROM memory sockets. The MPFB provides a method for connecting a single memory to the MCU. This memory operates as a byte port. When accessed by an instruction requesting a byte, it provides the data byte. When accessed by an instruction requesting a word, the memory provides the data word via two byte memory cycles. The design of the MCU specifies that all byte port memory operations occur on the most significant byte of the data bus, D8-D15. Therefore the MPFB implements sockets for the MSB of the data RAM and pseudo ROM memory. The sockets provide the physical interface for the byte and word ports.

When using the memory sockets as a word port, the MCU does not need to provide address A0 to memory. The address signal A0 is not needed for word ports since data is accessed in words. For example, on a byte read of a word port, the memory provides the MCU with a word of data. Internally, the MCU uses only the LSB or MSB to complete the operation. With a byte write, the data byte is placed on both the MSB and LSB of the data bus. If MCU chip selects are used, such as the data RAM area, the MCU chip select that controls the RAM's write enable determines which memory is written. These MCU chip selects must be configured as an upper write-only on a word port or lower write-only on a word port. When using a single chip select, such as the pseudo ROM area, the external MCU control signals must be decoded to determine the memory cycle type. Without this decoding, such as the fast RAM area, the MCU would write a word of data to memory during a byte write operation. The memory PAL provides the memory cycle decoding; LSB enable, and MSB enable functions for the pseudo ROM sockets.

When using a single MSB memory socket as a byte port, the MCU must provide the memory with address A0. This is required since each sequential memory access, MSB and LSB data, is provided by the same memory device. The dual sockets provide an easy method of connecting each memory to the address bus. The word sockets (right shifted) connect MCU address A1 to the memory's A0 address input and A2 to A1, etc. The byte sockets (left shifted) connect MCU address A0 to the memory's A0 address input and A1 to A1, etc. As you can see, reconnecting eighteen address signals to each of the MSB memories would be a sizable and messy jumper array.

It is usually easiest to envision the dual sockets as word port socket overlaid on a byte port socket. The confusion is greatly increased since the MPFB provides sockets for 300 mil and 600 mil memory devices. Each memory section below includes pictorial diagrams to help you with memory placements.

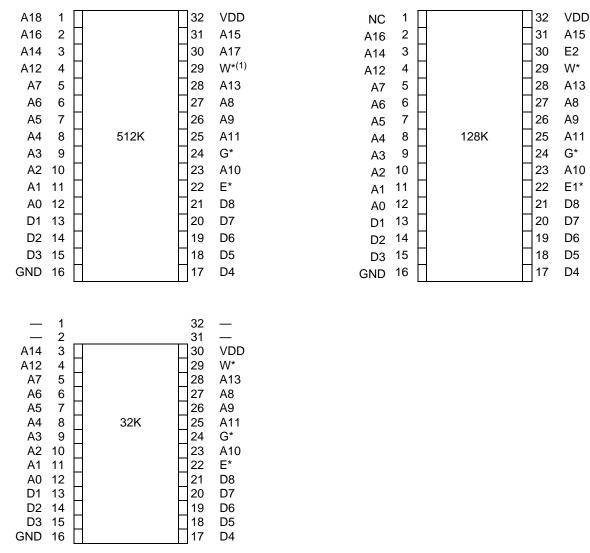

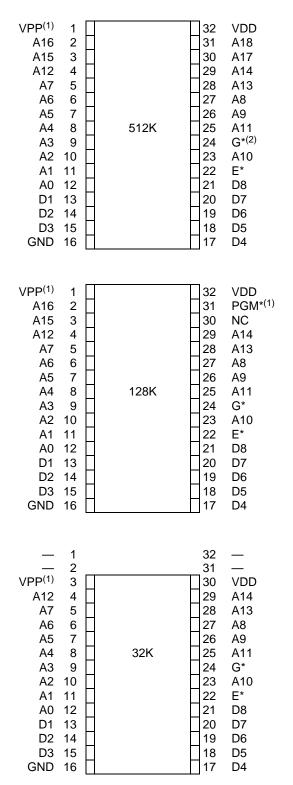

When installing memory devices in the on-board memory sockets, each matching pair of devices (U1 & U3, U2 & U4, and U9 & U10) must be functionally identical. This implies that you cannot place a RAM in the MSB socket and an EPROM in the LSB socket. It is also recommended that you keep the MSB and LSB the same memory size. If the MSB and LSB memory differs in size, such as an 64K x 8 EPROM and 128K x 8 EPROM, you must evaluate each memory pin-out for possible MPFB conflicts and damage. Refer to Figures 3-5 through 3-7 for memory pin-outs used by the MPFB.

Before attempting memory modifications to the MPFB, scan the paragraph relating to the specific memory sockets you plan to modify. These paragraphs provide detailed information relating to each memory interface.

Figure 3-1. Memory Socket Diagram

#### **3.2.1 Data RAM Configuration (U1 and U3)**

Data RAM refers to memory locations U1 & U3. These sockets are intended for static RAM devices. The data RAM sockets accept  $32K \ge 8$ ,  $128K \ge 8$ , or  $512K \ge 8$  static RAM devices (refer to Figure 3-5 for package pin-outs). The data RAM sockets support two package widths: either 300 mil or 600 mil wide DIP devices, and two package sizes: either 28- or 32-pin packages.

The data RAM sockets allow evaluation of the MCU chip select functions. Each data RAM device is connected to a unique MCU chip select for write enable generation. While the output enable (read enable) of each data RAM device is connected to a common MCU chip select. This memory is directly connected to the MCU without any MPFB device delays. This is ideal for fast termination (2 clock cycle) memory cycle evaluations.

The three MCU chip selects for the data RAM sockets are connected to the memory via jumper headers W7, W8, and W11. These jumper headers connect the default MCU chip select signals, CS0, CS3, and CS5 to the data RAM devices. Alternately, you may connect different MCU chip select signals via these jumper headers (refer to paragraphs 3.2.1.2 through 3.2.1.4 for definitions of these jumper headers).

Data RAM can be configured as a byte memory port (8-bits at a time on the data bus) or a word memory port (16-bits at a time on the data bus). For a word port, place the RAMs into sockets U1 and U3B. For a byte port, a RAM should be placed in socket U3A. When configured as a byte port, the RAM in U1 is unused by the MCU (removal of the device in location U1 is not required). Figure 3-2 illustrates memory device positioning within the data RAM sockets.

Once your software configures the connected MCU chip selects, memory can be accessed with byte, word, or long word memory cycles for both the word and byte port configurations. The examples in Table 3-1 provide MCU chip select configuration for byte and word port memory operation. The example uses the default MCU chip selects, CS0, CS3, and CS5, for data RAM operation.

#### NOTES

Memory data bus structure may be either byte or word in length. Byte or word bus structure is configured by positioning the memory devices in the proper socket area (refer to Figure 3-2).

The memory configurations shown in Figure 3-2 are only four of the possible methods for configuring memory in sockets U1 & U3.

You must configure jumper headers W1, W7, W8, W11, and W19 for correct data RAM operation. Paragraphs 3.2.1.1 through 3.2.1.5 give detailed descriptions of the jumper header settings for devices in the data RAM sockets.

Figure 3-2. Data RAM Device Configuration

Table 3-1 is a summary of valid configurations for RAM devices at locations U1 & U3. Table 3-1 shows the relationships of chip selects CS3, CS0, and CS5 to the BYTE and R/W fields of the corresponding chip select option registers. This table also shows data bus size setting for chip select pin assignment register 0. Refer to the descriptions of jumper headers W7, W8, and W11 (paragraphs 3.2.1.2, 3.2.1.3, and 3.2.1.4) for information on connecting the MCU chip selects CS0, CS5, and CS3 to the data RAM sockets.

| PART I: 16-Bit Data Bus Size, RAMS in U1 and U3B        |                          |                               |  |

|---------------------------------------------------------|--------------------------|-------------------------------|--|

| CS3<br>(U1 Write Enable)                                | CS0<br>(U3 Write Enable) | CS5<br>(U1, U3 Output Enable) |  |

| CSOR3 BYTE: lower                                       | CSOR0 BYTE: upper        | CSOR5 BYTE: both              |  |

| CSOR3 R/W: write only                                   | CSOR0 R/W: write only    | CSOR5 R/W: read only          |  |

| CSPAR0: 16-bit port                                     | CSPAR0: 16-bit port      | CSPAR0: 16-bit port           |  |

| PART II: 8-Bit Data Bus Size, RAM in U3A <sup>(2)</sup> |                          |                               |  |

| CS3<br>(U1 Write Enable)                                | CS0<br>(U3 Write Enable) | CS5<br>(U1, U3 Output Enable) |  |

| CSOR3 BYTE: disable <sup>(3)</sup>                      | CSOR0 BYTE: X            | CSOR5 BYTE: X                 |  |

| CSOR3 R/W: write only                                   | CSOR0 R/W: write only    | CSOR5 R/W: read only          |  |

| CSPAR0: 16-bit port                                     | CSPAR0: 8-bit port       | CSPAR0: 8-bit port            |  |

#### Table 3-1. Valid MPFB U1, U3 Memory Configurations<sup>(1)</sup>

1. KEY:

*CSORx BYTE* is the BYTE field of the chip select option register for CSx.

CSORx R/W is the R/W (read/write) field of the chip select option register for CSx.

CSPAR0 is chip select pin assignment register 0.

X means *don't care* internally to the MCU.

- 2. The MCU does not use a device at U1: the socket must be empty or contain an identical device to the one at U3 (word mode).

- 3. If no device is in the U1 socket or no jumper on jumper header W11 pins 1 and 2, you may use the CS3 pin in the wire-wrap area; otherwise, you must disable the field.

#### 3.2.1.1 Data RAM Memory Size Select Header (W1)

Jumper header W1 configures the MPFB for the size of memory devices in the data RAM sockets (U1 & U3). The factory setting is for 32K x 8 or 128K x 8 devices. The alternate setting is for 512K x 8 devices. W1 connects device power and address signals for the appropriate device. A jumper set in the wrong position could cause a RAM VDD pin to be connected to an MCU address line causing incorrect operation.

#### NOTE

Both jumpers of this header must have the same setting: both between pins 1 and 3; 2 and 4, or both between pins 3 and 5; 4 and 6.

#### **3.2.1.2** Data RAM Write Enable Select Header (W7)

Jumper header W7 selects or de-selects CS0 as the write enable for the memory device in the data RAM socket located at U3. The drawing below shows the factory configuration: the fabricated jumper selects CS0. If you do not want this functionality, remove the fabricated jumper and connect an alternate chip select to W7 pin-2. Removing W7 without connecting an alternate chip select provides write protection for memory at location U3.

#### 3.2.1.3 Data RAM Output Enable Select Header (W8)

Jumper header W8 selects or de-selects CS5 as the output enable for the memory devices in the data RAM sockets located at U1 and U3. The drawing below shows the factory configuration: the fabricated jumper selects CS5. If you do not want this functionality, remove the fabricated jumper and connect an alternate chip select to W8 pin-2. Removing W8 without connecting an alternate chip select inhibits memory read operations for memory at locations U1 & U3.

#### **3.2.1.4 Data RAM Write Enable Select Header (W11)**

Jumper header W11 selects or de-selects CS3 as the write enable for the memory device in the data RAM socket located at U1. The drawing below shows the factory configuration: the fabricated jumper selects CS3. If you do not want this functionality, remove the fabricated jumper and connect an alternate chip select to W11 pin-2. Removing W11 without connecting an alternate chip select provides write protection for memory at location U1.

#### 3.2.1.5 A19 Disconnect Select Header (W19)

Jumper header W19 lets you disconnect the A19 signal from the MEVB data RAM sockets (U1 & U3) and pseudo ROM (U2 & U4). This jumper option lets you evaluate the MCU's A19 pin with its alternate functions (CS6 or PC3) and maintain proper memory operation. The factory setting (jumper on pins 1 and 2) disconnects the MCU's A19 pin from the memory array and forces low the memory array's A19 signal (pull-down on W19 pin-1). When using 512K x 8 memory devices in a word port configuration (512K x 16) and W19 is set on pins 1 and 2; the amount of accessible memory is limited to 128K x 16. Alternately, you can wire-wrap another port signal to W19 pin-2, then toggle the port pin as a memory bank select to regain memory accessibility. All other memory sizes and port configurations are not effected by W19 or the MCU's A19 operation (they do not use the A19 signal).

The alternate setting, the jumper on pins 2 and 3, connects the MCU's A19 signal to the pseudo ROM and data RAM sockets. In this setting, 512K x 16 memory operation (data RAM and pseudo ROM) may not function properly if the MCU's A19 pin is set to its alternate functions (CS6 or PC3).

#### 3.2.2 Pseudo ROM Configuration (U2 and U4)

Pseudo ROM refers to memory locations U2 & U4. The two pseudo ROM sockets provide a generic memory socket, and accepts a variety of RAM, EPROM, or EEPROM devices. Refer to Figures 3-5 through 3-7 for each device pin-out supported. Pseudo ROM sockets may contain:

- RAM 32K x 8, 128K x 8, or 512K x 8

- EPROM 32K x 8, 64K x 8, 128K x 8, 256K x 8, or 512K x 8

- EEPROM 32K x 8, 64K x 8, 128K x 8, 256K x 8, or 512K x 8

The pseudo ROM sockets accept memory devices of two widths: either 300 mil or 600 mil DIP devices, and two package sizes: either 28- or 32-pin packages.

The pseudo ROM sockets provide an interface for a variety of memory types. The memory in the pseudo ROM sockets are controlled by the memory controller PAL at location U7. The MCU supplies a single chip signal as the pseudo ROM interface. The jumper W14 lets you select any MCU chip select signals to connect to the pseudo ROM sockets. The PAL provides several automated functions; memory device signal routing, write protection, and byte or word cycle decoding. The PAL also introduces a 15 (max.) nanosecond delay in several MCU address and control signals. This delay may require insertion of an extra wait state within the memory cycle.

Pseudo ROM can be configured as a byte memory port (8-bits at a time on the data bus) or a word memory port (16-bits at a time on the data bus). For a word port, memory should be placed in sockets U2 and U4B and set the port size via jumper header W4. For a byte port, memory should be placed in socket U4A and set the port size via jumper header W4. While configured as a byte port, the memory in U2 is unused by the MCU (removal of the device in location U2 is not required). Figure 3-3 illustrates memory device positioning in the pseudo ROM sockets. The pseudo ROM port size configuration is determined by the jumper setting of W4 (see Table 3-2).

| W4<br>Setting | Pseudo ROM<br>Port Width | U2<br>Memory Access <sup>1</sup>             | U4A<br>Memory Access <sup>1</sup>                | U4B<br>Memory Access <sup>1</sup>            |

|---------------|--------------------------|----------------------------------------------|--------------------------------------------------|----------------------------------------------|

| 16            | Word - 16 Bit            | All reads,<br>Word writes<br>LSB byte writes | Use U4B socket                                   | All reads,<br>Word writes<br>MSB byte writes |

| 8             | Byte - 8 Bit             | De-selected by PAL                           | All reads,<br>All word writes<br>All byte writes | Use U4A socket                               |

Table 3-2.

W4 Pseudo ROM Port Size Configuration

1) Qualified by a valid MCU chip select.

The simplest function the memory PAL provides is device signal routing. Each memory type (RAM, EPROM, and EEPROM) has unique device pin-outs. The PAL connects the proper signal for the device type and size selected. For 28-pin devices, jumper header W3 connects the power pin (pin-28) to the MPFB +5Vdc supply. For 32-pin devices, W3 connects the proper PAL interconnect signal to the memory device. The PAL also provides a write protection method for pseudo ROM devices. When enabled by W18, the PAL de-selects the pseudo ROM devices during all non-background mode write cycles. This lets the debugger software modify the pseudo ROM devices in background mode, i.e. loading programs, modify memory commands, etc. When your program begins execution, memory is write protected and appears as if ROM devices were installed in the pseudo ROM sockets (U2 & U4). The write protect feature is implemented for both RAM and EEPROM memory devices.

As described above, the pseudo ROM devices are selected by a single MCU chip select. When the devices are configured as a word port (16-bit), bus cycle decoding is required. During a byte write cycle, only one memory must be enabled. Otherwise a byte write will corrupt the memory contents by writing 16-bits on the data bus. The PAL uses the MCU's R/W, A0 and SIZ0 signals to determine the cycle type. It then enables or disables the proper MSB and LSB memory device(s) for each qualified memory cycle.

### NOTES

There is a 15 nanosecond (max.) delay on memory control signals and some address lines for devices in the pseudo ROM sockets. Please determine MCU wait states accordingly.

Memory data bus structure may be either byte or word in length. Byte or word bus structure is configured by positioning the memory devices in the proper socket area (refer to Figure 3-3).

The memory configurations shown in Figure 3-3 are only four of the possible methods for configuring memory in sockets U2 & U4.

Flash EEPROM devices in the pseudo ROM sockets may be programmed by setting the appropriate jumper headers. Jumper header W2 connects the programming voltage from the DC-DC converter to pin-1 of the pseudo ROM sockets (refer to paragraphs on S1 (5.2.2), W2 (3.2.2.1), VPP generation description (5.2)). You must provide the MCU programming algorithm code for the specific EEPROM device. The write protect jumper (W18) may also be used to inhibit flash EEPROM programming.

Jumper headers W2, W3, W4, W10, W12, W14, W18, and W19 effect pseudo ROM operation and need to be set appropriately. Paragraphs 3.2.2.1 through 3.2.2.8 give detailed descriptions of the jumper header settings for devices in the pseudo ROM sockets.

| WORD CONFIGURATION,<br>32-PIN, 600 MIL |        | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 |                                             | •                                       |                                         | U3 <b>D0D</b> 00000000000000000000000000000000   | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 |                                            |

|----------------------------------------|--------|-----------------------------------------|-----------------------------------------|---------------------------------------------|-----------------------------------------|-----------------------------------------|--------------------------------------------------|-----------------------------------------|-----------------------------------------|--------------------------------------------|

| BYTE CONFIGURATION,<br>28-PIN, 600 MIL |        | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | U2<br>□0□0000000000000000000000000000000000 | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | U3 <b>D0</b> 00000000000000000000000000000000000 | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 |                                            |

| WORD CONFIGURATION,<br>28-PIN, 300 MIL | U1<br> | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 |                                             |                                         | 000000000000000000000000000000000000000 | U3<br>000000000000000000000000000000000000       | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | U4                                         |

| BYTE CONFIGURATION,<br>32-PIN, 300 MIL |        | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | U2<br>                                      | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | U3                                               | 000000000000000000000000000000000000000 |                                         | U4<br>000000000000000000000000000000000000 |

Figure 3-3. Pseudo ROM Device Configuration

## 3.2.2.1 Pseudo ROM Pin 1 Select Header (W2)

Jumper header W2 configures the signal for pin-1 of a 32-pin memory devices in the pseudo ROM sockets (U2 & U4). (28-pin devices installed in U2 & U4 are not affected by the setting of W2.) The drawing below shows the factory configuration: the fabricated jumper between pins 1 and 2. With the jumper between pins 1 and 2, pin-1 of the pseudo ROM sockets is a standard address line. The alternate configuration (jumper between pins 2 and 3) connects VPP to pin-1 of the pseudo ROM sockets and lets you program flash EEPROM memory devices. To activate VPP, switch S1 must be set to ON (refer to paragraph 5.2.2). If S1 is OFF and W13 is installed, +5Vdc appears on W2 pin-3. If S1 is OFF and W13 has no jumper installed, then W2 pin-3 floats.

### 3.2.2.2 Pseudo ROM Package Size Select Header (W3)